D触发器的应用

- 触发器(59899)

相关推荐

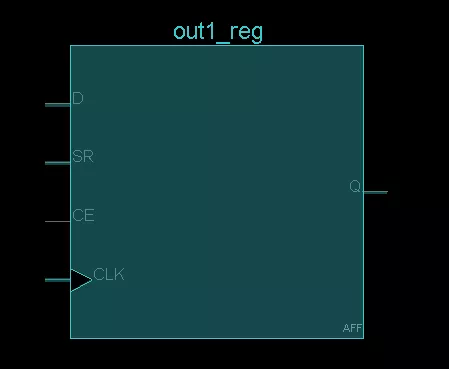

D触发器与Latch锁存器电路设计

D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 234

234

234

234

D触发器的类型详解 同步复位和异步复位D触发器讲解

的存储单元,具有时钟同步的特性。其中,D触发器是数字电路设计中使用最广泛的一种触发器类型之一,因为它具有简单、稳定和多功能等优点。

2023-08-31 10:50:19 1436

1436

1436

1436

D触发器组成音频信号发生器

D触发器组成音频信号发生器 D触发器是一种数字逻辑电路元件,它是由若干个逻辑门组成的,常用于数字系统中的寄存器、计数器等。D触发器在数字系统中起到很重要的作用,它能够存储和传输数字信号,并且能

2023-08-24 15:50:29 160

160

160

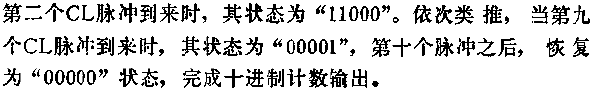

160用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器?

用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器? 序列发生器是数字电子技术中常用的电路模块之一,它可以用来生成一系列的数字信号序列。在数字电路中,D触发器是一种被广泛使用的数字逻辑组件

2023-08-24 15:50:17 549

549

549

549D触发器与亚稳态的那些事

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-07-25 10:45:39 274

274

274

274

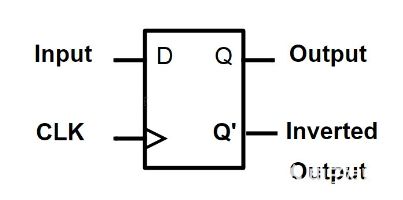

什么是D触发器,D触发器如何工作的?

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 5258

5258

5258

5258

FPGA设计的D触发器与亚稳态

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-05-12 16:37:31 975

975

975

975

使用LTspice仿真D触发器的串并输入功能

最近在用LTspice仿真D触发器的一个串并输入功能,只有第一个触发器的波形跟理论分析一致,其他剩余的就是怎么也不行。 经过资料查找,和不停地尝试,最终还是找出了原因。 确实每一个工具还是有其特点的,跟实际的芯片还是有差异。

2023-01-19 17:28:00 1872

1872

1872

1872

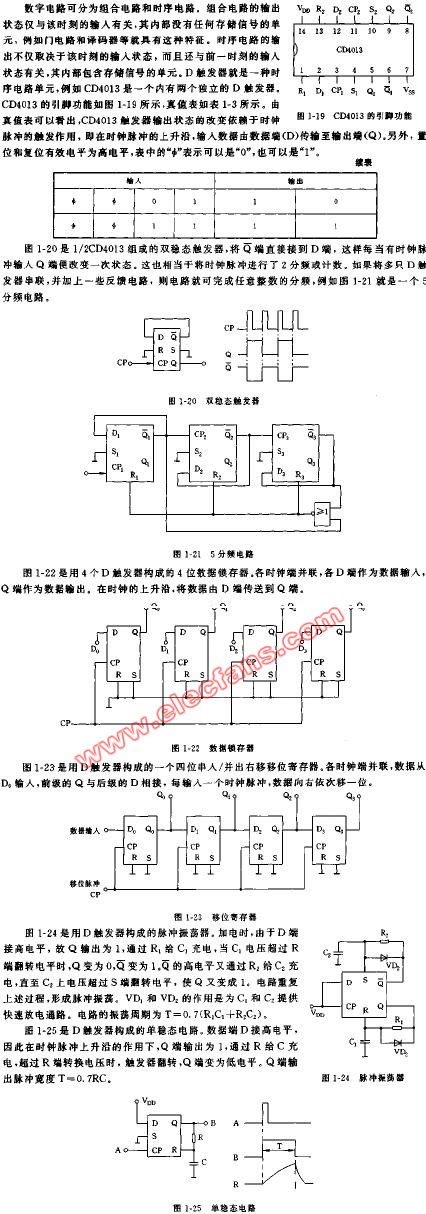

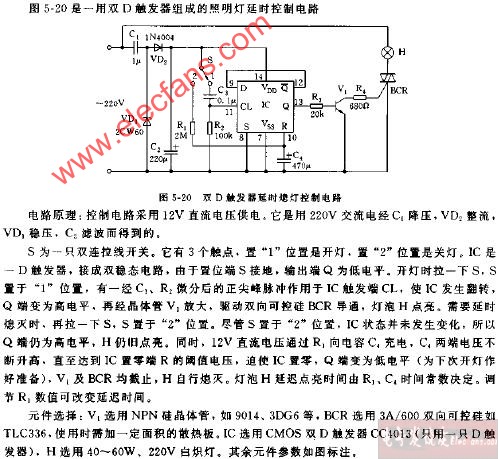

D触发器不同应用下的电路图详解

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

2023-01-06 14:19:46 1874

1874

1874

1874D触发器的结构特点、工作原理及主要应用

D触发器也称为“延迟触发器”或“数据触发器”,主要用于存储1位二进制数据,是数字电子产品中广泛使用的触发器之一。除了作为数字系统中的基本存储元件外,D触发器也被视为延迟线元件和零阶保持元件。

2022-10-11 17:21:02 97371

97371

97371

97371

时序约束系列之D触发器原理和FPGA时序结构

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 2327

2327

2327

2327

D触发器为什么能对数据延迟一个时钟周期

D触发器在FPGA里用得很多,但我经常无法理解D触发器为什么能对数据延迟一个时钟周期(打一拍)。下面从信号处理的角度来谈一下我的理解。如发现理解有误,烦请留言指正。

2022-06-17 16:56:19 4177

4177

4177

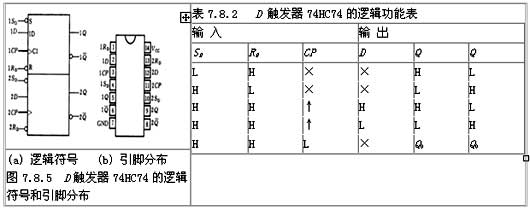

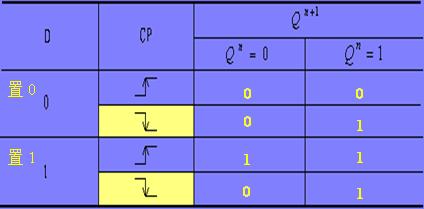

417774ls74双d触发器引脚图 74ls74双D触发器功能测试

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )复位输入( )、时钟输入(CP)和数据输出(Q)。 的低电平使输出预置或清除,而与其它输入端的电平无关。当

2021-06-04 15:40:41 63776

63776

63776

63776

D触发器:结构及时序介绍

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

2019-12-02 07:06:00 6002

6002

6002

6002

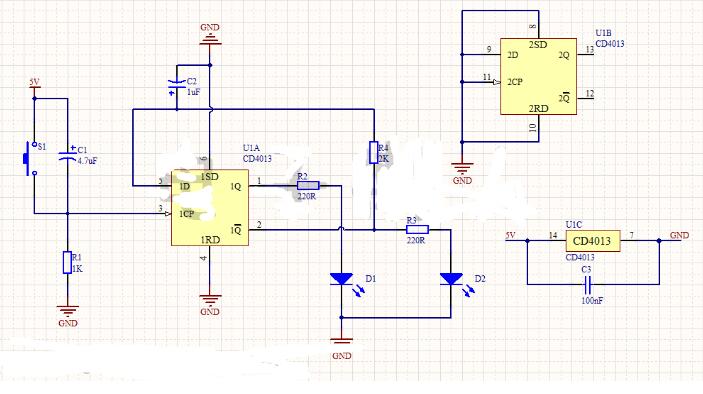

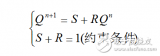

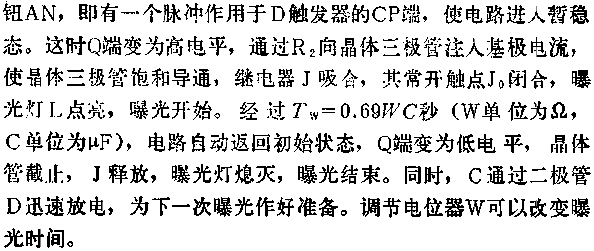

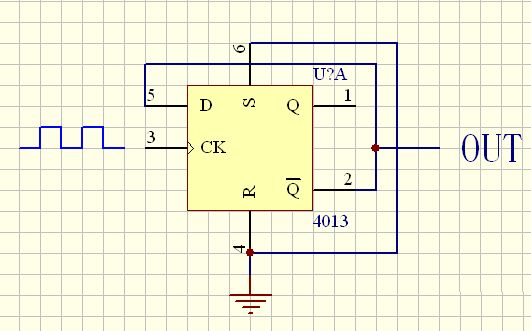

D触发器模拟按钮自锁开关电路工作过程分析

所谓自锁开关就是按一下,开关接通并保持接通状态;再按一下,开关解锁复位到初始状态。本例通过D触发器而设计的电子自锁开关,当每按一下电路中的轻触按键S1时,都可以使D触发器翻转一次,同时利用CD4013的特性,按键松开后电路仍然保持自锁状态。

2019-10-01 11:03:00 16749

16749

16749

16749

D触发器基本原理

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

2019-07-12 08:50:36 94674

94674

94674

94674

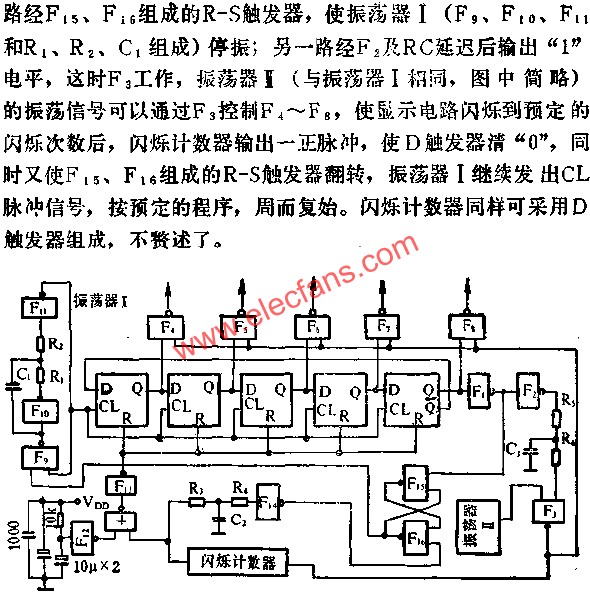

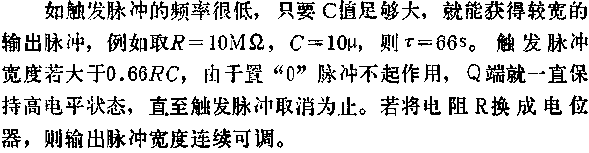

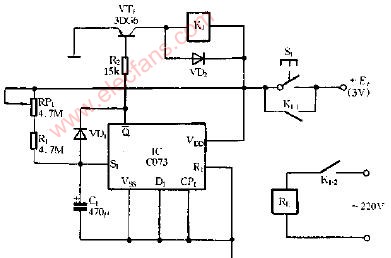

双D触发器式的VCO

关键词:D触发器 , VCO 如图所示为双D触发器式的VCO。电路输出一个占空比50%的方波信号,而消耗的电流却很小。当输入电压为5~12V时,输出频率范围从20~70kHz。首先假设IC-A的初始

2018-10-08 09:27:01 140

140

140

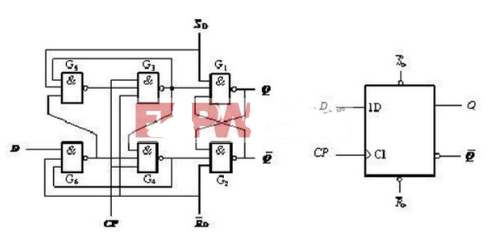

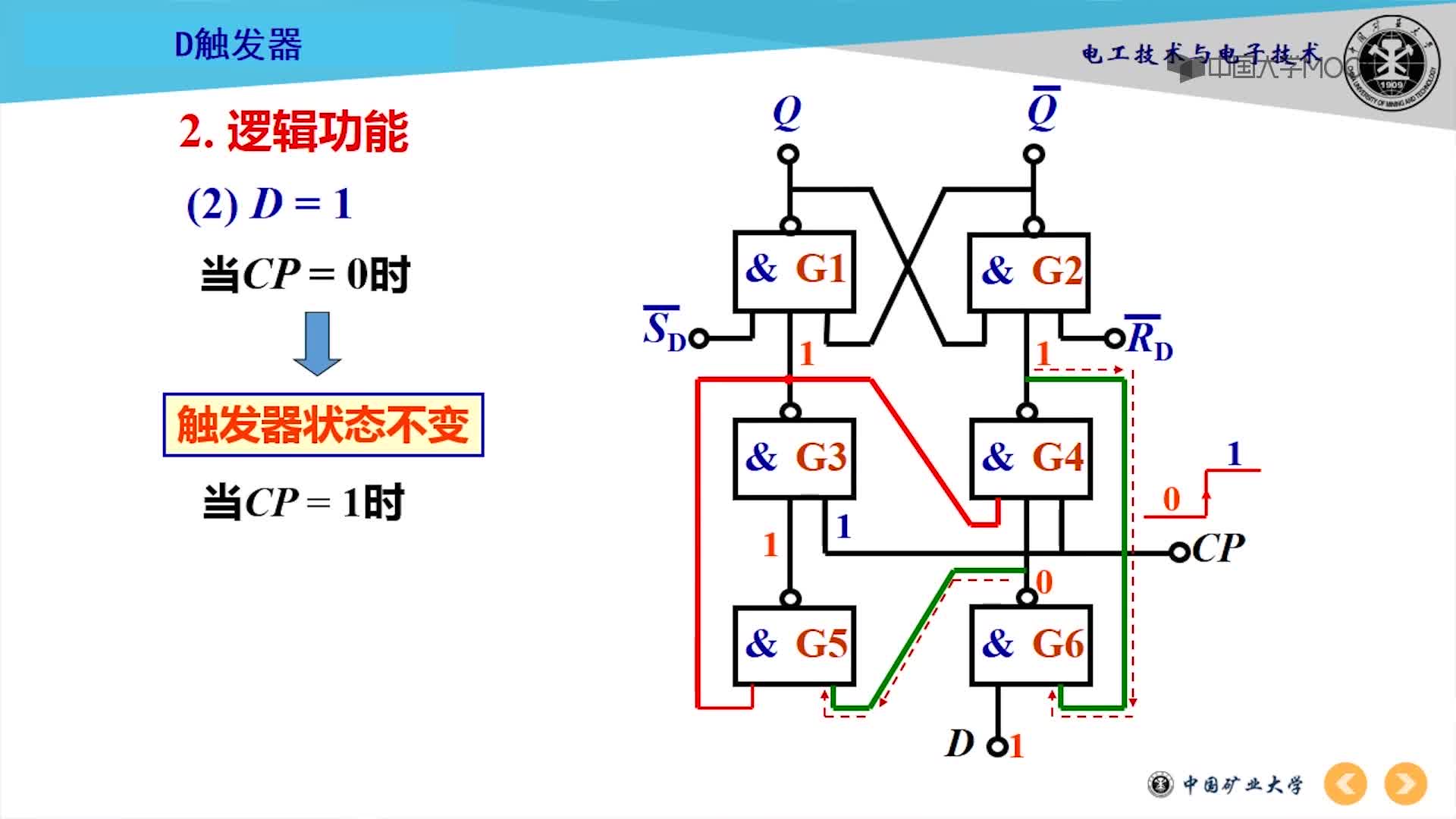

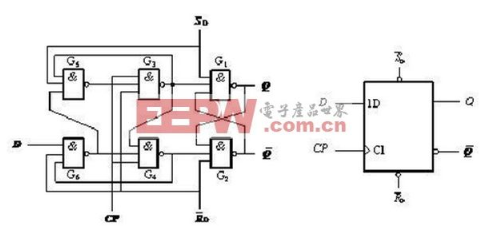

140d触发器的特性方程

D触发器(data flip-flop或delay flip-flop)由6个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

2017-11-02 09:59:08 95590

95590

95590

95590

D触发器的H-Spice仿真

用一对互补的输入信号送入RS 触发器,就得到单输入的 D 触发器。由于D 触发器有一对互补信号接至RS 触发器的 输入端,所以它避免了RS 输入端同时为1 的不允许工作状 态。D 触发器通常用来暂时存储一个比特的信息或用作时延 器件。当CLOCK=1 时,触发器能把输

2011-03-09 16:20:01 92

92

92

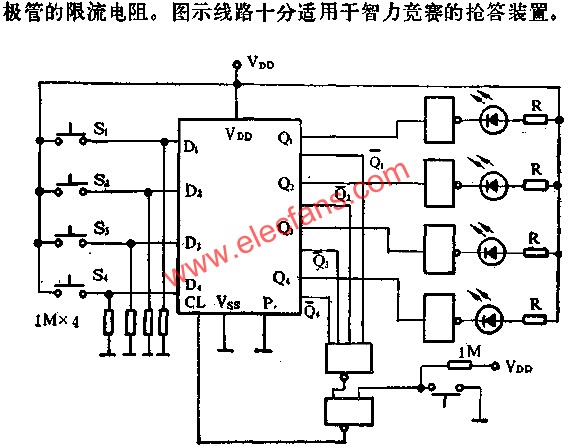

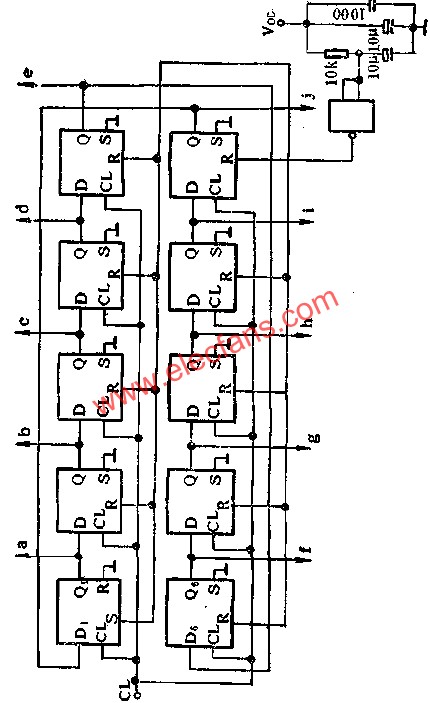

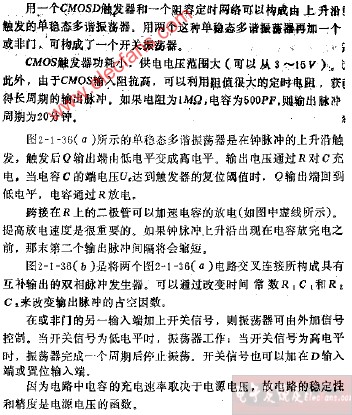

92基于CMOS双D触发器CD4013的脉冲宽度检测电路设计

D触发器的常规使用一般是用作二分频器、计数器或移位寄存器。然而,只要对D触发器的外围电路加以改进,根据其基本逻辑功能。就可充分发挥其独特的作用。数

2010-12-29 11:44:46 2899

2899

2899

2899

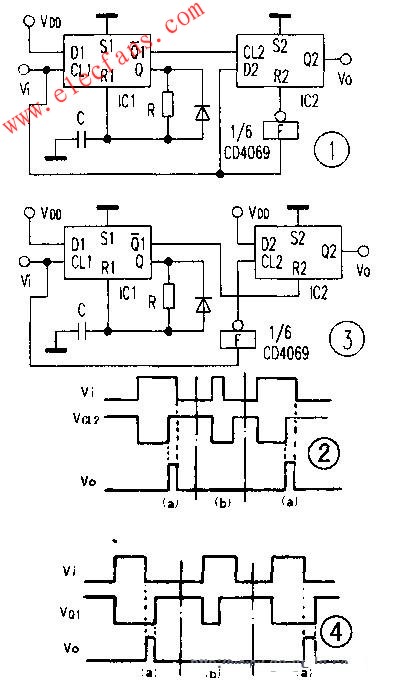

D触发器加“许可”信号电路图

从D触发器的真值表可知,当时钟脉冲CL="1"时,数据输入端D的状态会被“置放”入触发器中去,而与触发器原状无关。如果当时钟冲CL="1",D端状态不旋转放入

2010-09-21 01:27:59 577

577

577

577

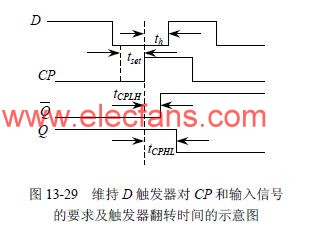

维持阻塞D触发器的脉冲工作特性和动态参数

根据前面分析可知,维持阻塞D触发器的工作分两个阶段,在CP=0时,为准备阶段;CP由0向1正向跳变时刻为状态转移阶段。为了使维持阻塞D触发器(见图13-22)能可靠

2010-08-23 09:31:03 4526

4526

4526

4526

基于钟控神经MOS 管的多值双边沿D触发器设计

摘 要:通过对钟控神经MOS 管特性和冗余抑制技术的研究,提出了一种新型多值双边沿D 触发器的设计方案.该方案利用钟控神经MOS 管多输入栅加权信号控制、浮栅上的电容耦合

2010-08-12 16:06:26 17

17

17

17D触发器工作原理是什么?

D触发器工作原理是什么?

边沿D 触发器:

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出

2010-03-08 13:56:50 68940

68940

68940

68940

D触发器/J-K触发器的功能测试及其应用

D触发器的功能测试74LS74型双D触发器芯片引脚图,D触发器功能测试的引脚连线图,D触发器功能测试的引脚连线图,用D触发器构成二进制计数器,用D触发器构成四位移位寄存器

J-K

2009-02-14 15:27:51 290

290

290

290cd4013双d触发器电路图

cd4013双d触发器

CD4013双D触发器做的脉冲4分频器应用

-----------------------------. ┌─────

2008-01-09 23:48:45 4487

4487

4487

4487D触发器原理图和真值表以及波形图分析

D触发器边沿D 触发器: 负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边

2007-09-11 23:13:22 173406

173406

173406

173406

电子发烧友App

电子发烧友App

评论