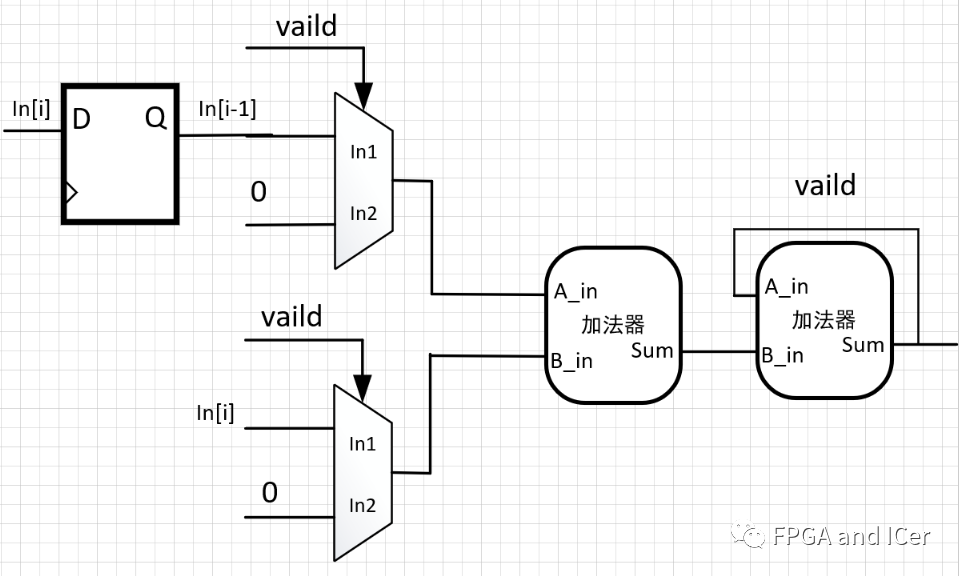

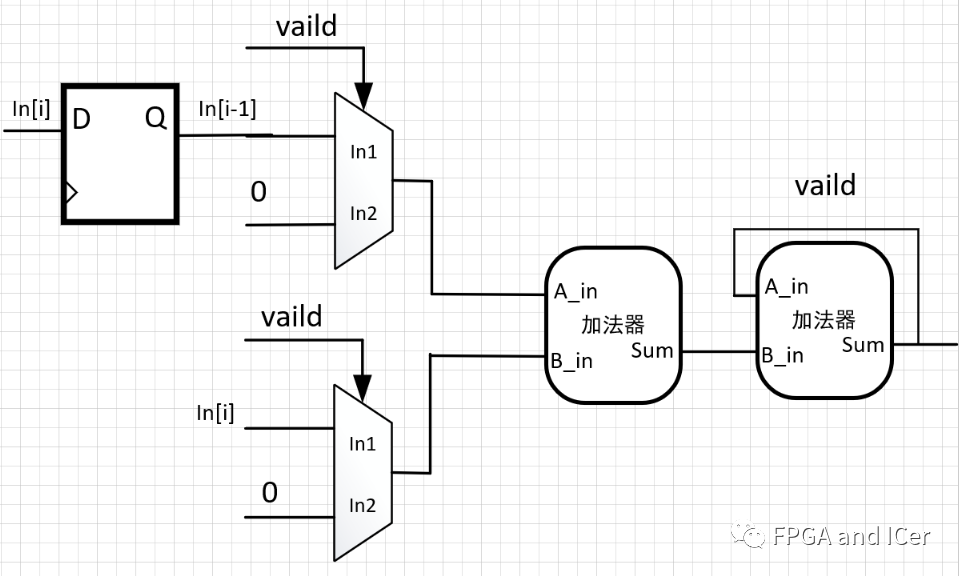

实现累加器的加法器例化的个数。按照原文大佬的设计方法,因为数据连续且加法器的延迟周期是2,使用使用一个实现累加,会有一半的数据丢失。

2023-06-02 16:35:40 1029

1029

模式下高达12 GSPS。高动态范围和带宽使这些DAC非常适合最严苛的高速射频(RF) DAC应用。DDS由一组32个32位数控振荡器(NCO)组成,各带相位累加器

2023-03-10 16:10:39

此DDS器件是一款数控振荡器,在单个CMOS芯片内集成了一个相位累加器、一个SINE查找表以及一个10位数模转换器,提供相位调制和频率调制两种调制能力。 最高支持25 MHz时钟速率。频率

2023-03-09 16:40:21

此DDS器件是一款数控振荡器,在单个CMOS芯片内集成了一个相位累加器、一个正弦查找表以及一个10位数模转换器,提供相位调制和频率调制两种调制能力。 最高支持50 MHz时钟速率。频率

2023-02-15 09:43:52

AD9832是一款数控振荡器,在单个CMOS芯片内集成了一个相位累加器、一个正弦查找表以及一个10位数模转换器(DAC),提供相位调制和频率调制两种调制能力。 最高支持25 MHz时钟速率

2023-02-15 09:41:06

AD9835是一款数控振荡器,在单个CMOS芯片内集成了一个相位累加器、一个COS查找表以及一个10位数模转换器,提供相位调制和频率调制两种调制能力。 最高支持50 MHz时钟速率。频率

2023-02-15 09:38:09

模式下高达12 GSPS。高动态范围和带宽使这些DAC非常适合最严苛的高速射频(RF) DAC应用。DDS由一组32个32位数控振荡器(NCO)组成,各带相位累加器

2023-02-14 15:24:06

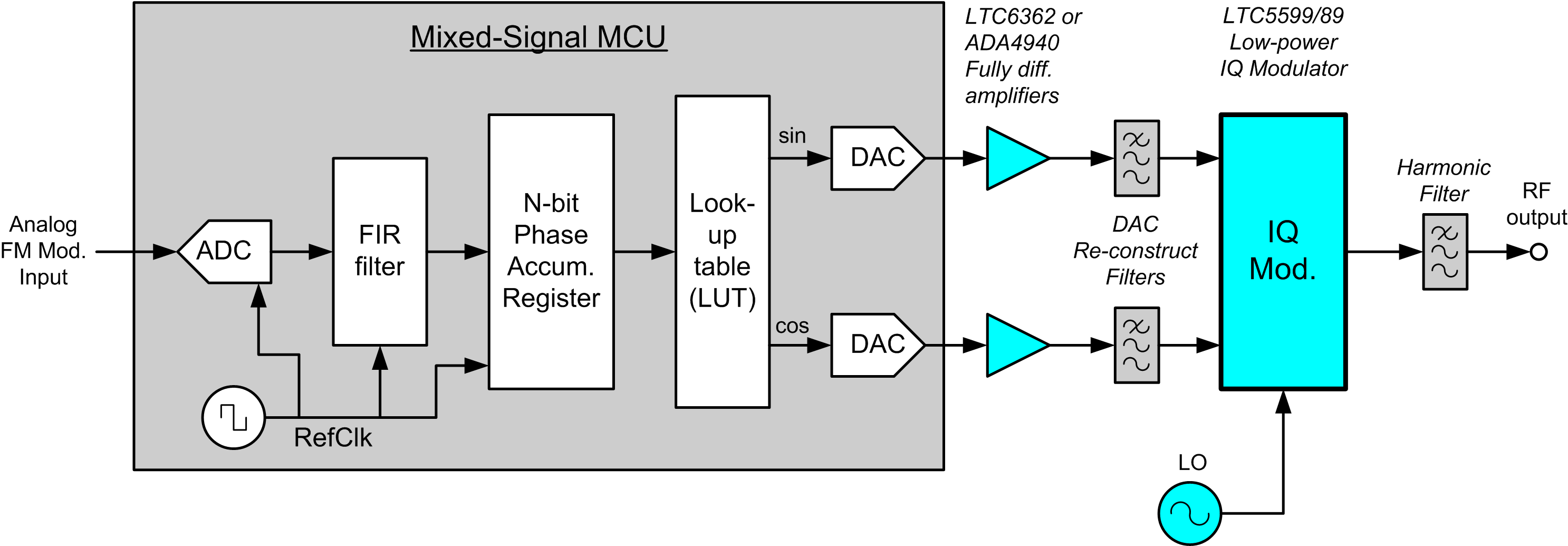

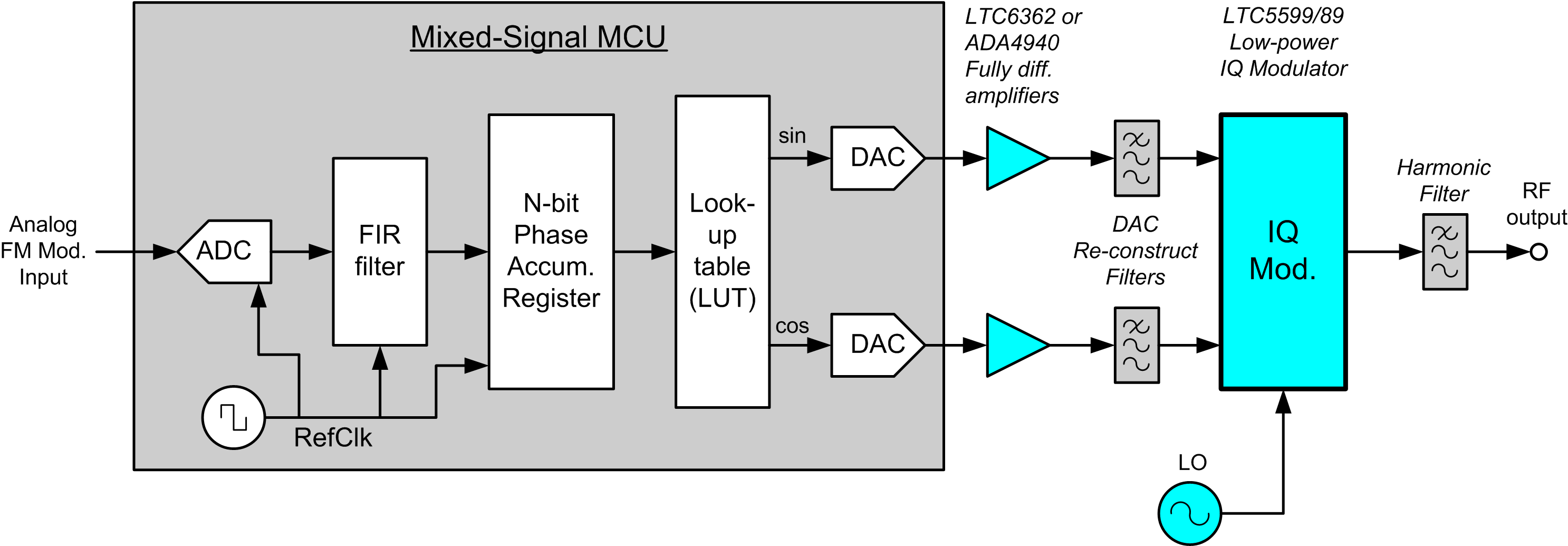

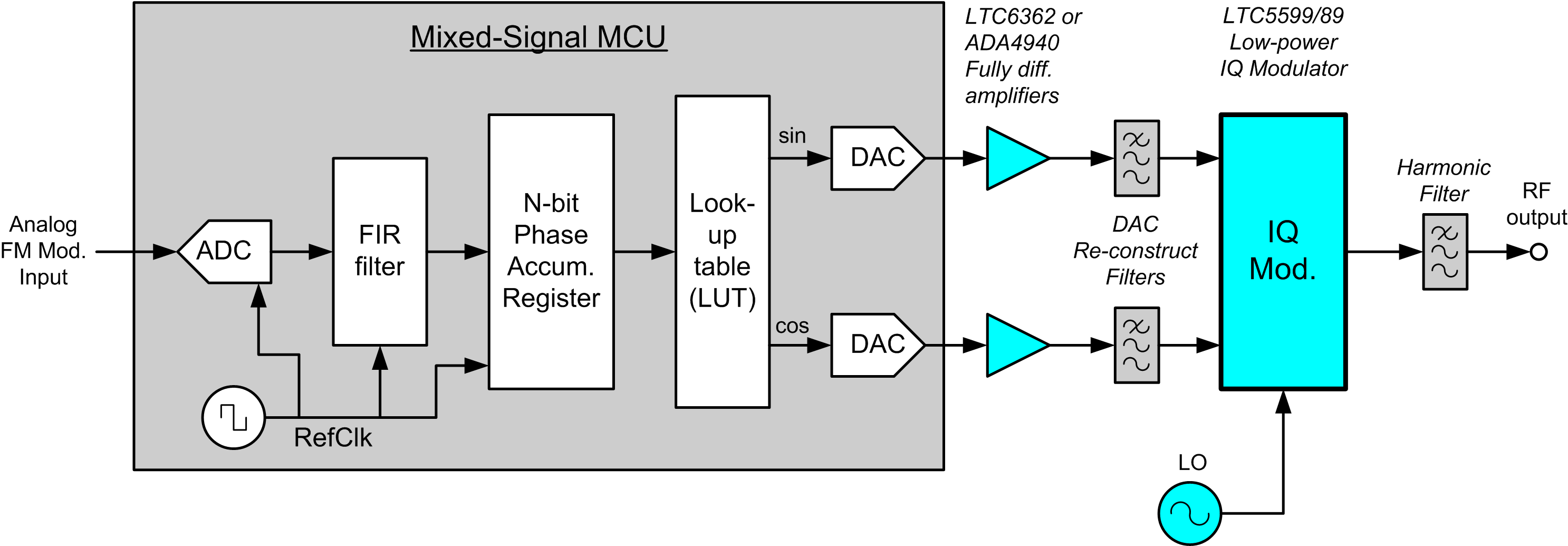

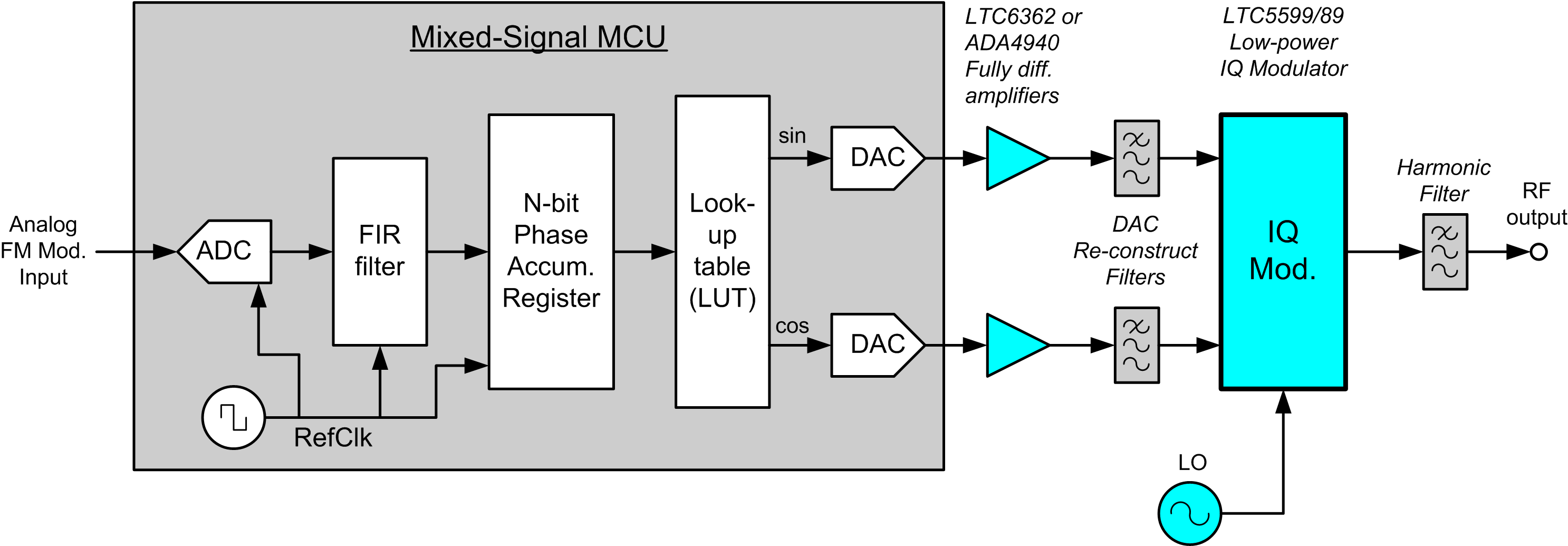

在为通信应用生成模拟或数字FM时,IQ调制器可提供多功能的低功耗解决方案。示例设计将展示如何使用混合信号MCU执行相位累加器和正弦/余弦查找表功能。证明了 IQ 调制器精度和线性度的重要性。

2023-01-03 14:20:06 855

855

相位累加器寄存器的输出代表生成波形的当前相位。由于相位到正弦或相位到余弦映射器引擎,每个离散累加器输出相位值随后被转换为幅度正弦或余弦数据或样本。

2022-07-24 16:51:14 935

935

本设计相位累加器设定为32位,正弦表数据为8位,因此在ROM查找表里的容量为232×8=34,359,738,368(bits),在理论上这可以获得精细的频率分辨率,但是这么大容量的数据却很难实现。

2022-06-21 10:54:35 5249

5249

相位累加器寄存器的输出代表生成波形的当前相位。由于相位到正弦或相位到余弦映射器引擎,每个离散累加器输出相位值随后被转换为幅度正弦或余弦数据或样本。

2022-06-06 14:58:19 1024

1024

精细的频率调节。采用这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形。一个完整周期的函数波形被存储在上面所示的存储器查找表中。相位累加器跟踪输出函数的电流相位。为了输出一个非常低的频率,采样样本之间的差相位(Δ)将非常小。例

2021-12-02 18:51:18 28

28 累加器A与ACC区别累加器写成A或ACC在51汇编语言指令中是有区别的。ACC在汇编后的机器码必有一个字节的操作数,即累加器的字节地址E0H,A在汇编后则隐含在指令操作码中。所以在指令中A不能

2021-11-23 09:06:01 98

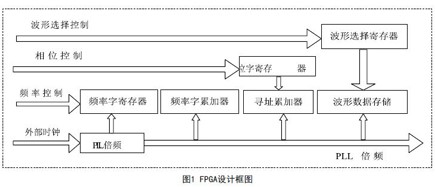

98 可编程逻辑器件设计环境,其功能更为强大。用Max+plusII设计DDS系统数字部分最简单的方法是采用原理图输入。相位累加器调用lmp_add_sub加减法器模拟,相位累加器的好坏将直接影响到整个系统

2011-07-13 14:13:56

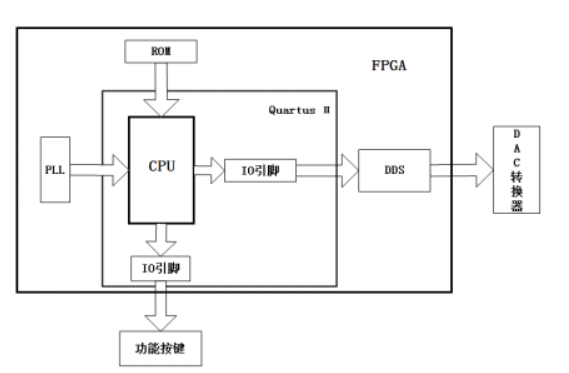

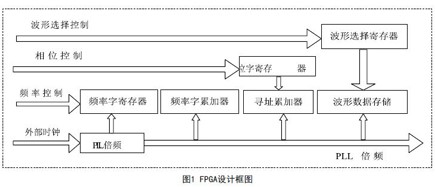

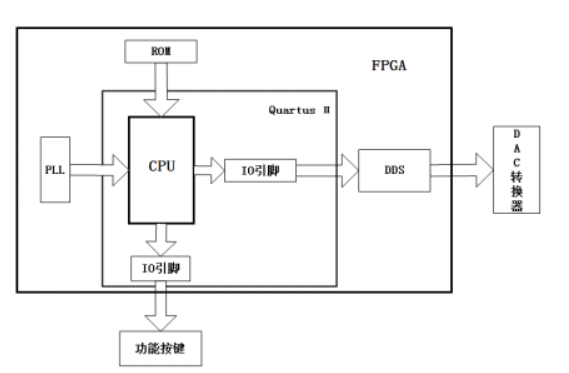

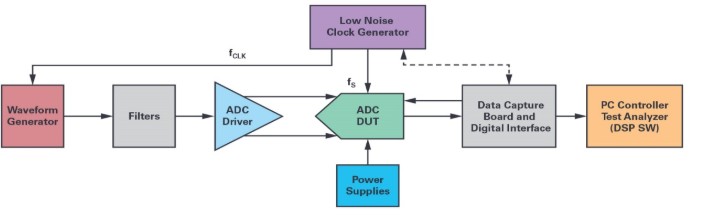

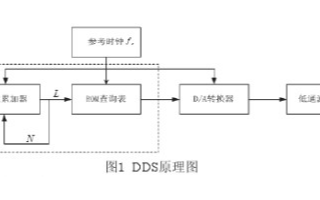

正弦信号产生采用DDS技术,以FGPA方式实现,DDS的基本结构由参考时钟、相位累加器、存储器(ROM)、DAC和滤波器(LPF)组成,其组成如图2所示。

2021-05-20 10:20:40 1604

1604

本文档的主要内容详细介绍的是Arduino的累加器实验程序和工程文件免费下载。

2021-01-13 17:24:00 5

5 在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。 1、DDS相位累加器 (1)DDS合成流程 首先讲述DSS(直接频率合成法)的原理。 DDS是重要的频率合成方法,在波形

2020-11-29 10:19:00 3728

3728 累加器 (accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写回到 内存,也许马上就得读回来。然而存取主存的速度是比从算术逻辑单元到有直接路径的累加器存取更慢。

2020-10-14 16:00:00 8

8 图5.FTW最右边非零位的位置确定了理论上SFDR的最差水平。由Nicholas修改的相位累加器解决了采用任何N值的问题,并且使NCO的SFDR最大。

2020-10-07 10:33:00 1580

1580

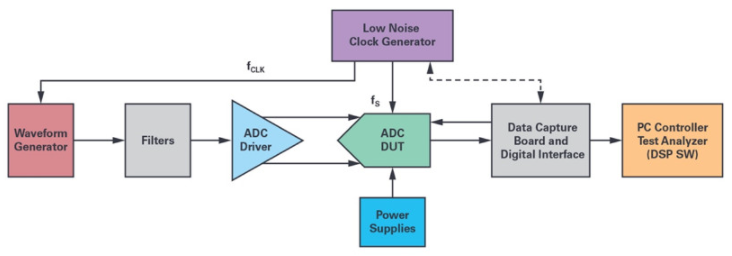

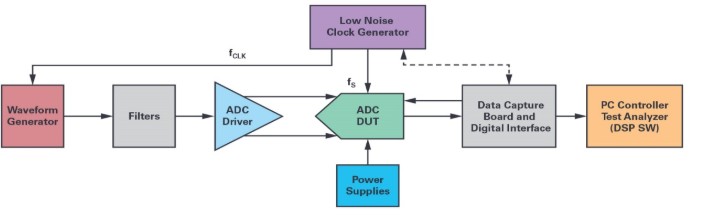

的某种波形。 在测试测量领域有另一个概念 - AWG(任意波形发生器)是跟DDS紧密相关的,波形发生器未必一定采用DDS的方式,但任意波形的产生就离不开DDS了。 DDS可以生成任意波形 - 比如心状波形 DDS的基本原理如下面的框图,主要由以下几个部

2020-09-24 14:20:24 11474

11474 的产生原理是基于奈奎斯特采样定律, 先对模拟信号采集,经过量化后存入查表中, 再由相位累加器产生地址, 通过对查表寻址,得到离散化波形序列,最后经过D/A 转换输出模拟波形。方波的产生是在输出波形的前半周期输出低电平, 后半周期输

2020-08-25 16:32:00 4

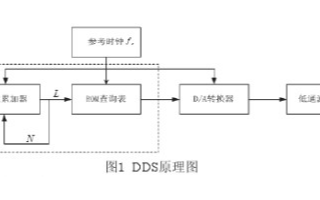

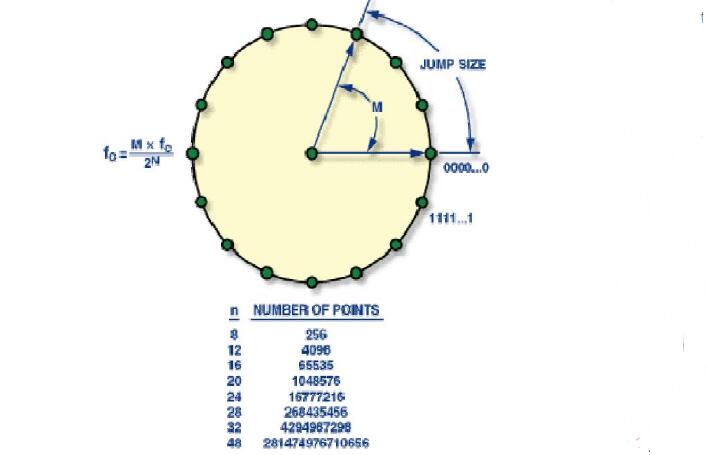

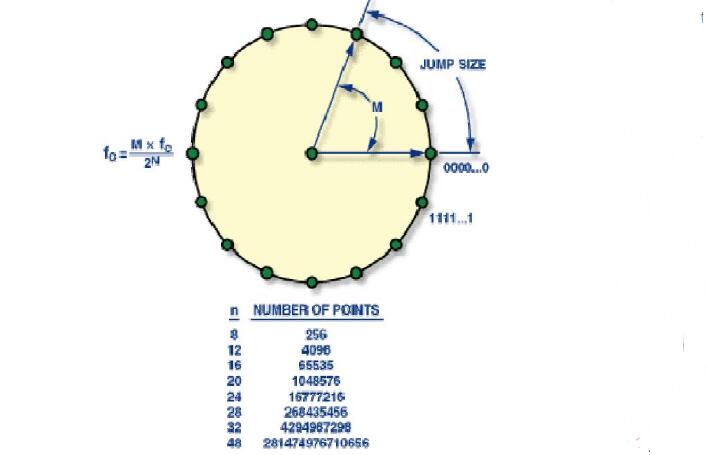

4 DDS的原理如图1所示,包含相位累加器、波形存储器(ROM)、数模转换器(DAC)和低通滤波器4个部分。在参考时钟的驱动下,相位累加器对频率控制字N位进行累加,得到的相位码L作为ROM的地址,根据地址ROM输出相应幅度的波形码,然后经过DAC生成阶梯波形,经低通滤波器后得到所需要的连续波形。

2020-01-14 16:27:27 2476

2476

假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N, 则可以产生一个频率为Fc/2N 的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,

2019-07-22 08:52:56 6983

6983 在系统时钟脉冲的作用下,相位累加器不停累加,即不停查表,把波形数据送到D/A转换器转换成模拟量输出,从而合成波形。滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号。

2019-05-12 09:41:58 3495

3495

DDS频率合成器具有频率分辨率高,输出频点多,可达2N个频点(假设DDS相位累加器的字长是N);频率切换速度快,可达us量级;频率切换时相位连续的优点,可以输出宽带正交信号,其输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻。

2019-04-24 08:30:00 2795

2795

为通信应用生成模拟或数字FM时,IQ调制器提供通用的低功耗解决方案。示例设计将显示混合信号MCU如何用于执行相位累加器和正弦/余弦查找表功能。证明了IQ调制器精度和线性度的重要性。

2019-04-15 08:18:00 5007

5007

本系统采用数字合成芯片AD9850完成整个系统设计AD9850内含可编程DDS系统和高速比较器,能实现全数字编程控制的频率合成。可编程DDS系统的核心是相位累加器,它由一个加法器和一个N位相位寄存器

2018-11-19 08:00:00 36

36 DDS由相位累加器、只读存储器(ROM)、数模转换器(DAC)和低通滤波器(LPF)组成。DDS的关键部分是相幅转换部分,根据相幅转换方式的不同,DDS大致可分为两大类:(1)ROM查询表法。ROM

2018-10-07 11:50:50 3000

3000

设计时,只要将波形的一个周期(周期波形)中分成N段输出就可以了。 DDS的实现一般都是由频率控制器、相位累加器和波形存储器构成(如图3)。 图3 刚刚开始的时候百度到这个信息,笔者也不太

2018-08-22 19:18:00 79

79 DDS频率合成器具有频率分辨率高,输出频点多,可达2N个频点(假设DDS相位累加器的字长是N);频率切换速度快,可达us量级;频率切换时相位连续的优点,可以输出宽带正交信号,其输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻。

2018-06-11 09:49:00 4780

4780

直接数字频率合成(DDS)技术是20世纪70年代以来推出的一种频率合成法。随着数字集成电路和微电子技术发展,DDS技术已广泛应用于电子、通信、雷达等领域。DDS是通过改变频率控制字来改变相位累加器

2018-06-07 08:07:00 18101

18101 在中央处理器中,累加器(accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写回到内存,也许马上就得读回来。然而存取主存的速度是比从算术逻辑单元到有直接路径的累加器存取更慢。

2018-04-11 16:46:27 20510

20510 本文首先对寄存器、累加器、暂存器做个哥介绍,其次解答了累加器是不是寄存器,最后阐述了寄存器、累加器、暂存器的区别。

2018-04-11 16:31:42 8860

8860 本文开始介绍了累加器的概念和相位累加器原理,其次介绍了累加器的作用,最后介绍了流水线相位累加器的设计与累加定时器在PLC控制程序中的应用。

2018-04-11 11:40:16 65911

65911

DDS的具体工作过程如图1所示。N位相位累加器由N位加法器和N位累加寄存器组成。每来一个时钟脉冲,N位加法器将频率控制字K与N位累加寄存器输出的累加相位数据相加,并把相加后的结果送至累加寄存器的输入

2017-11-24 15:06:42 7012

7012

导航数字信号源的系统设计,完整参考方案 本无线电导航数字信号源总体设计思想采用直接数字频率合成器(DDS)技术,设计精确的时钟参考源精度、频率和相位累加器字长和正弦波函数表,实现研制技术要求的输出频率变化范围、频

2017-11-15 13:59:17 21

21 AD9854正交数字信号发生器是一款有着广泛应用的非常灵活的器件。器件包括一个48位的相位累加器,可编程基准时钟乘法器,反辛格滤波器,数字乘法器,两个12位/300HZ数模转换器,一个高速模拟比较器和内部逻辑电路。这款高度集成的器件可以用作本机震荡发生器,灵活的时钟发生器和FSK/BPSK调制器。

2017-11-03 18:31:00 3785

3785

直接数字频率合成(DDSDigital Direct Frequency Synthesis)技术是一种新的频率合成方法 DDS是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。时钟频率给定后,

2011-04-06 16:34:30 45

45 在利用可编程电路实现高速直接数字合成的基础上,提出了一种通过实时改变直接数字合成频率控制字,直接实现波形频率调制的方法。重点对高速相位累加器、FM、扫频、FSK等调

2009-02-28 16:45:28 26

26 TMS320F24X 指令集累加器、算术与逻辑指令附件

TMS320F24X 指令集累加器、算术与逻辑指令

助记

2008-10-17 22:41:11 1024

1024

电子发烧友App

电子发烧友App

评论