主要有代数译码和概率译码两种。代数译码根据卷积码自身的代数结构进行译码,计算简单;概率译码则在计算时考虑信道的统计特性,计算较复杂,但纠错效果好得多。典型的算法如:Viterbi 译码、序列译码等

2008-05-28 15:03:31

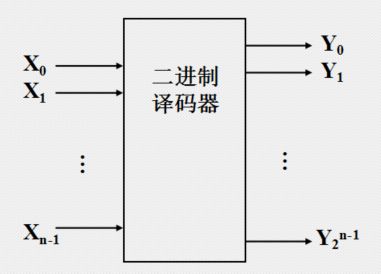

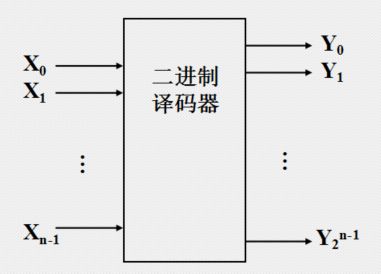

输入:二进制代码,有n个;

输出:2^n 个特定信息。

1.译码器电路结构

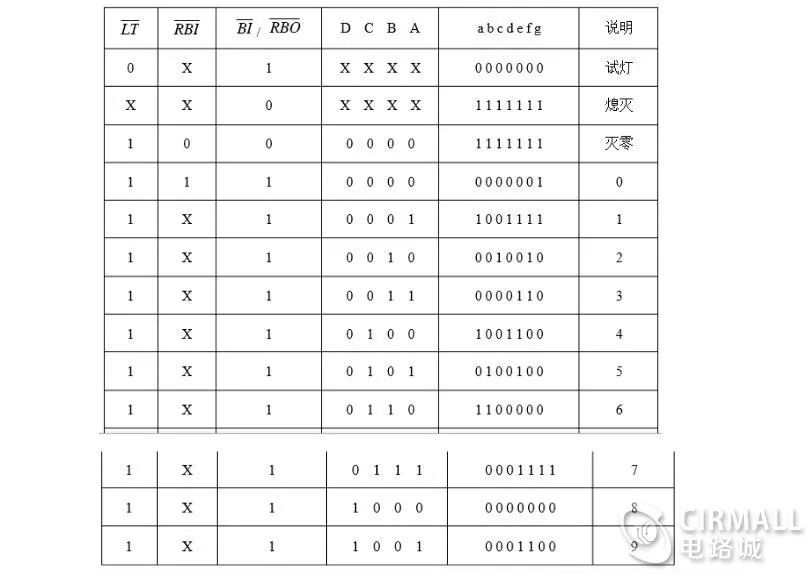

以2线— 4线译码器为例说明

2线— 4线译码器的真值表为:

2023-04-30 16:29:00 684

684

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出的高、低电平信号。常用的译码器电路有二进制译码器、二--进制译码器和显示译 码器。译码为编码的逆过程。它将编码时赋予代码的含义“翻译”过来。实现

2023-04-26 15:39:40 2201

2201

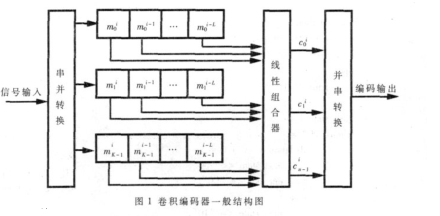

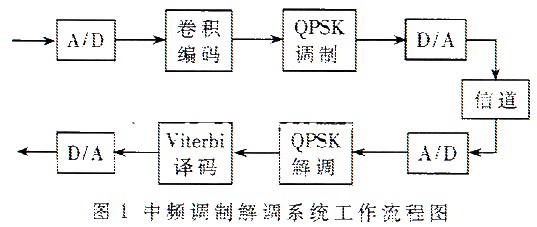

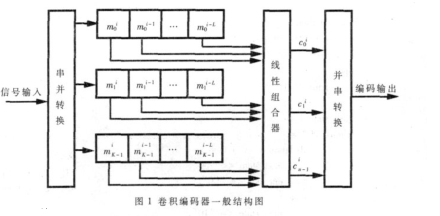

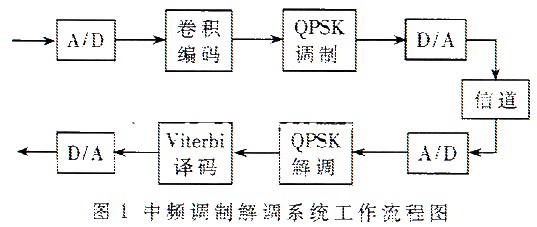

卷积码是一种信道纠错编码,在通信中具有广泛的应用。在发送端根据生成多项式进行卷积码编码,在接收端根据维特比(Viterbi)译码算法进行译码,能够有效抵抗信道噪声的影响,在误码率门限之下可以对传输过程中发生的突发错误进行纠错。

2022-04-28 15:02:12 7304

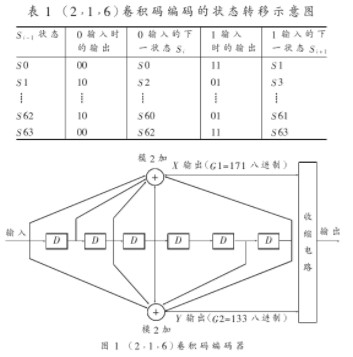

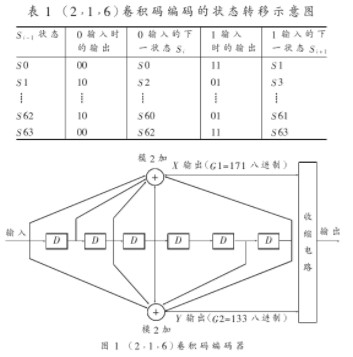

7304 介绍并用VHDL语言实现了卷积编码和维特比译码。根据编码器特征设计了一种具有针对性的简洁的维特比译码器结构,

2021-05-12 15:22:41 1868

1868

为了满足复杂的无线通信系统功耗以及性能要求,提出并设计了一种指针反馈式Viterbi译码器。该译码器使相邻时刻的

2021-04-28 09:35:41 1378

1378

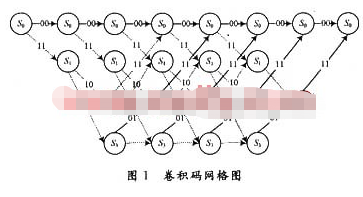

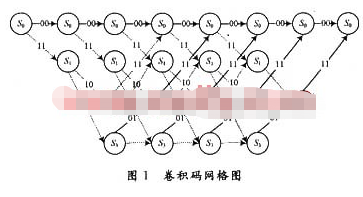

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法

2020-08-11 17:41:23 605

605

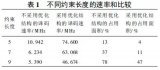

记(n0,k0,m)为卷积码编码器,该编码器共有2k0×m个状态,Viterbi译码器必须具备同样的2k0×m个状态发生器,且每个状态必须有一个存储路径度量值的存储器和一个存储幸存路径信息的存储器,所以Viterbi译码器的复杂度呈2k0×m指数增长。

2020-07-15 20:53:51 1238

1238

随着现代无线通信系统日益复杂化的发展,无线基带通信系统中各模块的实际性能、延时、功耗等参数成为基带设计的重要考虑因素。Viterbi译码器广泛应用于无线局域网和移动通信系统,并且作为基带系统的重要

2019-10-06 11:09:00 323

323

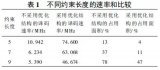

新一代移动通信系统目前主要采用多载波传输技术, 基带传输速率较3G 有很大提高, 一般要求业务速率能达到30 Mb/ s 以上。约束长度卷积码以及Viterbi译码器由于其性能和实现的优点, 在

2019-10-06 10:16:00 1753

1753

信道的是二进制信号序列。为了充分利用信道输出信号的信息,提高传输系统译码的可靠性,首先把信道的输出信号量化,将Q电平量化序列输入Viterbi译码器,因此本文采用的VB译码算法为软判决译码算法。

2019-07-11 08:01:00 2571

2571

和Viterbi译码是广泛使用的信道编码技术,具有一定的克服突发错误的能力,可以降低信道的误码率,带来很高的编码增益。

2019-05-13 08:04:00 5830

5830

卷积码是广泛应用于卫星通信、无线通信等各种通信系统的信道编码方式。Viterbi算法是一种最大似然译码算法。在码的约束度较小时,它比其它概率译码算法效率更高、速度更快,译码器的硬件结构比较简单。随着

2019-04-24 08:29:00 2438

2438

极化码的译码算法研究近年来发展迅速,其中成为研究热点的连续删除(Successive Cancellation,SC)译码算法的基本思想是通过对信息位的比特似然概率值的判断来进行译码。

2019-01-06 11:19:55 4472

4472

由网格图的输入支路特点分析可知,产生任意一个状态节点Si的输入条件mi是确定的,即mi=‘1’,i为偶数;mi=‘0’,i为奇数。输入条件mi表示译码器最终需要输出的比特信息。此外,译码器所要找的留选路径是不同状态的组合。

2018-10-02 01:07:16 4926

4926 在大多数无线通信系统中,卷积编码是最好的方法。纠错编码以克服传输失真。这份报告概述了这一理论。卷积编码和译码,解释维特比的编程技术TI TMS3C35X数字信号处理器的解码(DSPs)相同的基本方法对任何卷积码进行译码。本申请报告用一般的观点来考察问题,而不是为特定的问题勾勒出解决方案。

2018-04-25 09:47:38 3

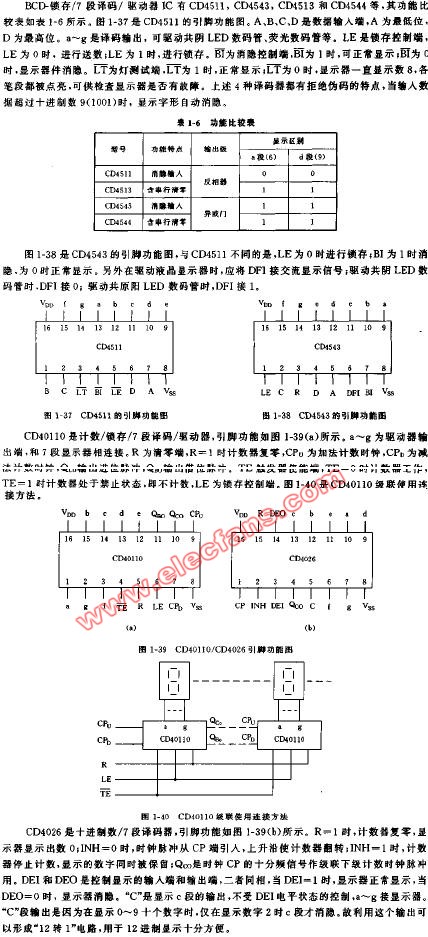

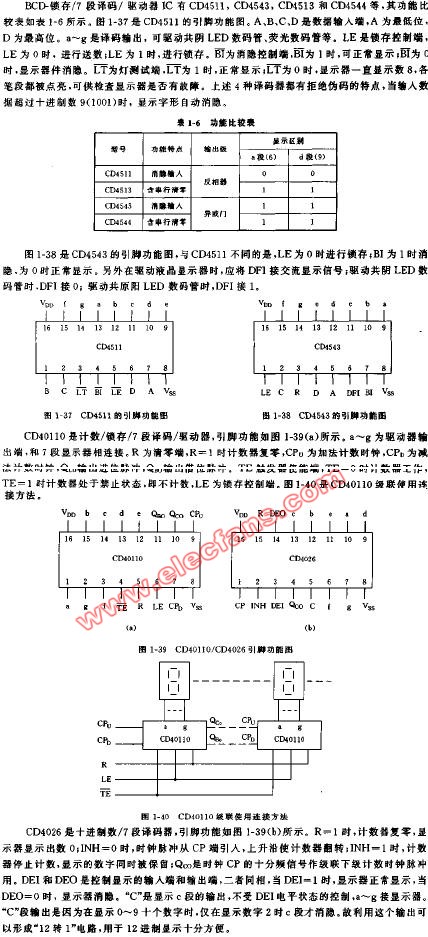

3 本文主要介绍了译码器的分类和应用。译码器指的是具有译码功能的逻辑电路,译码是编码的逆过程,它能将二进制代码翻译成代表某一特定含义的信号(即电路的某种状态),以表示其原来的含义。译码器可以分为:变量

2018-04-04 11:51:12 35527

35527

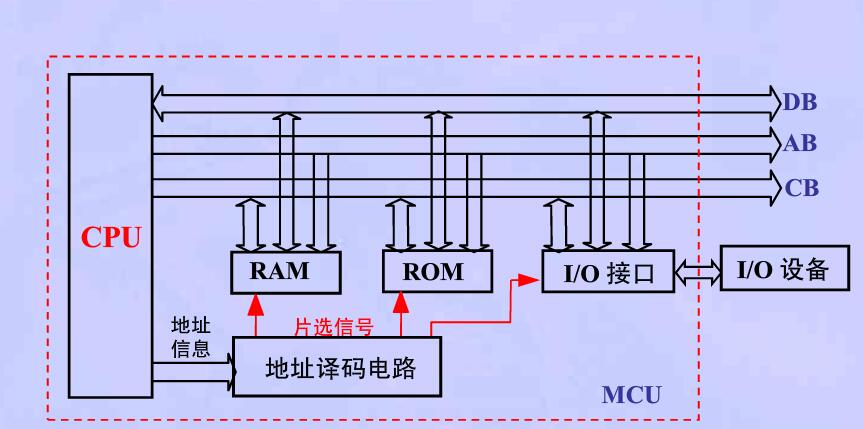

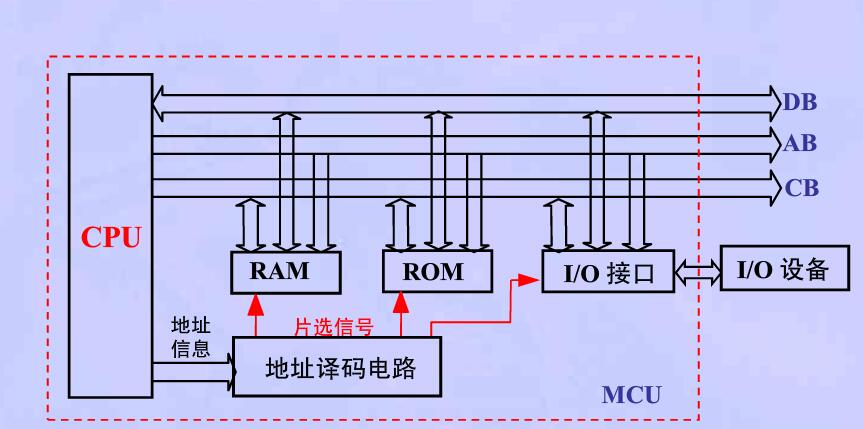

地址译码有两种方式,一种是单译码方式,或称为字结构方式;另一种是双译码方式,或称为X-Y译码结构。

2018-03-02 16:11:02 9355

9355

常用的译码电路有哪些?本文主要介绍了IO接口地址译码电路、BCD译码驱动器电路、4线16线译码电路、3.8线译码器电路以及继电器译码电路。继电器译码电路的作用是在单片机的控制下将1 536个测试点

2018-03-02 15:48:20 37712

37712

本文首先介绍了译码器的定义与译码器的分类,其次介绍了译码器的作用和译码器的工作原理,最后介绍了译码器的逻辑功能。

2018-02-08 14:04:06 104354

104354

针对无线通信系统中对于高频率、高吞吐量的要求,提出了一种基于ASIC的高速Viterbi译码器实现方案。该译码器在约束度小于等于9的情况下,采用全并行结构的加比选模块。性能分析结果表明,在SMIC

2017-11-11 17:56:15 6

6 为了解决在RS译码中存在的译码过程复杂、译码速度慢和专用译码器价格高等问题,以RS(255,239)码为例,采用了基于改进的无求逆运算的Berlekamp-Massey( BM)迭代算法。结合FP

2017-11-07 15:27:06 15

15 2Mbps视频数据流的Viterbi算法的移植与优化策略、技巧。 1 Viterbi算法原理简介 Viterbi译码算法是由Viterbi于1967年提出的一种最大似然译码方法,译码器根据接收序列R按最大似

2017-10-24 11:41:30 0

0 DSP嵌入式系统开发典型案例,第9章 Viterbi译码及其实现

2017-10-20 14:23:37 4

4 应用于LTE_OFDM系统的Viterbi译码在FPGA中的实现

2016-05-11 11:30:19 11

11 设计、高速数据采集系统设计、常用自动控制系统设计、语音信号处理、编码系统设计、ip电话系统设计、无线网卡系统设计、viterbi译码的实现、非均匀采样理论及其实现等工程实例。

2015-12-24 14:07:16 22

22 介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构实现

2013-01-25 16:43:46 68

68 文中提出的卷积码译码Matlab仿真方案,旨在用Viterbi译码实现对卷积码译码的功能。仿真结果表明,维特比是一种良好的译码方式。

2012-03-22 17:21:11 57

57 本文主要对卷积码编码和Viterbi译码进行MATLAB实现,并在此基础上分析移位寄存器对纠错能力的影响。论文首先根据MATLAB的存储特点及函数特征,主要介绍卷积编码的原理,同时给出MA

2012-01-13 16:56:57 34

34 该文介绍了两种Viterbi 译码器回溯译码算法,通过对这两种算法硬件实现结构上的优化,给出了这两种算法的FPGA 实现方法,比较了两种实现方法的优缺点。最后将其应用在实际的Viter

2011-05-28 15:18:48 33

33 Viterbi译码是一种应用广泛的最大似然估计算法; 而功耗是通信系统设计中的一个重要制约因素,介绍了3种Viterbi译码的低功耗设计方法。对这3种设计方法的原理和实际使用效果作了详

2011-05-16 15:54:11 11

11 Viterbi算法代表了统计概率的模式匹配算法,而DTW算法代表了模版匹配的模式匹配算法,它们之间是否存在关系至今尚无定论

2011-02-22 14:51:23 17

17 Turbo码虽然具有优异的译码性能,但是由于其译码复杂度高,译码延时大等问题,严重制约了Turbo码在高速通信系统中的应用。因此,如何设计一个简单有效的译码器是目前Turb

2010-11-25 10:10:26 1677

1677

本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi译码的实现方案,对译码的各个组成部分作了分析,并在FPGA中实现

2010-07-21 17:20:04 22

22 卷积码/Viterbi译码,卷积码/Viterbi译码是什么意思

卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(

2010-03-18 14:09:21 2193

2193 译码器,译码器是什么意思

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。 变量译码一

2010-03-08 16:32:18 5062

5062 文章分析了Turbo 码的MAP 类译码算法后,针对传统Log—MAP 译码算法的特性,提出了一种改进的Log—MAP 译码算法。仿真结果表明,新的算法在降低译码复杂度的同时较好地保持了译

2010-01-15 11:51:47 13

13 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi 译码的实现方案,对译码的各个组成部分作了分析,并在FP

2010-01-06 15:06:59 12

12 介绍了 TI 的TMS320C6416 DSP 片上Viterbi 译码协处理器(VCP)的结构与原理。给出了一种使用链式EDMA 结构和“乒乓”缓冲技术提高VCP 译码过程并行性的方法。设计出基于MATLAB 的Link for

2009-12-23 15:19:48 19

19 计数/译码显示电路: 计数译码显示在现代科学技术中应用非常广泛,它由计数器、译码器和显示器三部分组成,包含数字电子系统的组合逻辑电路和

2009-12-20 12:36:59 128

128 3G测试系统中的Viterbi译码及其DSP实现及优化

摘要 介绍了一种用于测试TD-SCDMA手机终端测试平台中的关键技术——Viterbi译码。研究用约束度K=9的卷积编码和最大似然Viterbi译

2009-11-13 18:51:25 18

18 给出了由(2,1,N)系列卷积码Viterbi 译码中路径度量存储器及其接口的使用FPGA实现时的设计方法,译码器采用四个ACS 并行运算的方式,状态度量的更新采用乒乓模式,阐述了存

2009-09-08 14:49:05 9

9 基于对传统Viterbi 译码器的分析和对改进的Viterbi 算法理论的修正,提出了一种新的Viterbi 译码器的实现方法。通过对路径度量值的深入分析和对回溯信息的重新编码,在不增加硬

2009-08-13 10:43:19 23

23

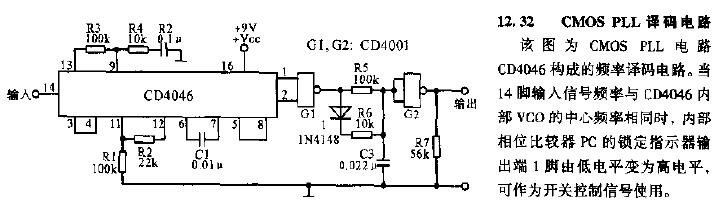

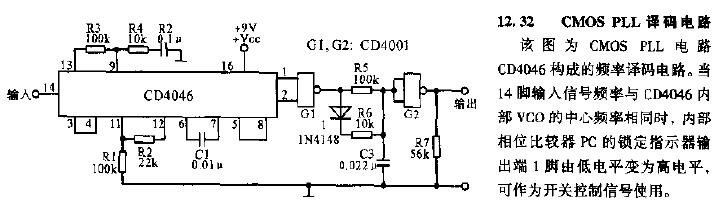

CMOS PLL译码电路

2009-04-18 11:07:44 542

542

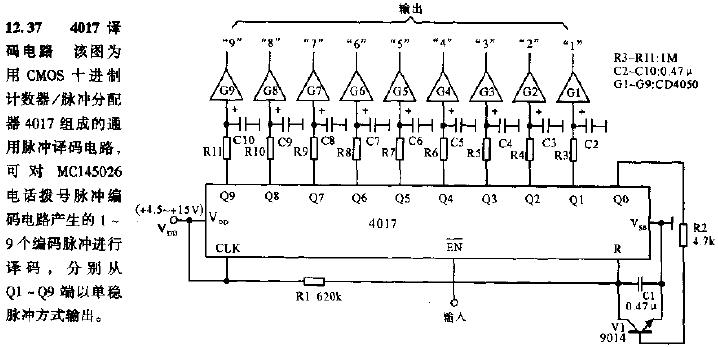

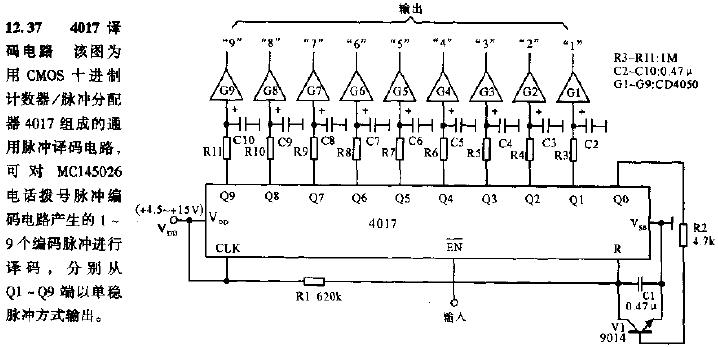

4017译码电路

2009-04-18 11:06:35 1248

1248

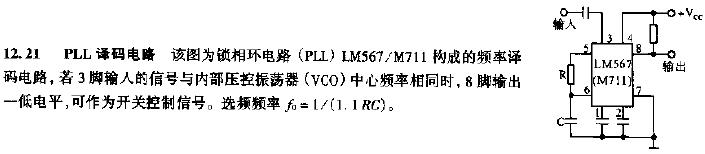

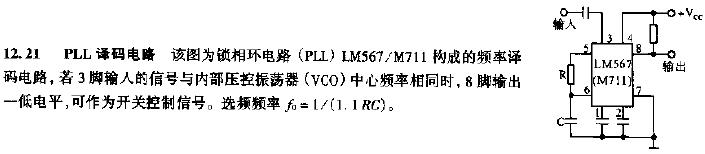

PLL译码电路

2009-04-12 13:15:57 496

496

集成电路译码器

1.74138集成译码器

上图为常用的集成译码器74138,其功

2009-04-07 10:24:17 7830

7830

译码器的定义及功能

译码是编码的逆过程,它的功能是将具有特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路称为译码器

2009-04-07 10:23:42 15826

15826

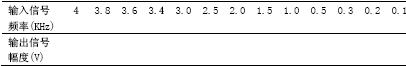

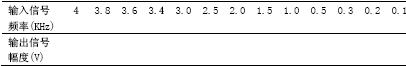

实验九 PCM编译码 一、实验目的

1. 掌握PCM编译码原理。 2. 掌握PCM基带信号的形成过程

2009-04-01 14:44:49 9420

9420

Altera viterbi compiler v1.0 下载

2009-03-23 09:45:42 31

31 LDPC编译码LDPC码是一种线性分组奇偶校验码,它采用基于因子图的置信传播(Belief Propagation,BP)迭代译码算法进行译码。其性能接近Turbo码,不规则LDPC码甚至超过Tur

2009-03-01 17:36:05 1696

1696

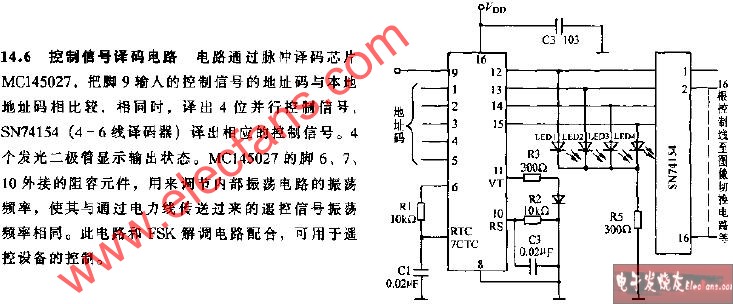

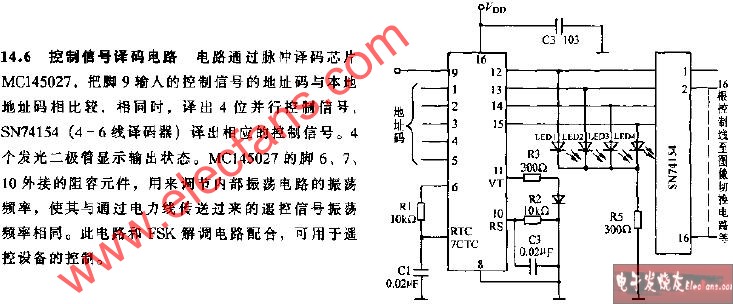

控制信号译码电路

2009-02-25 21:54:51 472

472

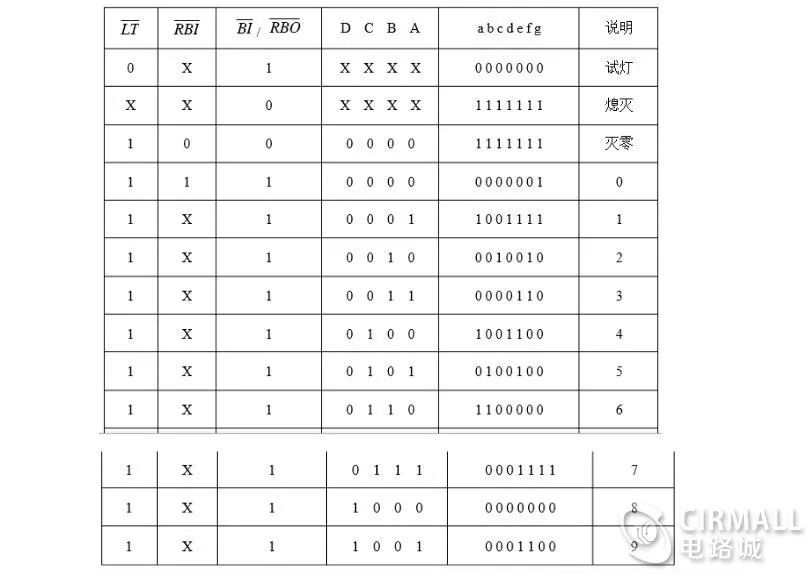

显示译码器的应用:

2008-12-17 14:35:06 1199

1199

数码译码器的应用:译码器课件ppt

2008-12-17 14:31:20 999

999

PCM编译码实验

一、实验目的1. 掌握PCM编译码

2008-10-21 13:35:45 7675

7675

译码器

译码是编码的逆过程,即将某个二进制翻译成电路的某种状态。实现译码操作的电路称为译码器。

2008-09-27 12:59:06 11977

11977

大约束度Viterbi译码器中路径存储单元的设计

1 引言 Viterbi译码算法是一种最大似然译码算法,目前广泛应用于各种数据传输系统,特别是卫星

2007-08-15 17:21:47 815

815

Altera viterbi compiler

2006-03-25 15:45:58 18

18 Viterbi Compiler MegaCore Function User Guide

好东西哦。网上搜集,希望对你有用。

2006-03-25 15:40:49 32

32

电子发烧友App

电子发烧友App

评论