Interface Data Sheet的引脚图、接线图、封装手册、中文资料、英文资料,MAX16550A-MAX16550B: Integrated Protection IC on 12V Bus

2023-10-17 19:04:14

电子发烧友网为你提供ADI(ADI)AD2430/AD2438: Automotive Audio Bus (A<sup>2</sup>B) Transceiver Data

2023-10-12 18:53:45

AD7380/AD7381: What are the pros and cons of a Serial 2 wire mode and serial 1 wire mode?

2021-02-02 09:24:09 13

13 What Is XML?XML stands for Extensible Markup Language (often written aseXtensibleMarkup Language

2008-10-07 14:21:05

This data is presented for the purpose of quick selection. It lists what is considered

2016-09-12 15:57:20 2

2 What the Internet of Things (IoT) Needs to Become a Reality,Freescale发布的IOT白皮书!

2015-10-30 17:04:40 7

7 The SN65LBC176A, SN65LBC176AQ, and SN75LBC176A differential bus transceivers are monolithic

2010-09-04 21:47:04 10

10 The TL3695 differential bus transceiver is designed for bidirectional data communication

2010-09-04 17:12:02 12

12 The SN75176A differential bus transceiver is a monolithic integrated circuit designed

2010-09-03 03:56:14 29

29 registers and provide extra data width for wider address/data paths or buses carrying parity. The CY74FCT823T is a 9-bit-wide buffered r

2010-07-26 16:31:38 6

6 registers and provide extra data width for wider address/data paths or buses carrying parity. The CY74FCT823T is a 9-bit-wide buffered r

2010-07-26 16:23:49 6

6 registers and provide extra data width for wider address/data paths or buses carrying parity. The CY74FCT823T is a 9-bit-wide buffered r

2010-07-26 16:22:20 5

5 registers and provide extra data width for wider address/data paths or buses carrying parity. The CY74FCT821T is a 10-bit-wide buffered

2010-07-26 16:20:53 4

4 registers and provide extra data width for wider address/data paths or buses carrying parity. The CY74FCT821T is a 10-bit-wide buffered

2010-07-26 16:19:22 6

6 registers and provide extra data width for wider address/data paths or buses carrying parity. The CY74FCT821T is a 10-bit-wide buffered

2010-07-26 16:16:13 5

5

The SN74LVCZ32245A is designed for asynchronous communication between data buses. The control-function implementation

2010-07-25 17:35:25 5

5 is designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus or from th

2010-07-25 17:33:15 8

8

The SN74LVCZ16245A is designed for asynchronous communication between data buses. The control-function implementation

2010-07-25 17:31:32 8

8 operation.

The SN74LVC32245A is designed for asynchronous communication between data buses. The control-function implementation

2010-07-25 17:27:50 5

5 is designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus or from

2010-07-25 17:24:34 20

20 operation.

The SN74LVCR16245A is designed for asynchronous communication between data buses. The control-function implementatio

2010-07-25 17:18:28 9

9 operation.

The SN74LVCHR32245A is designed for asynchronous communication between data buses. The control-function implementati

2010-07-25 17:10:11 8

8 operation.

The SN74LVCHR16245A is designed for asynchronous communication between data buses. The control-function implemen

2010-07-25 17:07:23 9

9 operation.

The SN74LVCH32245A is designed for asynchronous communication between data buses. The control-function implementatio

2010-07-25 17:04:39 6

6 This 9-bit bus transceiver is designed for 1.65-V to 3.6-V VCC operation.

The SN74LVC863A

2010-07-25 16:39:13 8

8 This 10-bit bus transceiver is designed for 1.65-V to 3.6-V VCC operation.

The SN74LVC861A

2010-07-24 20:09:28 11

11 is designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus or from th

2010-07-24 19:39:37 32

32 operation.

The SN74LVC16245A is designed for asynchronous communication between data buses. The control-function implementation

2010-07-24 17:27:33 19

19 This octal bus transceiver is designed for asynchronous two-way communication between data buses.

2010-07-24 17:17:58 16

16 are designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus or

2010-07-24 17:09:45 21

21 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the level at the direction control

2010-07-24 16:55:03 24

24 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the level at the direction control

2010-07-24 16:49:29 6

6 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the level at the direction control

2010-07-24 16:46:27 5

5 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the level at the direction control

2010-07-24 16:43:08 12

12 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the level at the direction control

2010-07-24 16:38:31 18

18 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the level at the direction control

2010-07-24 16:34:57 8

8 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending upon the level at the direction-contr

2010-07-24 15:37:34 8

8 The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the logic level at the direction-control (D

2010-07-24 14:47:58 6

6 The control-function implementation allows for maximum flexibility in timing.

The device allows data transmission from the A bus to the B bus

2010-07-24 14:35:19 9

9 This 25-octal bus transceiver is designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus

2010-07-24 14:24:27 4

4 The ´BCT25245 is a 25- octal bus transceiver designed for asynchronous communication between data buses. It improves both the performance an

2010-07-24 14:20:51 10

10 is designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus or from t

2010-07-23 18:46:52 12

12 is designed for asynchronous communication between data buses. The device transmits data from the A bus to the B bus or from th

2010-07-23 18:39:24 15

15 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the level at the direction-control

2010-07-23 18:37:54 8

8 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the level at the direction-control

2010-07-23 18:36:32 8

8 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending upon the level at the directi

2010-07-23 18:32:59 15

15 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending upon the level at the directi

2010-07-23 18:31:09 12

12 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending upon the level at the directi

2010-07-23 18:22:43 7

7 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending upon the level at the direction-contr

2010-07-23 18:21:23 4

4 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending upon the level at the direction-contr

2010-07-23 18:18:58 7

7 open-collector and 3-state buses. The devices transmit data from the A bus (open-collector) to the B bus (3 state) or from the B bus to the A bus,

2010-07-23 18:17:46 11

11 open-collector and 3-state buses. The devices transmit data from the A bus (open-collector) to the B bus (3 state) or from the B bus to the A bus,

2010-07-23 18:14:17 10

10 These octal bus transceivers are designed for asynchronous two-way communication between data

2010-07-23 18:11:20 11

11 These octal bus transceivers are designed for asynchronous two-way communication between data

2010-07-23 18:09:52 8

8 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the level at the direction-control

2010-07-23 17:42:09 16

16 buses. These devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the direction-

2010-07-23 17:39:41 5

5 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the directio

2010-07-23 17:20:16 9

9 The devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the direction-control (DI

2010-07-23 17:13:27 5

5 The devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the direction-control (DI

2010-07-23 16:46:34 28

28 buses. The devices transmit data from the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the directio

2010-07-23 16:44:55 13

13 The devices transmit data from the A bus to the B bus or from the B bus to the A bus depending upon the logic level at the direction-control (DIR)

2010-07-23 16:18:54 9

9 function implementation allows for maximum flexibility in timing.

The device allows data transmission from the A bus to the B bus

2010-07-22 17:23:42 12

12 The control-function implementation minimizes external timing requirements.

The device allows data transmission from the A bus to t

2010-07-22 17:21:52 14

14

The SN74LVCH16652A consists of D-type flip-flops and control circuitry arranged for multiplexed transmission of data directly fro

2010-07-22 16:45:15 3

3

The SN74LVC2952A consists of two 8-bit back-to-back registers that store data flowing in both directions between two bidirectional

2010-07-22 16:31:43 11

11 arranged for multiplexed transmission of data directly from the data bus or from the internal storage registers. Enable GAB and GBA are provide

2010-07-22 16:28:11 2

2

The SN74ALVCH16646 can be used as two 8-bit transceivers or one 16-bit transceiver. Data on the A or B bus is clocked into the re

2010-07-21 22:05:27 11

11 arranged for multiplexed transmission of data directly from the data bus or from the internal storage registers. Output-enable (OEAB and OEBA)

2010-07-21 21:53:35 5

5 arranged for multiplexed transmission of data directly from the data bus or from the internal storage registers. Output-enable (OEAB and OEBA)

2010-07-21 21:49:49 6

6 flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the data bus or from the internal storage reg

2010-07-21 21:44:14 3

3 arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus is clocked into

2010-07-21 21:18:19 5

5 for multiplexed transmission of data directly from the data bus or from the internal storage registers. Enable GAB and GBA are provided

2010-07-20 15:58:52 4

4 What Is Portable Digital Storage?

Portable digital storage is a storage solution which is designed

2010-03-25 11:16:34 797

797 What Is a Portable Hard Drive?

A portable hard drive is a type of digital storage device.

2010-03-25 11:16:03 1234

1234 What is UATA?

In computers, Ultra Advanced Technology Attachment (UATA) is a term used to describe

2010-03-25 11:15:36 832

832 What is an SCSI Hard Drive?

A SCSI hard drive is a storage drive which uses a different system

2010-03-25 11:15:03 1470

1470 for SATA technologies. It competes with FireWire 400 and universal serial bus (USB) 2.0 to provide fast data transfer speeds

2010-03-25 11:12:56 1179

1179 , the characteristicimpedance of a PCB trace, along comes a data sheetthat tells you to design for a specific differential impedance.And

2010-01-15 10:21:47 19

19 Impedance Terminations -What’s the Value:There is a lot of confusion in the industry about

2010-01-15 09:16:29 11

11

Problem What range of dielectric constants you could be realize with your PCB materials?

2009-12-29 09:26:53 639

639

Problem What is the maximum temperature your PCB can handle?

Solution 130 Degrees C.266 Degrees F.

Details:

2009-12-29 09:25:02 397

397 What is the minimum space between a pair of tracks on a PCB that could be manufactured?

Problem

2009-12-29 09:24:25 742

742 What is Soldermask? 什么是绿油

The normally green coating used to protect the board and circuitry

2009-12-29 09:20:04 1792

1792 What It Me

2009-11-26 10:16:28 36

36 The SCAN921023 transforms a 10-bit wide parallelLVCMOS/LVTTL data bus into a single high speed

2009-10-13 09:58:16 31

31 The SCAN921023 transforms a 10-bit wide parallelLVCMOS/LVTTL data bus into a single high speed

2009-10-13 09:53:03 1

1 What is NI Ultiboard?什么是Ultiboard?

National Instruments Electronics Workbench GroupThe National Instruments Electronics Workbench Group (for

2009-07-01 07:47:47 3222

3222 What It Me

2009-06-29 16:13:09 6

6 iCoupler® Isolation in CAN Bus Applications:The Controller Area Network (CAN) bus, a robust

2009-06-21 10:28:21 17

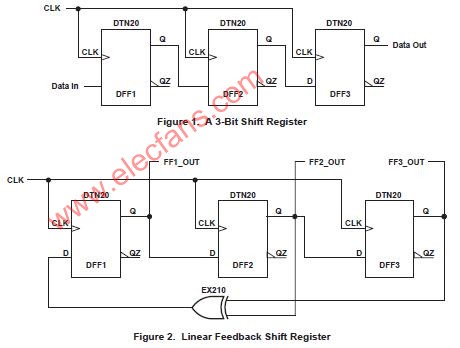

17 What is an LFSR,什么是LFSR

Texas Instruments (TI) reserves the right to make changes to its products

2009-06-14 09:10:53 31

31 什么是LFSR,What is an LFSR?

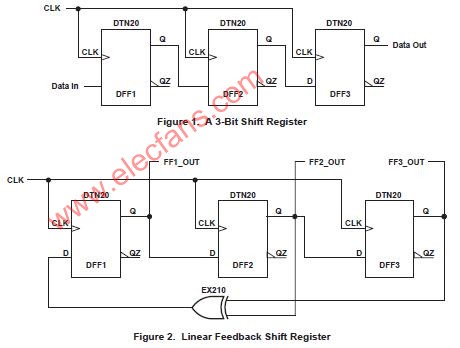

The purpose of this article is to explain what a Linear Feedback Shift

2009-05-14 11:42:37 2311

2311

Abstract: The following article describes how to slow down and store high-speed data of a typical

2009-05-08 11:00:09 794

794

in a classic FAQ format it addresses topics such as: What is an ADC, what is a DAC, what is nyquist, effects of charge injection, techniques f

2009-05-08 09:18:13 5466

5466

Universal Serial Bus Device Class Definition for Audio Data Formats

The intention of this document

2009-04-11 19:34:18 26

26 Universal Serial Bus Device Class Definition for Printing Devices

The Universal Serial Bus (USB

2009-04-11 19:32:14 15

15 PCI Local Bus Specification V2.3

The PCI Local Bus is a high performance 32-bit or 64-bit bus

2008-12-09 14:03:01 182

182 transmissionfrom the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the direction-control(DIR) input

2008-10-14 09:39:22 35

35 RS485 Application Using A Combination of NXP And ADI Products

RS485 Bus is a serial communication

2008-04-09 16:00:14 1559

1559

电子发烧友App

电子发烧友App

评论