除法器对数运算电路的应用

- 除法器(13808)

相关推荐

运算放大电路的设计实验

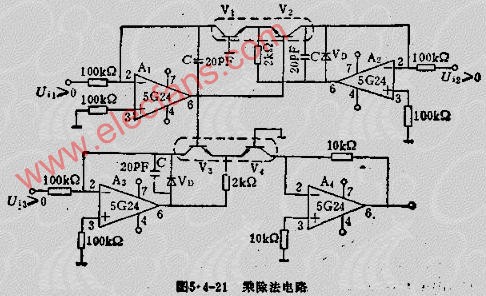

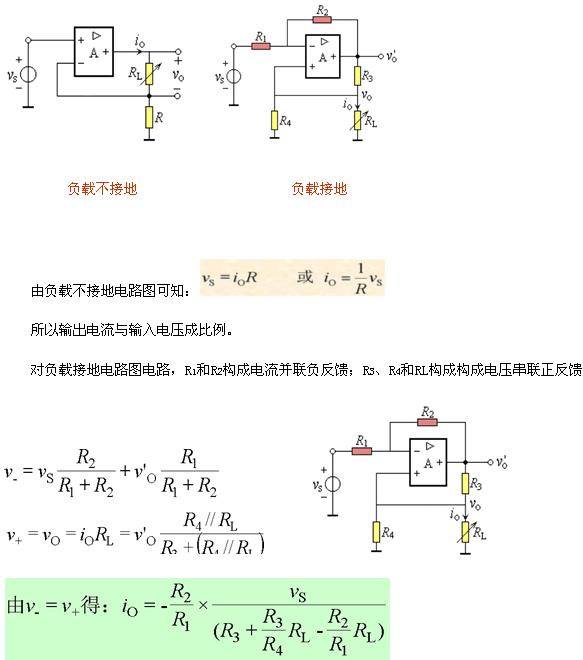

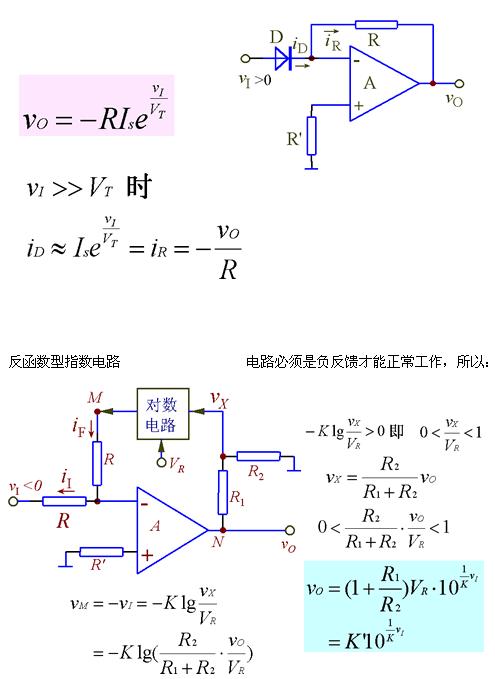

,可以实现乘法、除法、对数等模拟运算功能。如果加入线性或者非线性正反馈网络(或将正、负两种反馈形式同时加入),就可以构成一个振荡器产生各种不同的形态的模拟信号(如正弦波、三角波等)由运算放大器和深度负反馈网络组成的模拟运算电路如图1所示。

2008-09-22 13:09:28

AD534KDZ 模拟IC乘法器除法器

AD534是一款单芯片激光调整四象限乘法器除法器,其精度规格以前只有昂贵的混合或模块化产品才有。无需任何外部调整,AD534L的最大乘法误差保证为0.25%。出色的电源抑制性能、低温度系数以及片内

2023-08-09 16:52:53

FPGA基于线性迭代法的除法器设计

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想打打拍改善下时序都不知从何下手。

2023-07-04 10:03:39 236

236

236

236

FPGA常用运算模块-加减法器和乘法器

本文是本系列的第二篇,本文主要介绍FPGA常用运算模块-加减法器和乘法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:13:57 1336

1336

1336

1336

如何使用LM358运算放大器来演示加法器电路

运算放大器(Opamp)有许多有趣的应用,我们已经使用运算放大器创建了许多电路。今天我们将研究运算放大器的另一个应用,即添加两个或多个输入电压,该电路称为求和放大器或运算放大器加法器。在这里,我们将使用 LM358 运算放大器来演示加法器电路。

2022-11-11 15:29:29 7919

7919

7919

7919

如何实现FPGA中的除法运算

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成。因此FPGA实现除法运算并不是一个“/”号可以解决的。

2022-04-27 09:16:03 5168

5168

5168

5168实例九— 除法器设计

4.3 实例九 除法器设计4.3.1. 本章导读要求掌握除法器原理,并根据原理设计除法器模块以及设计对应的测试模块,最后在 Robei可视化仿真软件经行功能实现和仿真验证。设计原理这个除法器的设计为

2021-11-07 10:51:04 17

17

17

17乘法器原理_乘法器的作用

乘法、除法、乘方和开方等模拟运算的主要基本单元,而且还广泛用于电子通信系统作为调制、解调、混频、鉴相和自动增益控制;另外还可用于滤波、波形形成和频率控制等场合,因此是一种用途广泛的功能电路。

2021-02-18 15:08:01 22932

22932

22932

22932

基于FPGA的除法器纯逻辑设计案例

除法运算。很多人觉得不就是除法嘛,直接打上/即可,但是,FPGA是不能正确综合这个除法器的,综合的结果只是一个固定数值,而不像其他微处理器。可以这么说,用FPGA实现除法运算是比较麻烦的。

2020-06-17 10:17:27 6157

6157

6157

6157

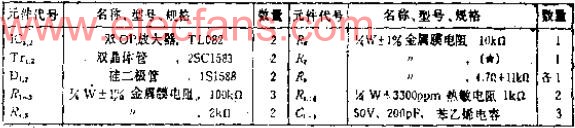

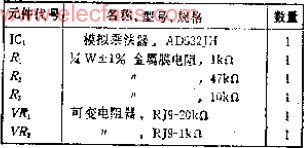

四款常见的除法电路图分享

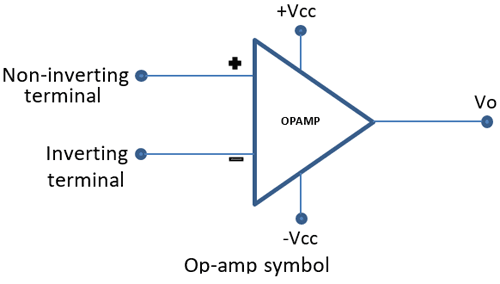

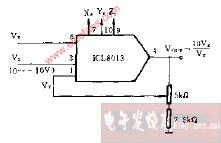

输入信号为V1、V2,输出Vo为Vo=10V2/V1。这种除法器是将乘法器接在运算放大器的反院回路组成的。V1的输入范围为-0.2V到10V,V2的输入范围为-10V到10V。

2019-12-31 14:12:44 15859

15859

15859

15859

用于除法运算的运行时ABI辅助方法过载

SAMC21(一款 Cortex-M0+ MCU)非常适合需要数学计算的应用。SAMC21 MCU 具有可进行乘法运算的快速单周期乘法器选项,还具有一个新的外设,称为除法和平方根加速器

2018-07-19 09:25:25 5141

5141

5141

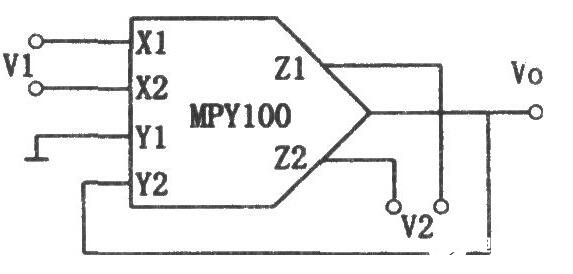

5141微功率乘法器/除法器电路原理

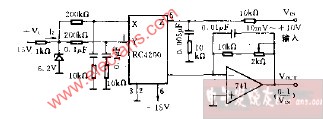

X、Y 和 Z 输入放大器执行伺服操作,以根据施加的信号来控制晶体管的发射极电流。晶体管 Vbe 随电流呈对数变化,因此 Q2 的发射极包括 X 和 Y 对数之和。Z信号对数在 Q4 的基极上提供,于是 Q4 上最终的 Vbe 为 Vbe1 + Vbe2 - Vbe3。

2018-07-05 10:07:00 3082

3082

3082

3082

一文读懂FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且

2018-05-18 01:15:00 3961

3961

3961

3961基于delta码的乘除法运算错误检测改进算法

为确保安全苛求系统中程序执行的正确性,研究人员将差错控制理论用于对计算机指令进行编码,但由于编码大多涉及模运算,导致复杂度大量增加,应用于实时系统有困难。针对复杂度问题对delta码的乘除法运算

2017-12-04 16:44:29 0

0

0

0信号的运算与处理电路--求和运算电路

运算电路是集成运算放大器的基本应用电路,它是集成运放的线性应用。讨论的是模拟信号的加法、减法积分和微分、对数和反对数(指数)、以及乘法和除法运算。

2017-11-27 15:55:10 5

5

5

5进位保留Barrett模乘法器设计

乘法器,求模运算部分利用Barrett约减运算,用硬件描述语言进行FPGA设计与实现,避免了除法运算。对于192位的操作数,完成Barrett模乘需要约186个时钟周期,计算速率可以达到269.17 Mb/s。

2017-11-08 15:18:19 32

32

32

32高效的C编程之除法运算

14.2 除法运算 因为ARM体系结构本身并不包含除法运算硬件,所以在ARM上实现除法是十分耗时的。ARM指令集中没有直接提供除法汇编指令,当代码中出现除法运算时,ARM编译器会调用C库函数(有符合

2017-10-17 17:22:29 5

5

5

5一种模拟除法器的设计及仿真验证CMOS工艺

模拟除法器是一种能实现两个模拟量相除的电子器件。目前不仅应用于模拟运算方面,而且已扩展到无线通讯、电视广播、人工神经网路、机器人控制技术等领域。此外,模拟除法器在模糊控制和测量仪表中也是非常重要的器件。

2014-09-19 15:14:31 2946

2946

2946

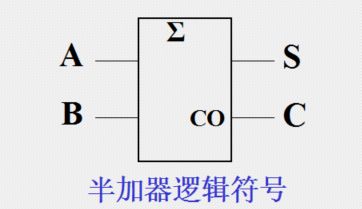

2946FPU加法器的设计与实现

浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计

2012-07-06 15:05:42 47

47

47

47基于Verilog计算精度可调的整数除法器的设计

除法器是电子技术领域的基础模块,在电子电路设计中得到广泛应用。目前,实现除法器的方法有硬件实现和软件实现两种方法。硬件实现的方法主要是以硬件的消耗为代价,从而有实

2012-05-24 09:41:04 1757

1757

1757

1757

AD532,pdf (预调整的单芯片乘法器/除法器)

AD532是首款预调整的单芯片乘法器/除法器;无需任何外部调整电阻或输出运算放大器,即可保证±1.0%的最大乘法误差和±10 V的输出电压范围。AD532经过内部调整,易于使用,为设计

2010-10-02 09:37:50 131

131

131

131乘除法和开方运算的FPGA串行实现

高精度的乘除法和开方等数学运算在FPGA实现中往往要消耗大量专用乘法器和逻辑资源。在资源敏感而计算时延要求较低的应用中,以处理时间换取资源的串行运算方法具有广泛的应

2010-07-28 18:05:14 37

37

37

37乘法器对数运算电路应用

乘法器对数运算电路应用

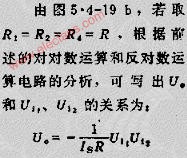

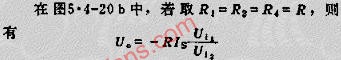

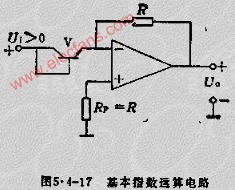

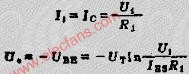

由对数电路实现乘法运算的数学原理是:UO=EXP(INU11+INU12)=U11+U12

图5.4-19示出了满足上式的乘法器的方框

2010-04-24 16:03:19 2115

2115

2115

2115

对数运算电路

对数运算电路

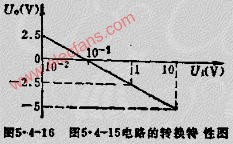

图5.4-15是具有温度补偿和失调的对数运算电路,输入电压10MV~10V,动态范围60DB。V1和V2应当用特性一致结温相同的对管,为了提高精度,V1和V2应

2010-04-23 17:31:43 6561

6561

6561

6561

原码除法运算原理是什么?

原码除法运算原理是什么? 两个原码表示的数相除时,商的符号由两数的符号按位相加求得,商的数值部分由两数的数值部分相除求得。 设有n位定

2010-04-13 11:15:45 11412

11412

11412

11412并行除法器 ,并行除法器结构原理是什么?

并行除法器 ,并行除法器结构原理是什么?

1.可控加法/减法(CAS)单元 和阵列乘法器非常相似,阵列式除法器也是一种并行运算部件,采用大规模集成

2010-04-13 10:46:30 14405

14405

14405

14405模拟信号运算电路基础

模拟信号运算电路基础

7.1 理想运放的概念7.2 比例运算电路7.3 求和电路7.4 积分和微分电路7.5 对数和指数电路7.6 乘法和除法电路

2010-04-13 08:54:20 62

62

62

62TI发布可定制编程的3-PLL时钟合成器乘法器除法器

TI推出的CDC706是目前市场上体积最小且功能强大的PLL合成器/乘法器/除法器之一。尽管其物理外形非常小巧,但却极为灵活。该器件能够在特定输入频率下生成几乎独立的输出频率。

2009-11-26 14:35:47 21

21

21

21 电子发烧友App

电子发烧友App

评论