本内容介绍了DFT可测试性设计的相关知识,并列举了3中常见的可测性技术供大家学习

2012-05-30 16:42:27 6920

6920 TX-6000-DFT-287 - Temperature Compensated Crystal Oscillator - Vectron International, Inc

1970-01-01 08:00:00

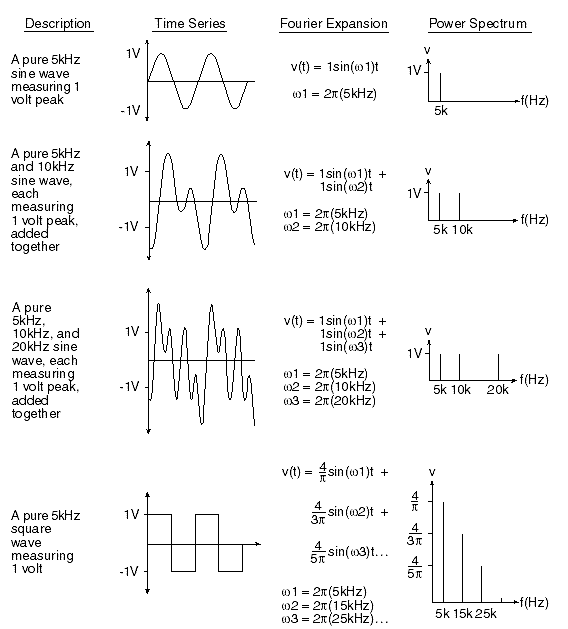

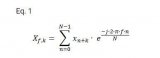

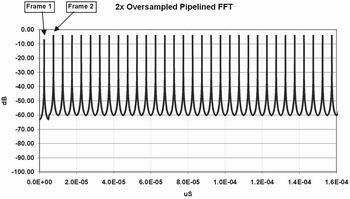

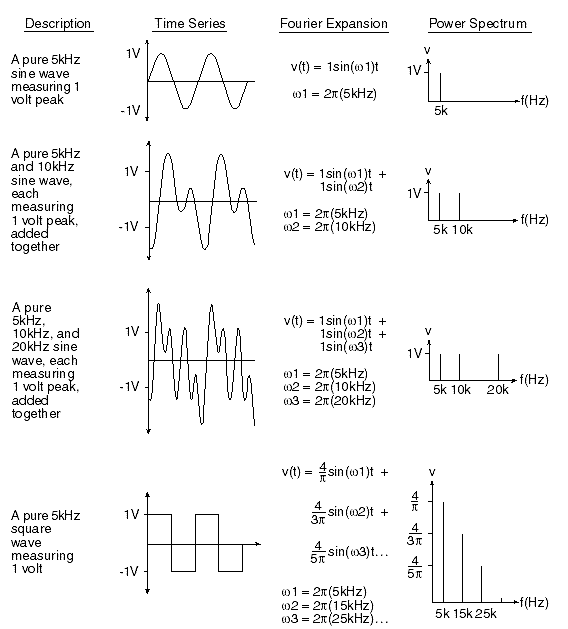

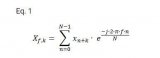

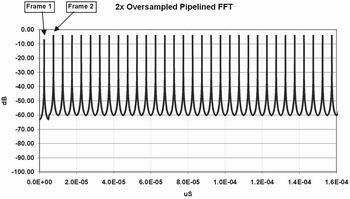

FFT的替代方案是离散傅里叶变换(DFT)。DFT 允许您精确定义计算转换的范围,从而消除了窗口的需要。不利的一面是,DFT的计算速度比FFT慢。

2022-12-02 16:16:09 8186

8186

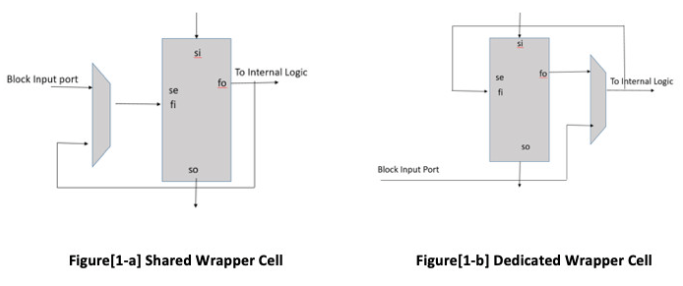

用元素和测试点补充您的操作设计以促进电路板的功能测试被称为可测试性( DFT )设计。 DFT 与制造设计( DFM )不应混淆,尽管两者都是基于 CM 设备和过程能力的设计人员活动。 DFM

2020-10-12 20:42:17 3467

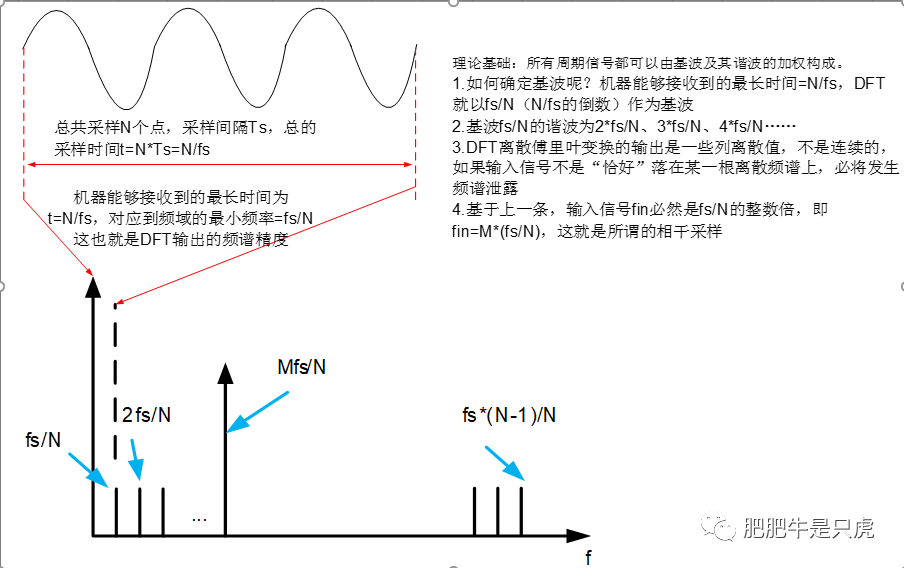

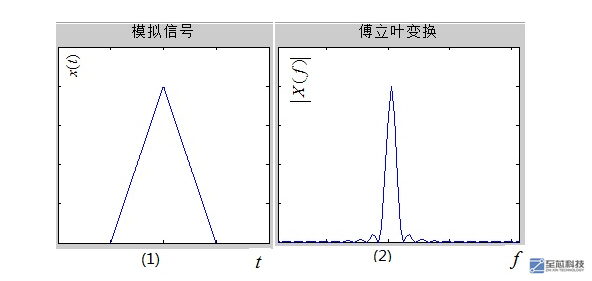

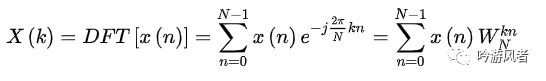

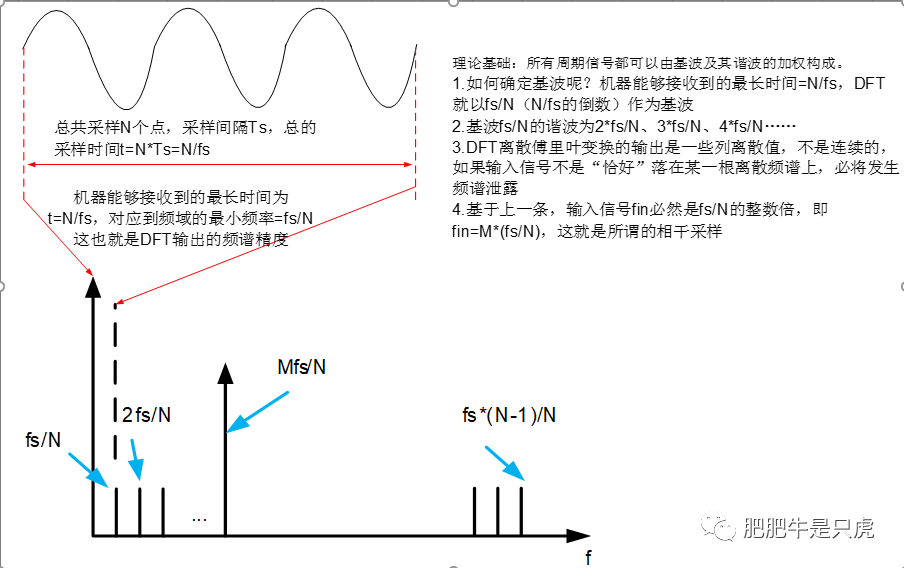

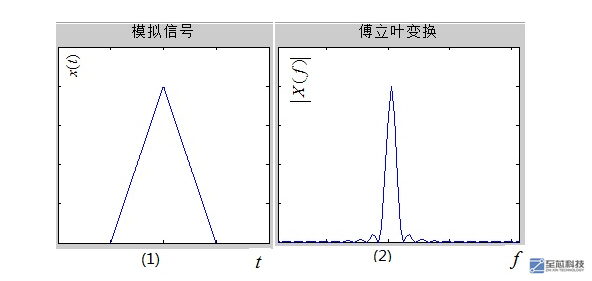

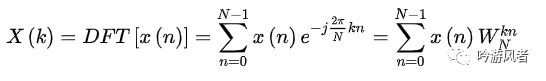

3467 进行计算的,但实际上大多数信号是非周期的,所以会出现在计算FFT时会丢失一些频域信息的情况,进而导致频谱泄露现象。 在理解FFT中的频谱泄露效应时,需要先了解什么是离散傅里叶变换(DFT)。DFT可以将时域上的N个采样点映射到N个相

2023-10-20 15:08:18 89

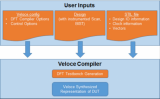

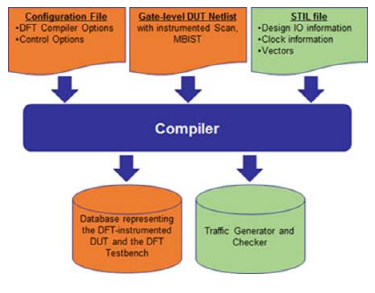

89 在本篇白皮书中,我们介绍了一个典型设计的 DFT 组件,并提出了多种可大幅改善 DFT 项目进度的智能 DFT 方法。我们展示了如何将结构化 DFT 和即插即用原则用于 DFT 基础结构,来支持与其他设计开发工作相似的并行 DFT 开发和集成。

2022-11-30 10:15:00 392

392 DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。DFT不友好的ECO会对芯片的测试和调试带来很大的困难,可能导致芯片测试效率降低甚至无法测试。

2023-05-05 15:06:37 674

674

DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。

2023-03-06 14:47:07 983

983 fft和dft的区别联系 快速傅里叶变换(FFT)和离散傅里叶变换(DFT)是信号处理和数学计算领域中最常见的技术之一。它们都是用于将离散信号从时域转换到频域的方法,而在此转换过程中,它们都利用傅里

2023-09-07 16:43:53 694

694 第3章--离散傅里叶变换(DFT)

2016-12-28 14:23:30 2

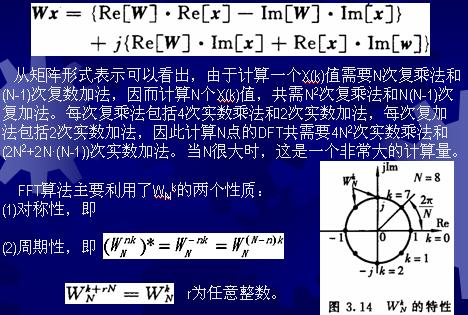

2 首先给大家提供DFT和FFT的运算量的教程,内容有直接用DFT计算运算量与用FFT计算的运算量比较和多种DFT算法(时间抽取算法DIT算法,频率抽取算法DIF算法等.

2011-09-08 00:01:48 71

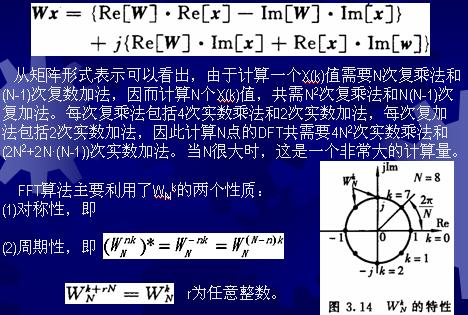

71 DFT在数字信号处理中有很重要的作用,如频谱分析、FIR DF的实现、线性卷积等。一个重要的原因是DFT有高效算法。 为了了解高效算法的重要以及实现高效算法的思路,先介绍DFT的运算特

2011-09-07 23:59:55 57

57 简 介:这学期的信号与系统进展到第五章,拉普拉斯变换与 z 变换。前几天看到一篇博文中对于无限电阻网络求解相邻节点阻抗中使用了离散傅里叶变换 (DFT) 的方法比较新颖。分析了DFT在其中仅仅是起到

2022-08-16 16:26:17 1477

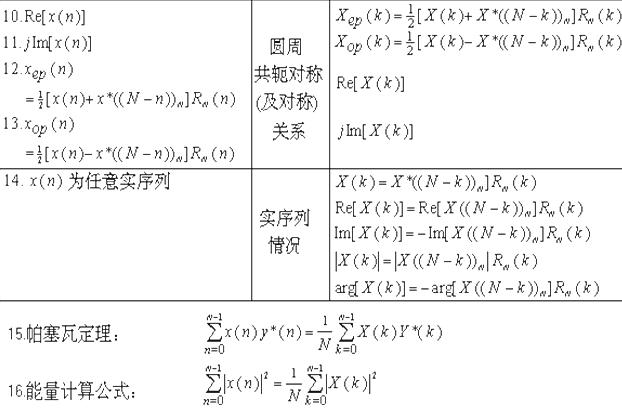

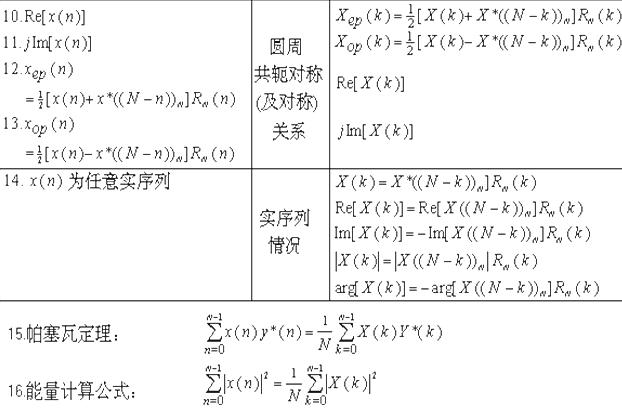

1477 DFT性质一览表

2009-07-25 11:41:03 3822

3822

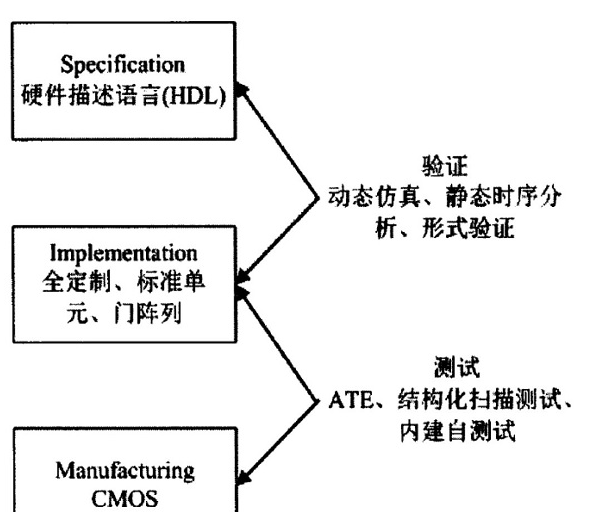

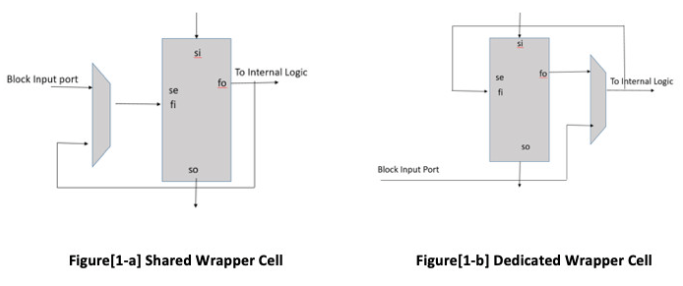

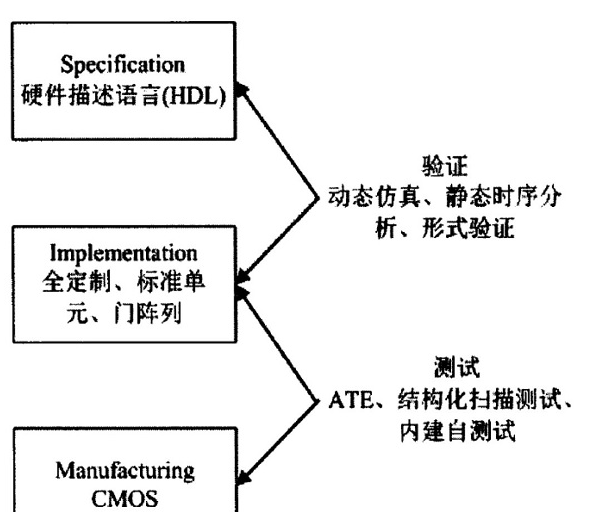

相信很多ICer们在Light芯片的过程中无论前后端都听过DFT设计测试,DFT全称Design for Test(即可靠性设计),众所周知,测试的目的是为了保证芯片成品的质量以及功能逻辑的可靠性的必须 措施。

2023-03-06 14:45:10 1656

1656 英诺达发布了自主研发的静态验证EDA工具EnAltius®昂屹® DFT Checker,该工具可以在设计的早期阶段发现与DFT相关的问题或设计缺陷。

2023-09-13 09:05:18 497

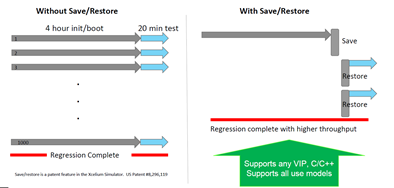

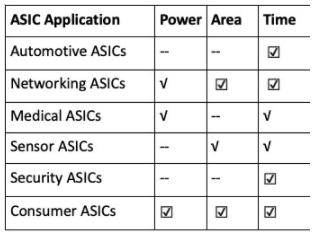

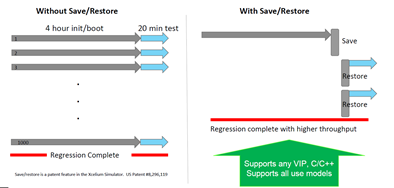

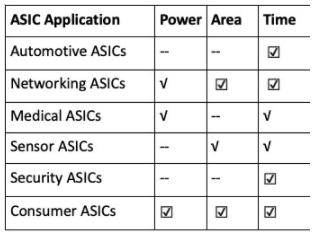

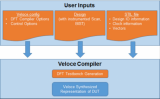

497 当今片上系统的设计复杂性日益增加,可能导致长达数小时、数天甚至数周的可测试性 (DFT) 仿真设计。由于这些往往发生在专用集成电路(ASIC)项目结束时,当工程变更单(ECO)强制重新运行这些长时间

2023-04-20 10:21:24 767

767

应用离散傅里叶变换(DFT),分析离散信号x[k]的频谱。深刻理解DFT分析离散信号频谱的原理,掌握改善分析过程中产生的误差的方法。

2019-08-06 17:16:55 11

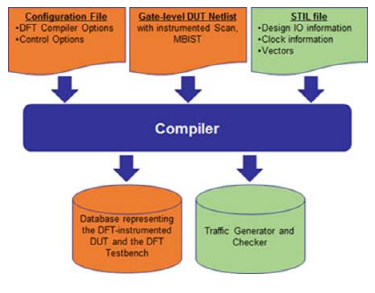

11 随着半导体技术的飞速发展,系统级芯片(SoC)设计已成为现代电子设备中的主流。在SoC设计中,可测试性设计(DFT)已成为不可或缺的环节。DFT旨在提高芯片测试的效率和准确性,确保产品质量和可靠性。

2023-09-02 09:50:10 737

737 基于滑动DFT算法推导出一种改进的周期图功率谱估计方法,并在软件系统界面中应用。根据传统的功率谱估计方法和滑动DFT算法推导出改进的功率谱估计算法,通过滑动DFT算法计算出

2011-09-09 11:02:32 35

35 今天这期小编将继续与大家一起学习DFT的相关知识和流程代码,在开始之前,先解决一下上期DFT学习的章节最后留下的问题—DFT工程师在收敛时序timing的时候经常遇到的hold的问题,即不同时钟域的两个SDFF(扫描单元的SI端hold违例问题。

2023-04-16 11:34:59 2407

2407 DFT 可以降低通过问题器件的风险,如果最终在实际应用中才发现器件有缺陷,所产生的成本将远远高于在制造阶段发现的成本。它还能避免剔除无缺陷器件,从而提高良率。插入 DFT 亦能缩短与测试开发相关的时间,并减少测试装配好的芯片所需的时间。

2019-09-16 14:31:51 1490

1490

为了提高快速移动OFDM系统的信道估计的精度,进一步抑制载波间干扰(ici),本文提出了一种基扩展模型(BEM)联合反馈分组DFT的信道估计算法(BEM+ DFT)。首先,利用BEM算法估计出快速

2017-12-27 11:52:43 3

3 循环卷积DFT的优化算法与仿真_韩芳

2017-03-04 18:08:58 0

0 在前端设计和功能验证之间做对比的情况是很常见的,但随着IC设计业的发展,很多初入行的ICer对其他岗位之间的异同点也很好奇。比如验证和DFT。

2022-12-01 10:09:55 946

946 在芯片做功能ECO时,DFT部分的逻辑常常被破坏,这是由于正常工作模式下修改设计的原因。

2023-03-06 09:15:18 746

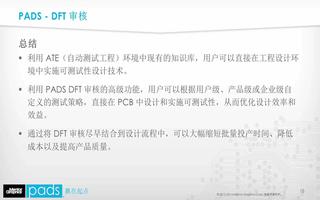

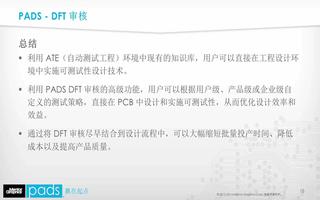

746 通过此视频可快速浏览 PADS DFT 审核的一些主要功能、优点和易用性。在设计流程的早期使用 PADS DFT 审核可大幅降低 PCB 的批量投产时间,确保 100% 的测试点覆盖和制造前所有网络的可测试性。

2019-05-21 08:06:00 2694

2694 如何对一个时域信号(比如ADC输出、一个采样保持电路的输出)做频域DFT线性度分析?

2023-05-23 17:17:13 595

595

DFT的计算量

离散傅里叶变换在实际应用中是非常重要的,利用它可以计算信号的频谱、功率谱和线性卷积等。但是,如果使用定义式(

2008-10-30 12:59:19 4732

4732

PADS 可测试性设计 (DFT) 审核可以缩短上市时间。了解如何尽早在设计流程中利用 PCB 测试点和 DFT 审核优化设计。

2019-05-14 06:26:00 2741

2741

测性设计(DFT)给整个测试领域开拓了一条切实可行的途径,目前国际上大中型IC设计公司基本上都采用了可测性设计的设计流程,DFT已经成为芯片设计的关键环节。

2020-07-06 11:38:47 8847

8847

该文利用参数估计方差最小为优化准则,计算出多频正弦信号分段WDFT(Windowed-DFT)相位加权平均相位估计算法的最优加权系数,并给出算法相位估计的方差公式。另外,该文对DFT“噪

2009-11-09 14:47:17 15

15 现今流行的可测试性设计(DFT:Design For Testability)为保证芯片的良品率担任着越来越重要的角色。

2012-04-20 09:39:05 6090

6090

第2章-离散傅里叶变换(DFT)及其快速算法(FFT)

2016-12-28 14:23:30 6

6 OFDM的调制技术及DFT实现:正交频分复用(OFDM)技术的应用已有近40 年的历史,但直到70 年代,人们采用了离散傅立叶变换来实现多个载波的调制,简化了系统结构,使得OFDM技术更趋

2009-06-15 07:49:30 30

30 离散傅里叶变换,(DFT)Direct Fouriet Transformer(PPT课件)

一、序列分类对一个序列长度未加以任何限制,则一个序列可分为: 无限长序列:n=-∞~∞或n=0~∞或n=-

2009-07-25 11:38:17 117

117 在本文中,我们检查了扫描压缩确实有助于减少 ASIC 设计中的测试时间 (DFT),但扫描通道减少也是一种有助于顶层测试时间的方法。

2022-06-02 14:25:09 1209

1209

滑动DFT的推导是相当简单的,并且和DFT完全等价。也就是说,滑动DFT算法相比传统DFT或FFT算法没有信息丢失或失真。下面有完整的推导过程,没有兴趣的读者可以跳过这一节,因为它容易让人想睡

2018-02-19 01:01:00 9486

9486

Ad-hoc DFT 包括一套提倡“良好”设计规范的规则,旨在简化和加速测试流程。例如,提供置位和复位信号,使得所有触发器均可初始化;避免引起振荡的异步逻辑反馈;逻辑门设计应注意避免扇入数过大(扇入

2018-04-12 14:29:00 2558

2558

数字信号处理第3章-离散傅里叶变换(DFT)

2016-12-28 14:23:30 0

0 数字信号处理(第三章-离散傅里叶变换DFT)

2016-12-28 14:23:30 0

0 对于过渡族金属元素主要是3d族,当然也包括4d,5d族,和稀土元素,主要是镧系;这些元素形成的合金或者化合物中,由于存在d电子或f电子,而这两种电子都是强关联电子,在某些时候,传统的DFT没法描述

2022-08-17 14:54:08 988

988 电子发烧友网为你提供ON Semiconductor(ti)NLSX4401DFT2G相关产品参数、数据手册,更有NLSX4401DFT2G的引脚图、接线图、封装手册、中文资料、英文资料,NLSX4401DFT2G真值表,NLSX4401DFT2G管脚等资料,希望可以帮助到广大的电子工程师们。

2019-08-03 04:02:19

一种基于改进DFT算法的相位差测量研究_陈孔阳

2017-03-19 11:46:13 1

1 在芯片做功能ECO时,DFT部分的逻辑常常被破坏,这是由于正常工作模式下修改设计的原因。

2023-02-22 11:37:12 284

284 数字信号处理[第三章-离散傅里叶变换(DFT)]

2016-12-28 14:23:30 1

1 数字信号处理--第3章--离散傅里叶变换(DFT)

2016-12-28 14:23:30 0

0 摘要:本文简要地论述了FFT和多相位DFT滤波器组在响应方面的差异。一般而言,多相位DFT(甚至包括任何滤波器组,比如PFT)在稳态条件下有着很好的相邻信道抑制性能,而瞬态响应却很糟糕。这符合了滤波器冲激响应结论。

2006-03-11 13:17:03 1898

1898

均衡技术是在接收端消除无线多径衰落信道引起的码间干扰的重要手段。介绍了一种利用单点DFT运算进行均衡的算法,讨论了在对该算法进行定点仿真中遇到的几个问题,最后给出了浮

2011-09-16 14:36:28 35

35 近日,西门子旗下业务Mentor宣布推出一种创新的可测试性设计 (DFT) 自动化方法 — Tessent Connect,可提供意图驱动的分层测试实现。与传统的 DFT 方法相比,该方法可帮助 IC 设计团队以更少的资源实现更快的制造测试质量目标。

2019-12-04 15:54:49 3321

3321 的计算能力和相当多的时间。分层可测试性设计通过在区块或内核上完成了 DFT 插入和图案生成解决了这个问题。

2018-01-31 07:06:09 10501

10501

NC_OFDM系统基于DFT_DCB降PAPR研究_朱志成

2017-02-28 20:38:20 0

0 大家好,又到了每日学习的时间了,今天咱们来聊一聊数字信号处理中DFT、DTFT和DFS的关系,咱们通过几幅图来对比,探讨一下哦。 很多同学学习了数字信号处理之后,被里面的几个名词搞的晕头转向,比如

2018-06-11 15:15:11 10962

10962

DFT(Discrete Fourier Transform)代表着离散傅里叶变换,是作为有限长序列的在数字信号处理中被广泛使用的一种频域表示方法。

2023-08-09 11:26:36 565

565

可测试性设计 (DFT) 在市场上所有的电子设计自动化 (EDA) 工具中是最不被重视的,纵然在设计阶段提高芯片的可测试性将会大幅缩减高昂的测试成本,也是如此。最近的分析数据表明,在制造完成后测试

2017-11-28 11:28:38 0

0 香山处理器的第二代微架构,南湖微架构,引入了L3 Cache,可配置多核形态,我们完成流片的是双核版本的南湖。较第一代雁栖湖,设计规模在大幅膨胀,主频也从1.3GHz提升到2GHz。规模化之后对DFT设计及物理实现都造成新的挑战,我们的设计方法学也需要与时俱进。

2022-12-14 10:51:16 921

921 本文档的主要内容详细介绍的是数字信号处理教程之DFT和FFT处理的学习课件免费下载包括了:1.离散傅里叶变换,2.与傅里叶变换的关系,3.与傅里叶级数的关系,4.DFT 窗效应,6.快速傅里叶变换。

2019-11-13 17:08:16 12

12 DFT 伪码捕获算法在进行伪码搜索的同时估计多普勒频偏,为了满足捕获精度要求,需要增加DFT 点数,但随着运算点数的增加硬件实现难度成倍增长。本文提出一种基于FPGA 的在不

2009-09-22 09:59:21 12

12 高级测试设计 (DFT) 技术通过提高顺序翻牌的可控性和可观察性,提供高效的测试解决方案,以应对更高测试成本、更高功耗、测试面积和较低几何尺寸下的引脚数。这反过来又提高了SoC的良率,可靠性和可测试性是当今ASIC世界的重要因素。

2022-11-23 14:53:53 529

529

中,被授予该奖项的三大产品之一,它帮助 Mentor 抢占了 DFT 市场的老大位置。我们对创新大小的定义,不仅仅体现在它对产品本身的影响,更要能体现在该产品带来的商业价值和市场份额上。

2019-10-11 15:59:30 2690

2690 的电性参数发生偏移,扫描链测试失败。这对DFT(Design for Test)以及ATPCJ(Automatic Test Pattern Ceneration)提出了更高的挑战。

2017-11-11 16:20:38 4

4 ASIC设计的平均门数不断增加,这迫使设计团队将20%到50%的开发工作花费在与测试相关的问题上,以达到良好的测试覆盖率。尽管遵循可测试设计(DFT)规则被认为是好做法,但对嵌入式R

2011-05-28 11:56:59 1308

1308

电子发烧友App

电子发烧友App

评论