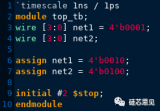

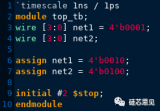

在Verilog和SystemVerilog中经常需要在使用变量或者线网之前,期望变量和线网有对应的初始值

2023-08-25 09:47:56 264

264

SystemVerilog 的VMM 验证方法学教程教材包含大量经典的VMM源代码,可以实际操作练习的例子,更是ic从业人员的绝佳学习资料。SystemVerilog 的VMM 验证方法学教程教材[hide][/hide]

2012-01-11 11:21:38

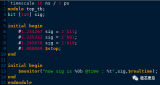

在SystemVerilog中,输出信息显示时间时,经常会在输出信息格式中指定“%t”格式符,一般情况下“%t”输出的格式都是固定的,但是这样固定的输出显示的时间可能有时会让用户看起来感觉比较诧异,例如下面的示例。

2023-08-16 09:41:58 297

297

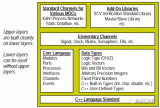

SystemC是基于C++的系统级设计语言,兼具描述硬件电路模型和面向对象的抽象能力。

2023-08-07 09:43:45 306

306

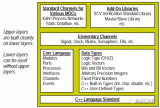

SystemVeirlog的全面支持是开发商用仿真器的第一道门槛。市面上可以找到不少基于纯Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可数。如何全面地支持SystemVerilog语言,是开发仿真器的一个重要任务。

2023-07-14 15:15:25 191

191

本文讲一下SystemVerilog的time slot里的regions以及events的调度。SystemVerilog语言是根据离散事件执行模型定义的,由events驱动。

2023-07-12 11:20:32 471

471

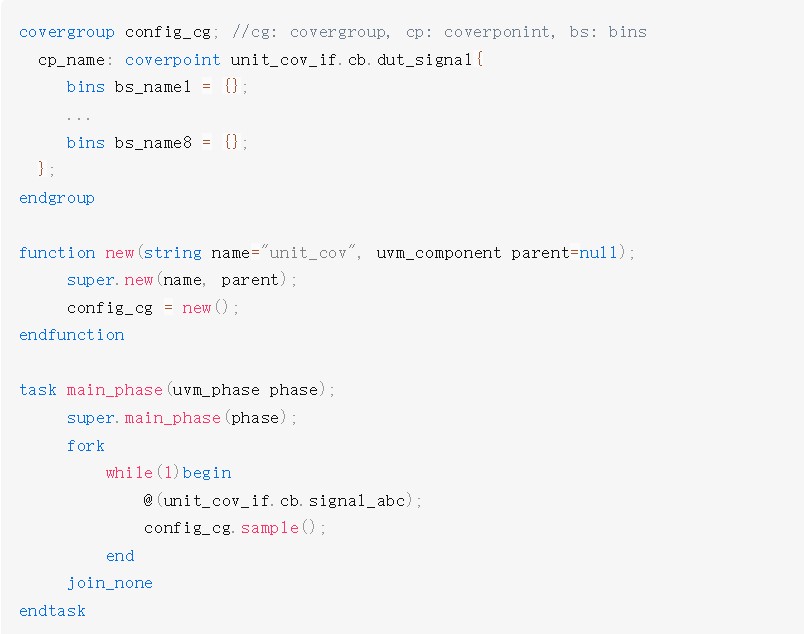

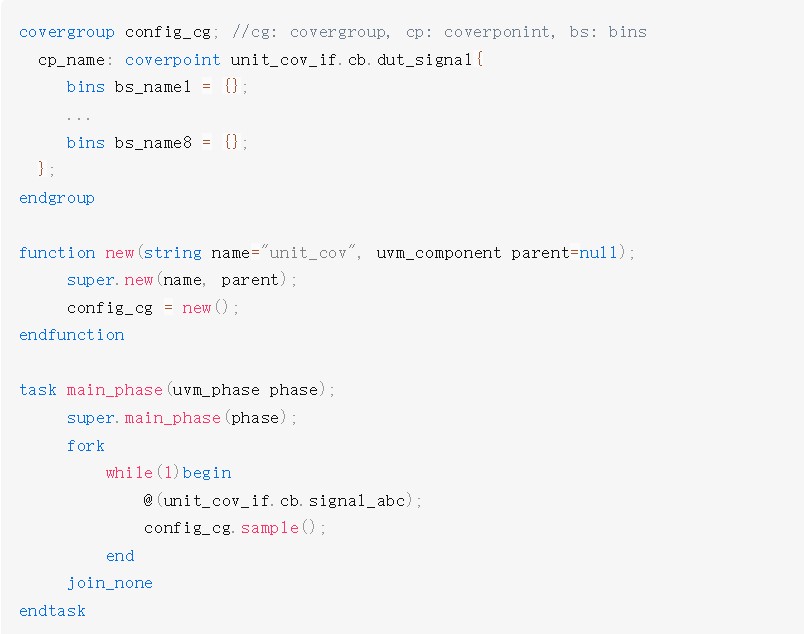

为了确保验证的完备性,我们需要量化验证目标。SystemVerilog提供了一套丰富的覆盖率建模方式。

2023-06-25 10:44:16 294

294 在systemverilog中,net用于对电路中连线进行建模,driving strength(驱动强度)可以让net变量值的建模更加精确。

2023-06-14 15:50:16 434

434

在SystemVerilog中,我们知道可以使用动态数组实现数组元素个数的动态分配,即随用随分

2023-06-09 09:46:24 1541

1541

SystemVerilog是一名芯片验证工程师,必须掌握的一门语言,其中Function Coverage是必须要懂的知识点之一;

2023-06-04 16:30:24 1891

1891

我们在工作中常常会针对数组施加各式的约束,下面列举一下有趣的**Systemverilog数组约束**示例

2023-05-30 11:13:21 243

243 写过Verilog和systemverilog的人肯定都用过系统自定义的函数$display,这是预定好的,可以直接调用的功能。

2023-05-16 09:27:02 382

382

SystemVerilog Interface是modport的一种,但比简单的输入、输出或输入输出端口的功能更多。

2023-04-28 14:12:22 1225

1225

SystemVerilog Interface是modport的一种,但比简单的输入、输出或输入输出端口的功能更多。

2023-04-28 14:10:06 740

740

数独是一种非常流行的游戏,数独本质上也是一个约束问题,所以我们可以让SystemVerilog的约束求解器来帮助我们解决。 约束求解器的精妙之处就是,我们只描述约束限制,繁重的数值生成工作由工具来帮我们完成。 你只需“既要...又要...”,其他的让下人干吧。

2023-03-08 14:06:00 630

630 我们在工作中常常会针对数组施加各式的约束,下面列举一下有趣的Systemverilog数组约束示例。

2023-03-08 13:12:00 373

373 上一篇文章介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-01-21 17:03:00 981

981 SystemVerilog中Semaphore(旗语)是一个多个进程之间同步的机制之一,这里需要同步的原因是这多个进程共享某些资源。

2022-12-12 09:50:58 1712

1712 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了 C语言 数据类型、结构、压缩和非

2022-12-08 10:35:05 935

935 SystemVerilog中可以将类属性声明为常量,即“只读”。目的就是希望,别人可以读但是不能修改它的值。

2022-11-29 10:25:42 1393

1393 SystemVerilog中多态能够工作的前提是父类中的方法被声明为virtual的。

2022-11-28 11:12:42 358

358 要想理解清楚SystemVerilog语言中的Upcasting和Downcasting概念,最好的方式从内存分配的角度理解。

2022-11-24 09:58:15 625

625 SystemVerilog中的句柄赋值和对象复制的概念是有区别的。

2022-11-21 10:32:59 378

378 在systemverilog中,如果一个类没有显式地声明构造函数(new()),那么编译仿真工具会自动提供一个隐式的new()函数。这个new函数会默认地将所有属性变量。

2022-11-16 09:58:24 2400

2400 SystemVerilog union允许单个存储空间以不同的数据类型存在,所以union虽然看起来和struct一样包含了很多个成员,实际上物理上共享相同的存储区域。

2022-11-09 09:41:28 440

440 SystemVerilog“struct”表示相同或不同数据类型的集合。

2022-11-07 10:18:20 1512

1512 SystemVerilog packages提供了对于许多不同数据类型的封装,包括变量、task、function、assertion等等,以至于可以在多个module中共享。

2022-11-07 09:44:45 693

693 SystemVerilog中除了数组、队列和关联数组等数据结构,这些数据结构还可以嵌套。

2022-11-03 09:59:08 915

915 SystemVerilog提供了几个内置方法来支持数组搜索、排序等功能。

2022-10-31 10:10:37 1320

1320 学习Systemverilog必备的手册,很全且介绍详细

2022-10-19 16:04:06 2

2 SystemVerilog casting意味着将一种数据类型转换为另一种数据类型。在将一个变量赋值给另一个变量时,SystemVerilog要求这两个变量具有相同的数据类型。

2022-10-17 14:35:40 1571

1571 event是SystemVerilog语言中的一个强大特性,可以支持多个并发进程之间的同步。

2022-10-17 10:21:33 772

772 Block,也就是语句块,SystemVerilog提供了两种类型的语句块,分别是begin…end为代表的顺序语句块,还有以fork…join为代表的并发语句块。

2022-09-14 10:27:30 713

713 HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

2022-08-31 09:06:59 937

937 IEEE SystemVerilog标准:统一的硬件设计规范和验证语言

2022-08-25 15:52:21 0

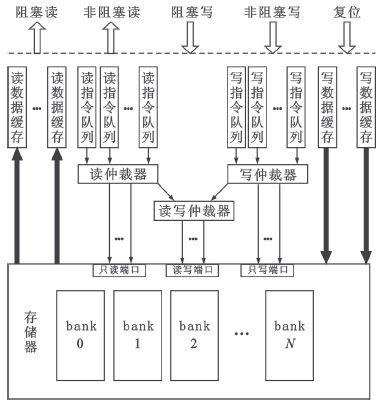

0 利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 2

2 本文定义了通常用于描述使用SystemVerilog对硬件功能进行建模的详细级别的术语。

2022-03-30 11:42:02 1151

1151 作者:limanjihe https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一种硬件描述和验证语言

2021-10-11 10:35:38 1882

1882 手册的这一部分探讨了使用SystemVerilog进行验证,然后查看了使用SystemVerilog的优点和缺点。

2021-03-29 10:32:46 22

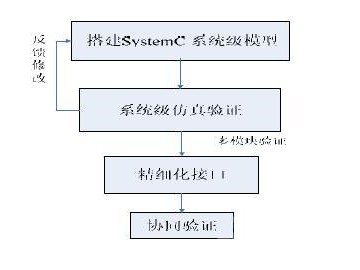

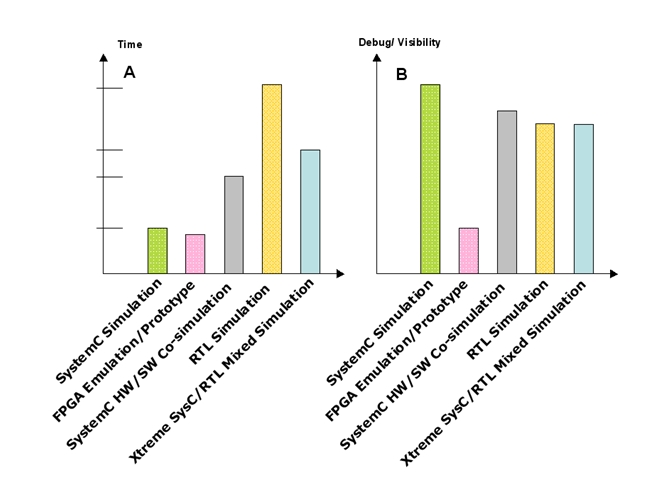

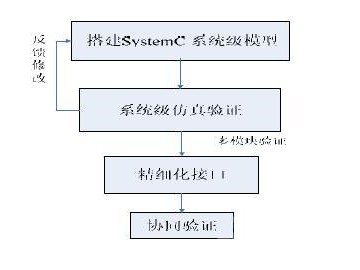

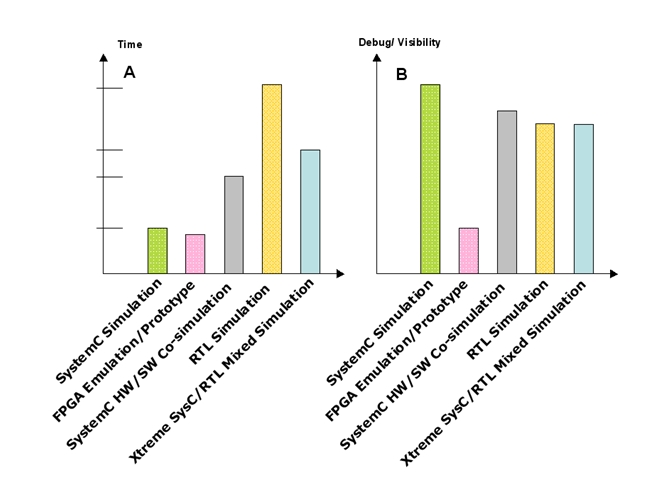

22 支持SystemC的电子系统级(ESL)设计和验证环境旨在设计,分析,优化和验证片上系统(SoC)平台模型。这样的环境构成了已建立的RTL实现流程的前端。

2019-10-03 17:05:00 4189

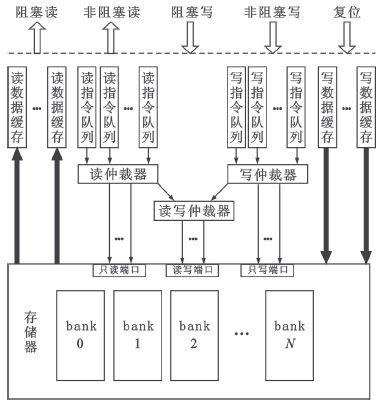

4189 硬件建模。但是随着软硬件复杂度的提高,C/C++语言难以再满足要求。OSCI适时推出了SystemC语言来适应新的需求。如今SystemC已经被广泛应用于SoC软硬件建模中。

2018-12-05 07:43:00 5041

5041

SystemC 是由C++衍生而来,本质是在C++的基础上添加了硬件扩展库和仿真核,这使SystemC 可以在不同抽象级对复杂电子系统建模。

2018-07-19 11:55:00 4496

4496

基于SystemC构建多核DSP软件仿真平台_韦祎

2017-01-03 17:41:32 3

3 systemc语言简单介绍,有助于初学者更好的运用和了解

2015-12-07 10:33:57 4

4 为了实现软硬件协同设计和提高仿真速度的需求,采用SystemC语言的建模方法,通过对片上网络体系结构的研究,提出了一种片上网络的建模方案,并对一个mesh结构完成了SystemC的建模设

2013-07-30 11:46:44 42

42 在介绍SystemVerilog 断言的概念、使用断言的好处、断言的分类、断言的组成以及断言如何被插入到被测设计(DUT)的基础上,本文详细地介绍了如何使用不同的断言语句对信号之间的复

2011-05-24 16:35:19 36

36 本内容提供了SystemC片上系统设计及源代码 #include scv.h #include fifo_mutex.h class rw_task_if : virtual public

2011-05-10 15:32:40 100

100 文章主要介绍《VMM for SystemVerilog》一书描述的如何利用SystemVerilog语言,采用验证方法学以及验证库开发出先进验证环境。文章分为四部分,第一部分概述了用SystemVerilog语言验证复杂S

2011-05-09 15:22:02 51

51 SystemVerilog 是过去10年来多方面技术发展和实际试验的结晶,包括硬件描述语言(HDL)、硬件验证语言(HVL)、SystemC、Superlog和属性规范语言。它们都从技术和市场的成败中得到了丰富的经

2010-09-07 09:55:16 1075

1075 随着项目复杂程度的提高,最新的系统语言的聚合可以促进生产能力的激增,并为处在电子设计自动化(EDA)行业中的设计企业带来益处。SystemVerilog和SystemC这两种语言在设计流

2010-08-25 09:44:47 1119

1119 数字专用集成电路设计中的SystemC建模验证方法

2010-07-17 16:36:23 31

31 视频编解码芯片中运动估计与补偿单元(MECU)的算法复杂,使用传统硬件描述语言建立模型和模型验证的过程繁琐耗时,为了缩短芯片验证时间,本文针对MECU模块提出了基于SystemC语言

2010-02-24 12:07:21 16

16 如何采用SystemVerilog 来改善基于FPGA 的ASIC 原型关键词:FPGA, ASIC, SystemVerilog摘要:ASIC 在解决高性能复杂设计概念方面提供了一种解决方案,但是ASIC 也是高投资风险的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 利用基于SystemC/TLM的方法学进行IP开发和FPGA建模

随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已

2010-01-04 13:11:50 5058

5058

本文利用形式化的方法对SystemVerilog的指称语义进行研究,采用EBES(extendedbundle event structure)作为抽象模型,以便更好的描述SystemVerilog真并发的特点。我们的主要工作是:首先,

2009-12-22 14:01:07 12

12 事务级(Transaction-Level,TL)建模是SystemC 中提出的一种新型高层次建模方法,以CoCentric System Studio(CCSS)作为SystemC 仿真工具,以一个IP 路由系统为建模实例,分析了事务级建模

2009-07-30 15:27:27 24

24 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1: A

2009-07-22 14:48:12 115

115 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1: A

2009-07-22 14:45:34 20

20 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 19

19 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 This time, we have responded to a growing interest not

only in object-oriented programming but also in SystemVerilog. The w

2009-07-20 09:26:57 30

30 This time, we have responded to a growing interest not

only in object-oriented programming but also in SystemVerilog. The w

2009-07-20 09:24:47 35

35 Systemc From The Ground Up:The first question any reader should ask is “Why this book?” We

2009-07-10 17:27:57 36

36 IC 技术已发展到SoC 阶段,系统级设计、仿真和验证已成为IC 设计面临的巨大挑战。SystemC 是新兴的系统级设计语言,为复杂系统的设计与验证提供了解决方案。本文介绍SystemC 的特点

2009-05-18 13:44:58 27

27 decided

to write this book after learning SystemC and after using minimal documents

to help us through the quest of bec

2009-02-12 09:30:34 45

45

电子发烧友App

电子发烧友App

评论