摘要

在SoC设计中,EDA工具处理完网络列表之后插入的逻辑均被称作ECO。可以不必进行合成、地点和路线、提取、串音等整个SoC设计周期,从而节省完成ECO的时间。可以采用省钱方式来执行后掩膜工程变更清单。 如果只修改少量金属层就能完成一项更改,那么涉及的成本要比将整个设计完全重做少得多。 ECO通常会使用到备用门模块(在合成期插入)。通常,这些备用门模块包括NAND、NOR、 触发器、 缓冲器、逆变器以及其他可能使用到的逻辑单元。 本文重点介绍如何使用现有布局的缓冲器/逆变器(对)逻辑,使用备用单元模组来避免违反设计(DRV)规则。

介绍

实施工程变更订单(ECO),是片上系统(SoC)设计阶段十分常用的一个步骤。 在设计中采用ECO的原因有很多。

1.事先规划好的ECO: 有时候,设计人员可以预先设定好采用ECO。 例如,有时候可能有这种情况:在ASIC设计周期的后期需要引入IP,因此设计人员要对其活动进行适当规划,以免设计阶段受到限制。 但有说法认为在设计周期中采用ECO,大部分属于偶然。

2.功能性修改: ECO也可能是设计规范需要进行功能性修改的结果,如果客户需要附加功能或者应用软件要求硬件部署该功能,那就有可能需要进行此类修改了。

3.设计问题: 门级模拟(GLS)或类似技术中一些先前的测试芯片的硅结果中可能会出现设计问题。

要在逻辑门里实施ECO,设计人员需要一个最佳解决方案,因为增加额外的门可能导致要再制造基础层(如激活层、多晶硅层、氮化物层)掩膜,这比互连掩膜的成本高得多。 因此理想的情况是,设计人员会希望只包含使用现有逻辑的逻辑,来减少因再制造产生的成本。

问题陈述:

使用额外的逻辑门来包含ECO,可能会对整个时序及设计的可路由性产生影响,具体来说,当ECO逻辑相当大时,受到影响的模块实施密度将达到100%。

现行方法:

当前针对该问题所采取的解决方法是在设计的物理合成阶段,在每个模块内添加额外的门,因此在执行ECO时,现有的备用门在以后可以用来包含设计中的修改。这样就不必增加更多的逻辑。 但这种方法具有一定的局限性。

现行方法的局限:

1.设计人员不能预测一个模块的最佳备用门数量,以避免ECO的中途中止; 例如,假设功能性ECO需要在一个链里连接10个缓冲器。 但现有的备用单元模组只有6个缓冲器,由于没有缓冲器/逆变器(对)所以我们必须重新转动SoC。基本上,这个局限在于设计人员必须要在一个模块中放置更多冗余逻辑,或在另一个模块中备用放置有限的备用门。

2. 规模过大的ECO必然会违反保持时间并违反设计规则,例如违反逻辑门的最大过渡或最大驱动强度。 这需要额外的冗余缓冲器来解决保持时间违反问题,或提高DRV易发生的信号压摆率性能。

建议的解决方案:

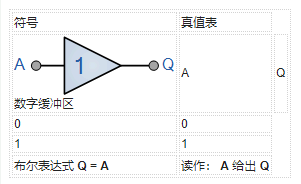

本文欲介绍一款我们可以使用现有布局来省去缓冲器/逆变器(对)的解决方案。

请记住,在备用规模块中,可能必须增加冗余的NAND/NOR门和额外的触发器/闩锁,但不一定需要增加冗余的缓冲器和逆变器。

基本上,本文试图演示一种创新方法,它使用优化技术,可从现有布局恢复缓冲器/逆变器逻辑。

算法和伪代码

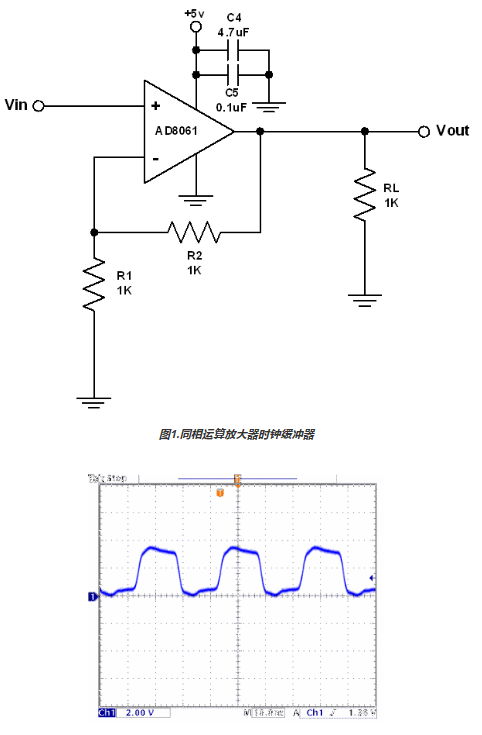

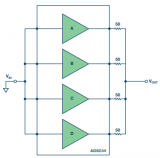

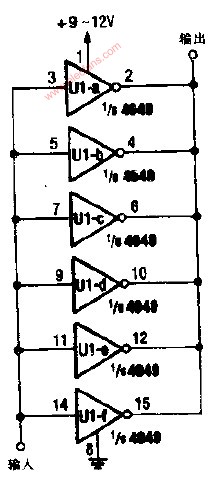

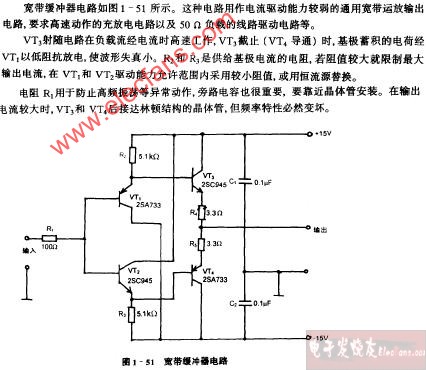

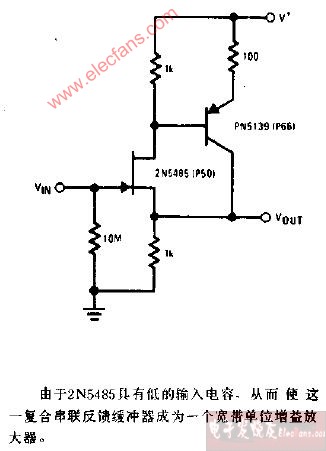

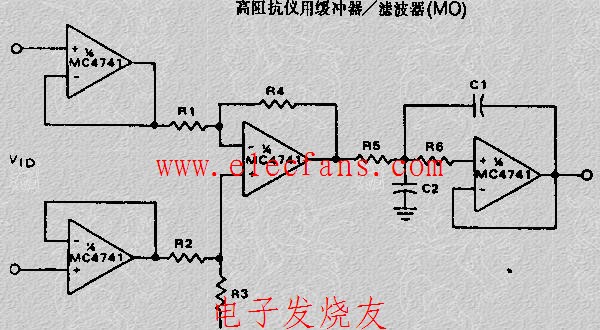

图1: 一个(x1,y1,x2,y2)窗口大小所要实施的基本算法

生成窗口大小的伪代码:

开头

x=x1;y=y1;

当 x < x2,

y < y2时

x’ = x + a, y’ = y + b;

x=x’,y=y’

如果 x > x2 或 y > y2

x=x2, y="y2";

结束

生成的每个窗口坐标用 (x, y, x’, y’)表示

此处a、b需要根据具体的设计和技术而定。 如果SoC的SoG(Sea of Gates)区域是 7 mm2 或更大,设计人员在计算窗口大小时需要注意计算的复杂性。

描述:

如上面的流程图所示,该思路的核心是如何识别非关键性的缓冲器(w.r.t时序余量)。 在实施ECO时,我们不可避免地需要使用备用单元模组的缓冲器。 现在,这个缓冲器的放置是比较随意的,使用它会违反DRV规则。

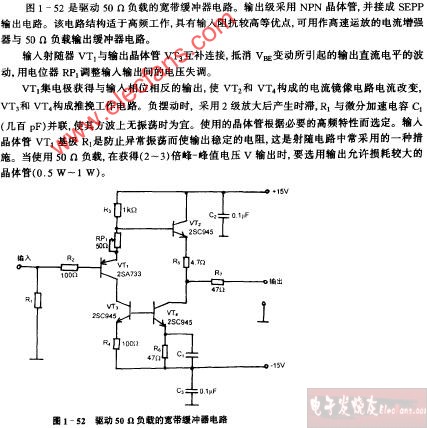

例如,我们假设使用BUFX8来驱动5个扇出。总的容量负荷(包括线路和引脚)是200fF。现在根据该缓冲器的SPICE特征,任何高于150fF的负荷都会导致不好的输出压摆。差的输出压摆不仅会违反最大过渡值,而且还会影响扇出驱动电路的时序。

因此,在这种情况下,明智的做法是遵从上面的算法,这样我们可以进行以下步骤:

1.找出ECO的目标点: 我们应当找出开始点和结束点位置,这是放置缓冲器元件的位置。该位置决定着窗口大小,我们应当在这个窗口里搜索非关键性缓冲器/逆变器(对)。

2.决定窗口大小: 这完全由设计人员决定。 他可以根据技术选择窗口大小。如果缓冲器能驱动的最大负荷是200fF,那么窗口大小应当相应地进行修改。

3.缓冲器/逆变器(对)的识别: 现在,该算法将在特定窗口上运行,并且尝试识别已标记位置中出现的所有缓冲器/逆变器(对)。

4.计算时序余量: 一旦缓冲器/逆变器(对)做了标记,算法应尝试通过这些标准单元找出时序余量。如果这些标准单元对时序很关键,那么该缓冲器/逆变器(对)就不需要标记。只要该缓冲器/逆变器(对)保留为标记状态,那么取消哪一个都不会对该设计的现有时序情况产生影响。

5.最后一步: 现在,带标记的缓冲器/逆变器(对)可以用于ECO。

结论

布局优化和冗余单元的使用可以帮助设计人员在以后数百万个门SOC的设计阶段,消化复杂的ECO,同时避免对整个产品的上市时间造成影响。

电子发烧友App

电子发烧友App

评论