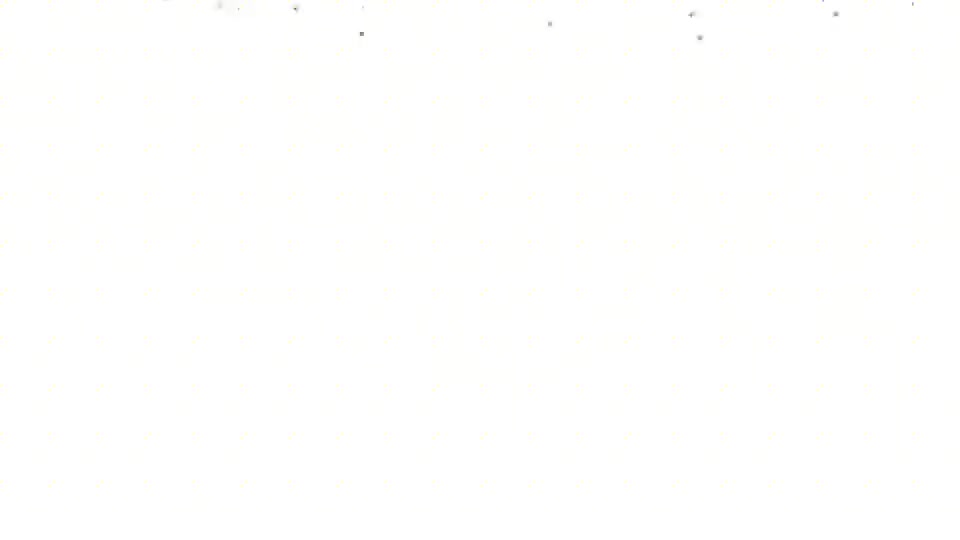

FinFET立体晶体管技术是Intel 22nm率先引用的,这些年一直是半导体制造工艺的根基,接下来在Intel 20A、台积电2nm、三星3nm上,都将转向全环绕立体栅极晶体管。

2023-10-23 11:15:08 59

59

; 晶体管,本名是半导体三极管,是内部含有两个PN结,外部通常为三个引出电极的半导体器件。它对电信号有放大和开关等作用,应用十分广泛。输入级和输出

2010-08-12 13:57:39

最近有许多正在全球范围内研究和开发的技术,例如晶体管GAA(Gate All around)、背面供电以及3D IC。

2023-07-26 18:21:58 998

998

在半导体行业的最初几十年里,新的工艺节点只需缩小晶体管的物理尺寸并将更多晶体管塞到芯片上即可实现性能、功耗和面积增益,这称为经典缩放。集成电路工作得更好,因为电信号在每个晶体管之间传播的距离更短。

2023-07-16 15:47:43 253

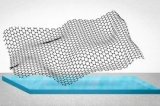

253 然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

2023-05-31 15:45:29 975

975

然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

2023-05-30 14:24:48 1116

1116

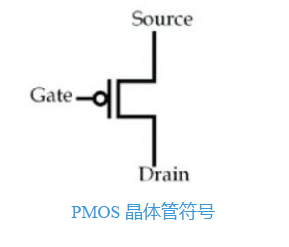

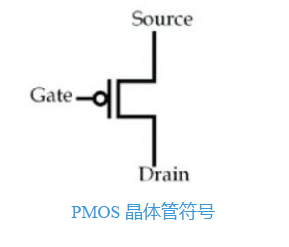

PMOS晶体管,也称为P沟道金属氧化物半导体,是一种晶体管形式,其中沟道或栅极区域使用p型掺杂剂。这个晶体管与NMOS晶体管完全相反。这些晶体管包含三个主要端子:源极、栅极和漏极。晶体管的源极端子由

2023-02-11 16:48:03 8728

8728

场效应晶体管的源极、漏极和栅极分别相当于晶体管的发射极、集电极和基极。对应于晶体管放大电路,场效应晶体管放大电路也有三种组态:共源极放大电路、共漏极放大电路和共栅极放大电路,其特点分别和晶体管放大电路中的共射极、共集电极、共基极放大电路类似。

2022-11-30 09:30:00 1635

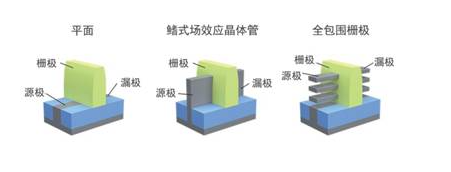

1635 BSPDN可以理解为Chiplet技术的演变(图自:IMEC) 目前主流的 FinFET(过去被称为 3D 晶体管)是 10nm 工艺发展过程中的关键芯片设计技术,采用三面包覆式的栅极设计,可以在三个侧面围起电流通道,以此减少漏电流(电子泄露)。

2022-11-11 14:42:53 570

570 在了解mos管栅极电阻的作用之前,我们先了解一下mos管栅极及其他2个极的基础知识。场效应管根据三极管的原理开发出的新一代放大元件,有3个极性,栅极,漏极,源极,它的特点是栅极的内阻极高,采用

2022-09-27 15:29:50 5811

5811 FinFET在22nm节点的首次商业化为晶体管——芯片“大脑”内的微型开关——制造带来了颠覆性变革。与此前的平面晶体管相比,与栅极三面接触的“鳍”所形成的通道更容易控制。但是,随着3nm和5nm技术节点面临的难题不断累积,FinFET的效用已经趋于极限。

2022-08-01 15:33:11 799

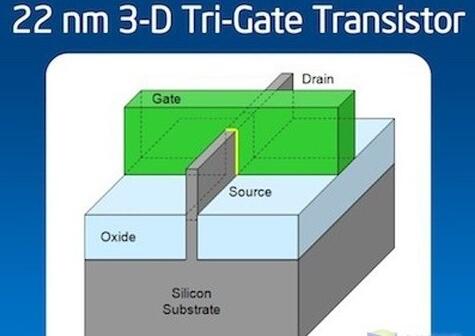

799 FinFET确切的说,是一个技术的代称。世界上第一个3D三维晶体管是由英特尔在2011年5月宣布研制成功,当时英特尔称其为 “Tri-Gate”(三栅极晶体管)。

2022-07-08 15:04:26 1549

1549 北斗星通的22nm工艺的全系统全频厘米级高精度GNSS芯片,在单颗芯片上实现了基带+射频+高精度算法一体化。

2022-07-04 15:53:48 1290

1290 现在的芯片技术越来越先进,人们常常能够听到某某公司又研发出5nm、4nm芯片的消息,而目前全球所研发出的最先进的芯片是IBM公司的2nm芯片,我们都知道芯片内部有很多晶体管,那么2nm芯片的晶体管

2022-07-04 09:15:36 3450

3450 日前,三星放出了将在6月30日正式量产3nm芯片的消息,今天上午,三星官方宣布已经开始了3nm工艺芯片的量产。 三星官方称,其采用了GAA晶体管的3nm工艺芯片已经在韩国华城工厂开始量产。 现在全球

2022-06-30 16:36:27 1768

1768 的技术呢? 据了解,全球芯片巨头Intel在2011年发布了22nm工艺,而在2012年第三季度,台积电也开始了22nmHP制程的芯片研发工作,因此可得出22nm芯片最早在2011年被发布出来,是2011年的技术。 不过这并不代表着我国这些22nm芯片就很落后,相反,在导航定位领

2022-06-29 11:06:17 4290

4290 我国在半导体行业一直都处于落后状态,不过近几年已经慢慢地开始追赶上来了,在半导体设备这方面,我国的上海微电子已经成功研发出了深紫外光光刻机,这种光刻机能够进行22nm制程工艺的加工,也就是说在

2022-06-29 10:37:36 1595

1595 之前北斗星通所宣布的22nm定位芯片在业界引起了巨大的轰动,北斗星通的创始人周儒欣表示:这颗芯片应该是全球卫星导航领域最先进的一颗芯片了。 有人就对这句话感到怀疑了,北斗星通22nm芯片先进吗?台积

2022-06-29 10:11:40 2297

2297 据芯片行业来看,目前22nm和28nm的芯片工艺技术已经相当成熟了,很多厂商也使用22nm、28nm的芯片居多,主要原因就是价格便宜,那么这两个芯片之间有什么性能差异呢?

2022-06-29 09:47:46 7231

7231 在全球范围内,目前共有美国、俄罗斯、中国三个国家拥有完整的卫星导航系统,我们中国的卫星导航系统就是大名鼎鼎的北斗导航系统,这款导航系统采用了一款北斗22nm芯片,那么这款北斗22nm芯片用途是什么呢

2022-06-27 11:56:36 2559

2559 目前从全球范围来说,也就只有台积电和三星这两家能做到5纳米工艺以下了。6月29日晚间,据外媒报道,三星宣布其基于栅极环绕型 (Gate-all-around,GAA) 晶体管架构的3nm工艺技术已经

2021-07-02 11:21:54 2136

2136 晶体管是器件中提供开关功能的关键组件。几十年来,基于平面晶体管的芯片一直畅销不衰。走到20nm时,平面晶体管开始出现疲态。为此,英特尔在2011年推出了22nm的FinFET,之后晶圆厂在16nm/14nm予以跟进。

2021-03-22 11:35:24 1945

1945 作者:泛林Nerissa Draeger博士 FinFET在22nm节点的首次商业化为晶体管——芯片“大脑”内的微型开关——制造带来了颠覆性变革。与此前的平面晶体管相比,与栅极三面接触的“鳍”所形成

2021-01-25 15:25:40 2669

2669

领先的移动和汽车SoC半导体IP提供商Arasan Chip Systems今天宣布,用于台积公司22nm工艺技术的eMMC PHY IP立即可用 加利福尼亚州圣何塞2021年1月21日 /美通社

2021-01-21 10:18:23 2193

2193 FinFET晶体管架构是当今半导体行业的主力军。但是,随着器件的持续微缩,短沟道效应迫使业界引入新的晶体管架构。在本文中,IMEC的3D混合微缩项目总监Julien Ryckaert勾勒出了

2020-12-30 17:45:16 2468

2468 互补场效应晶体管(hCFET)。 由于微加工技术的进步,电场效应晶体管(FET)已实现了高性能和低功耗。 在22nm世代中,它推进到被称为“ FinFET”的三维栅极结构的FET。此外,GAA(全方位门)结构已作为替代版本出现。 除此之外,还有一种称为CFET结构的技术,该结构是将

2020-12-21 10:36:58 2844

2844 全环绕栅极晶体管的出现满足了以上所有需求,从而允许摩尔定律在5纳米之后进一步前进。首先其生产工艺与鳍式晶体管相似,关键工艺步骤几乎一样(这点我们会在之后的文章中进一步讲解)。其次,全环绕栅极晶体管

2020-09-29 13:54:39 3601

3601 图片来源:联电 12月2日,中国台湾半导体代工厂联电(UMC)宣布,在首次成功使用硅技术之后,其22nm制程技术已准备就绪。 该公司称,全球面积最小、使用22nm制程技术的USB 2.0通过硅验证

2019-12-03 09:59:41 4346

4346 在9月的台湾SEMICON国际半导体展上,台积电(TSMC)首席执行官Mark Lui认为摩尔定律仍然有效。他表示,由于先进工艺技术(如纳米片)或3D FinFETS中的全栅晶体管技术的发展

2019-10-15 15:11:02 5321

5321 今天有多家媒体报道了中国科研人员实现了3nm半导体工艺的突破性进展,香港《南华早报》称中科院微电子所团队的殷华湘等人研究出了3nm晶体管,相当于人类DNA链条宽度,这种晶体管解决了玻尔兹曼热力学的限制。

2019-05-29 16:48:09 4236

4236 XX nm制造工艺是什么概念?芯片的制造工艺常常用90nm、65nm、40nm、28nm、22nm、14nm来表示。现在的CPU内集成了以亿为单位的晶体管,这种晶体管由源极、漏极和位于他们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流通断的作用。

2019-02-20 11:08:02 31585

31585 新的微加工技术可用于生产有史以来最小的3D晶体管,尺寸是目前主流商用产品的三分之一。

2018-12-12 09:40:48 2861

2861 半导体行业观察:目前,制造先进芯片离不开晶体管,其核心在于垂直型栅极硅,原理是当设备开关开启时,电流就会通过该部位,然后让晶体管运转起来。

2017-12-26 11:50:54 4280

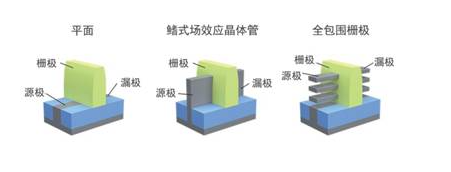

4280 intel的22nm 3D工艺牛,到底牛到什么程度,到底对业界有神马影响,俺也搞不太清楚。这不,一封email全搞定了。

2017-02-11 10:47:11 1166

1166 为什么说7nm是物理极限?缩短晶体管栅极的长度可以使CPU集成更多的晶体管或者有效减少晶体管的面积和功耗,并削减CPU的硅片成本。不过这种做法也会使电子移动的距离缩短,容易导致晶体管内部电子自发通过

2016-10-10 16:49:39 5765

5765 目前3D晶体管成为代工产业重点关注的技术,但很多人关于这个技术的细节不是很了解,我们在这里介绍一下。

2015-12-28 14:34:12 11367

11367

对于英特尔来说,要想在移动芯片市场多分得一杯羹,就需要借助其更加先进的制造能力的优势。而今日宣布的新款Atom SoCs——举例来说——即基于22nm的3D或“三栅极晶体管”工艺。与传统

2014-02-25 09:08:51 930

930 i HD1000是Speedster22i FPGA产品家族的首个成员。该器件采用英特尔领先的22nm 3D Tri-Gate晶体管技术,其功耗是竞争对手同类器件的一半。

2013-03-04 13:47:58 1477

1477 IBM在Common Platform技术论坛上展示了蓝色巨人对未来晶圆的发展预测,Common Platform是IBM、Globalfoundries和Samsung的联盟,旨在研究3D晶体管

2013-02-20 23:04:30 7669

7669 英特尔在4月23日正式发布Ivy Bridge处理器。Ivy Bridge是英特尔首款22nm工艺处理器,采用革命性的三栅极3D晶体管工艺制造。紧随其后,美国FPGA厂商Achronix在次日便宣布发布全球首款22nm工艺

2013-01-16 16:55:13 1363

1363 近日消息,英特尔计划将“3D晶体管”工艺应用到SoC移动芯片上,以获得产品性能飞跃性提升,但对于“3D晶体管”技术是否适用于SoC芯片的制造,参与旧金山国际电子产品大会的专家们

2012-12-11 09:05:45 1014

1014 裸眼3D显示技术详解介绍了3D显示原理、3D显示分类、柱状透镜技术、视差屏障技术、指向光源技术以及3D显示技术发展趋势。

2012-08-17 13:39:55 143

143 英特尔已经准备把第一个3D晶体管结构导入大量生产,它将是首款使用3-D Tri-Gate晶体管的量产芯片。22纳米处理器,代号为Ivy Bridge。3-D晶体管和2-D平面晶体管有本质性的区别,它不只可

2012-08-15 11:23:24 921

921

英特尔已经准备把第一个3D晶体管结构导入大量生产,它将是首款使用3-D Tri-Gate晶体管的量产芯片。22纳米处理器,代号为Ivy Bridge。3-D晶体管和2-D平面晶体管有本质性的区别,它不只可

2012-08-15 11:23:24 1179

1179 英特尔已经准备把第一个3D晶体管结构导入大量生产,它将是首款使用3-D Tri-Gate晶体管的量产芯片。22纳米处理器,代号为Ivy Bridge。3-D晶体管和2-D平面晶体管有本质性的区别,它不只可

2012-08-15 11:23:24 4748

4748 本文核心议题: 本文是对Intel 22nm三栅技术的后续追踪报道,为此,这里搜集了多位业界观察家、分析家对此的理解和意见,以便大家I更深入的了解ntel 22nm三栅技术。 鳍数可按需要进行

2012-08-15 09:46:03 1199

1199

Intel2011年5月6日研制成功的世界上第一个3D晶体管“Tri-Gate”现在已经逐步进入大家的视线了,本文将介绍3D晶体管的一些优点。

2012-08-08 11:49:46 1736

1736 什么是3D晶体管?3D晶体管,从技术上讲,应该是三个门晶体管。传统的二维门由较薄的三维硅鳍(fin)所取代,硅鳍由硅基垂直伸出。

2012-08-08 11:12:01 2992

2992 本文通过高清图详解Intel最新22nm 3D 晶体管 。业界一直传说3D三栅级晶体管技术将会用于下下代14nm的半导体制造,没想到英特尔竟提前将之用于22nm工艺,并且于上周四向全世界表示将在

2012-08-03 17:09:18 70

70 2012年4月23日,英特尔宣布采用3D三栅极晶体管设计,最小线宽为22纳米的Ivy Bridge微处理器量产成功,并于4月29日开始全球销售。

2012-05-13 09:35:43 4558

4558 Achronix 半导体公司今日宣布了其 Speedster22i HD和HP产品系列的细节,它们是将采用英特尔22nm 3D晶体管技术工艺制造的首批现场可编程门阵列(FPGA)产品。Speedster22i FPGA产品是业内唯一

2012-04-25 09:12:05 1138

1138 Intel Ivy Bridge处理器只是一次制程升级,对CPU性能来说没什么特别的,但是就制造工艺而言,Ivy Bridge不啻于一场革命,因为它不仅是首款22nm工艺产品,更重要的是Intel将从22nm工艺节点开

2012-04-18 14:02:29 890

890

在22nm,或许是16nm节点,我们将需要全新的晶体管。而在这其中,争论的焦点在于究竟该采用哪一种技术。这场比赛将关乎到晶体管的重新定义。在22/20nm逻辑制程的开发中,业界都争先

2012-03-25 10:52:16 1363

1363

在22nm,或许是16nm节点,我们将需要全新的晶体管。而在这其中,争论的焦点在于究竟该采用哪一种技术。这场比赛将关乎到晶体管的重新定义。在22/20nm逻辑制程的开发中,业界都争先

2012-03-06 10:08:16 1756

1756 可编程逻辑厂商Tabula 2月21日确认,英特尔将使用最新技术3-D三栅极晶体管技术为其代工22-nm3PLD产品。

2012-02-21 15:07:15 875

875

晶体管是现代电子学的基石,而Intel 此举堪称晶体管历史上最伟大的里程碑式发明,甚至可以说是重新发明了晶体管。半个多世纪以来,晶体管一直都在使用2-D 平面结构,现在终于迈入

2012-01-18 15:28:52 146

146 Intel在微处理器晶体管设计上取得重大突破,沿用50多年的传统硅晶体管将实现3D架构,一款名为Tri-Gate的晶体管技术得到实现。 3D Tri-Gate晶体管使用了一个微薄的三维硅鳍片取代了传统

2011-10-25 09:35:40 1274

1274 近日公布2011年“科技创新奖”,英特尔的3-D三栅极晶体管设计获得半导体类别创新大奖。英特尔的3-D三栅极晶体管结构代表着从2-D平面晶体管结构的根本性转变

2011-10-23 01:01:04 867

867 在本周于旧金山召开的英特尔开发者大会(IDF)中,英特尔将再揭示其采用三栅极(tri-gate)3D晶体管技术的22nm元件细节,并进一步说明超轻薄笔电(Ultrabook)的超薄、超低功耗设计概念。

2011-09-16 09:23:43 811

811 22nm以后的晶体管技术领域,靠现行Bulk MOSFET的微细化会越来越困难的,为此,人们关注的是平面型FD-SOI(完全空乏型SOI)元件与基于立体通道的FinFET。由于这些技术都不需要向通

2010-06-23 08:01:42 496

496 台积电又跳过22nm工艺 改而直上20nm

为了在竞争激烈的半导体代工行业中提供最先进的制造技术,台积电已经决定跳过22nm工艺的研

2010-04-15 09:52:16 816

816 Intel 22nm光刻工艺背后的故事

去年九月底的旧金山秋季IDF 2009论坛上,Intel第一次向世人展示了22nm工艺晶圆,并宣布将在2011年下半年发布相关产品。

2010-03-24 08:52:58 1019

1019 什么是绝缘栅极双极性晶体管

绝缘栅双极晶体管(IGBT)本质上是一个场效应晶体管,只是在漏极和漏区之间多了一个P型层.根据国际电工委员会IEC/TC(CO)1

2010-03-05 15:49:22 3985

3985 台积电计划于2012年Q3开始试产22nm HP制程芯片

据台积电公司负责开发的高级副总裁蒋尚义透露,他们计划于2012年第三季度开始试产22nm HP(高性能)制程的芯片产品,并

2010-02-26 12:07:17 783

783

电子发烧友App

电子发烧友App

评论