触发器(trigger)是SQL server 提供给程序员和数据分析员来保证数据完整性的一种方法,是一种特殊类型的存储过程,它是与表事件相关的特殊的存储过程,它的执行不是由程序调用,也不是手工启动,而是由事件来触发,比如当对一个表进行操作( insert,delete, update)时就会激活它执行。触发器经常用于加强数据的完整性约束和业务规则等。 触发器可以从 DBA_TRIGGERS ,USER_TRIGGERS 数据字典中查到。SQL3的触发器是一个能由系统自动执行对数据库修改的语句。

触发器与存储过程的唯一区别是触发器不能执行EXECUTE语句调用,而是在用户执行Transact-SQL语句时自动触发执行。

在Oracle中,触发器是一种特殊的存储过程,它在发生某种数据库事件时由Oracle系统自动触发发器,通常用于加强数据的完整性约束和业务规则等。

什么是触发器---触发器的功能

① 完成比约束更复杂的数据约束:触发器可以实现比约束更为复杂的数据约束

② 检查所做的SQL是否允许:触发器可以检查SQL所做的操作是否被允许。例如:在产品库存表里,如果要删除一条产品记录,在删除记录时,触发器可以检查该产品库存数量是否为零,如果不为零则取消该删除操作。

③ 修改其它数据表里的数据:当一个SQL语句对数据表进行操作的时候,触发器可以根据该SQL语句的操作情况来对另一个数据表进行操作。例如:一个订单取消的时候,那么触发器可以自动修改产品库存表,在订购量的字段上减去被取消订单的订购数量。

④ 调用更多的存储过程:约束的本身是不能调用存储过程的,但是触发器本身就是一种存储过程,而存储过程是可以嵌套使用的,所以触发器也可以调用一个或多过存储过程。

⑤ 发送SQL Mail:在SQL语句执行完之后,触发器可以判断更改过的记录是否达到一定条件,如果达到这个条件的话,触发器可以自动调用SQL Mail来发送邮件。例如:当一个订单交费之后,可以物流人员发送Email,通知他尽快发货。

⑥ 返回自定义的错误信息:约束是不能返回信息的,而触发器可以。例如插入一条重复记录时,可以返回一个具体的友好的错误信息给前台应用程序。

⑦ 更改原本要操作的SQL语句:触发器可以修改原本要操作的SQL语句,例如原本的SQL语句是要删除数据表里的记录,但该数据表里的记录是最要记录,不允许删除的,那么触发器可以不执行该语句。

⑧ 防止数据表构结更改或数据表被删除:为了保护已经建好的数据表,触发器可以在接收到Drop和Alter开头的SQL语句里,不进行对数据表的操作。

什么是触发器---触发器的组成

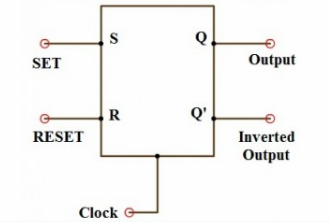

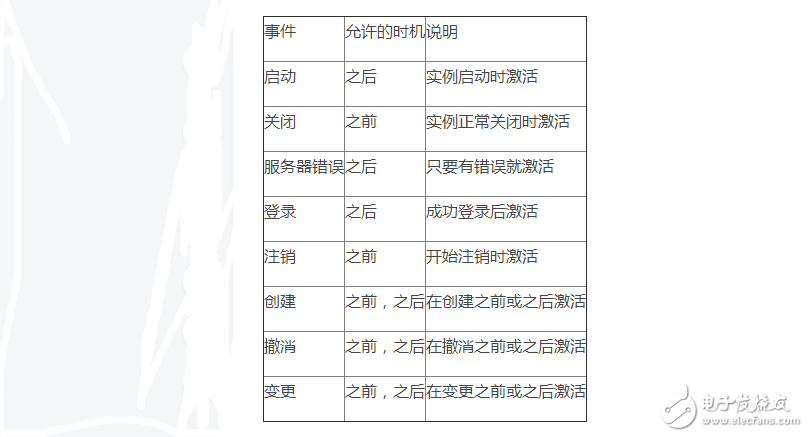

1. 触发事件:引起触发器被触发的事件。 例如:DML语句(INSERT, UPDATE, DELETE语句对表或视图执行数据处理操作)、DDL语句(如CREATE、ALTER、DROP语句在数据库中创建、修改、删除模式对象)、数据库系统事件(如系统启动或退出、异常错误)、用户事件(如登录或退出数据库)。

2. 触发时间:即该TRIGGER是在触发事件发生之前(BEFORE)还是之后(AFTER)触发,也就是触发事件和该TRIGGER的操作顺序。

3. 触发操作:即该TRIGGER 被触发之后的目的和意图,正是触发器本身要做的事情。 例如:PL/SQL块。

4. 触发对象:包括表、视图、模式、数据库。只有在这些对象上发生了符合触发条件的触发事件,才会执行触发操作。

5. 触发条件:由WHEN子句指定一个逻辑表达式。只有当该表达式的值为TRUE时,遇到触发事件才会自动执行触发器,使其执行触发操作。

6. 触发频率:说明触发器内定义的动作被执行的次数。即语句级(STATEMENT)触发器和行级(ROW)触发器。

什么触发器---触发器的基本特性

触发器有三个基本特性:

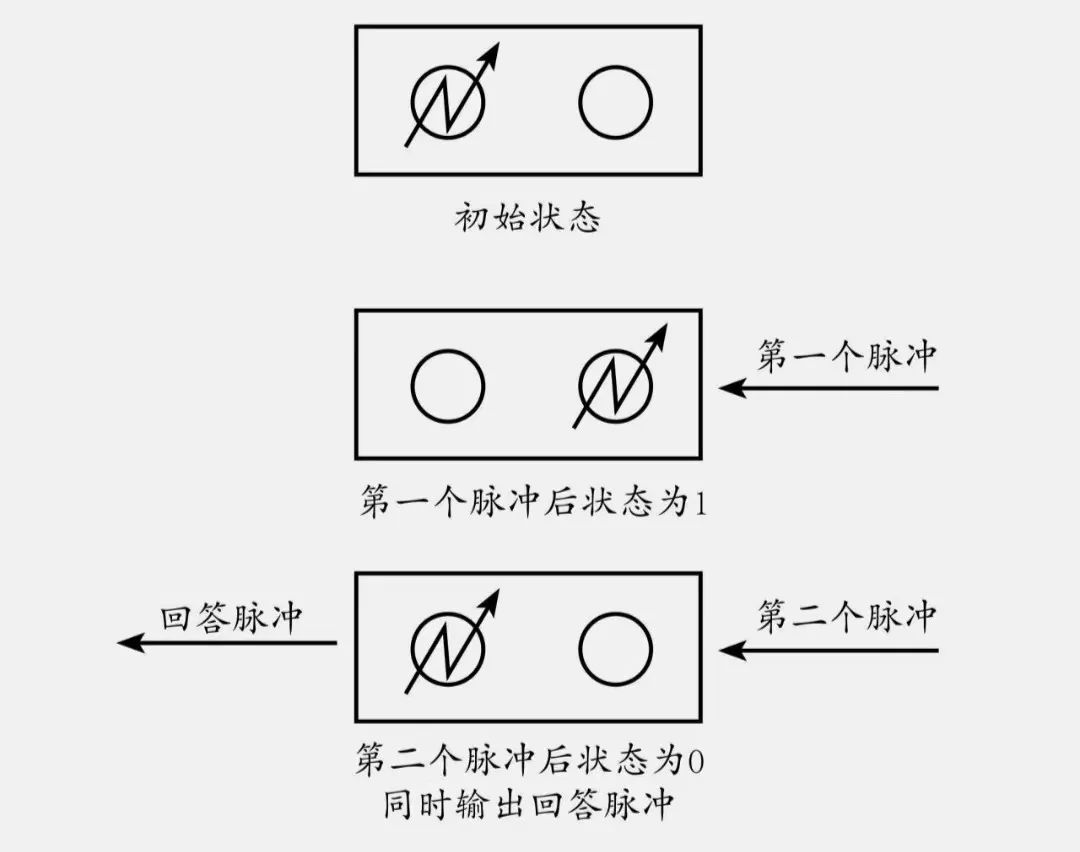

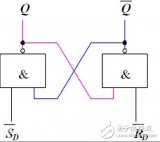

(1)有两个稳态,可分别表示二进制数码0和1,无外触发时可维持稳态;

(2)外触发下,两个稳态可相互转换(称翻转),已转换的稳定状态可长期保持下来,这就使得触发器能够记忆二进制信息,常用作二进制存储单元。

由于触发器有两个稳定状态,它就有一定的记忆功能,使用一个触发器可以记忆外部事件的两种状态,如果需要记忆更多的状态,就要通过多个触发器的连接来实现。由于一位二进制数也只有0和1两个状态,所以,一个触发器可以记忆一位二进制数,N个触发器,可以记忆N位二进制数。

什么是触发器---触发器的基本特点

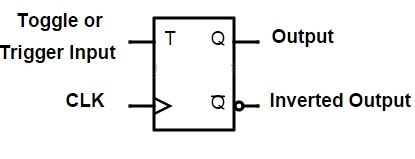

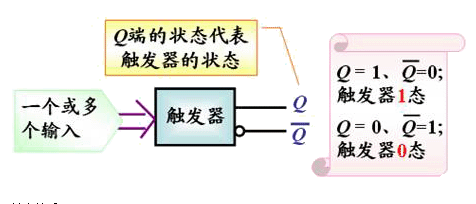

(1)具有两个互补输出端Q和/Q;

(2)具有“0”态和“1”态两个稳定状态;

(3)在外部信号作用下可实现状态转换,即翻转;

(4)外部信号消失时具有记忆功能,这就使得触发器能够记忆二进制信息。

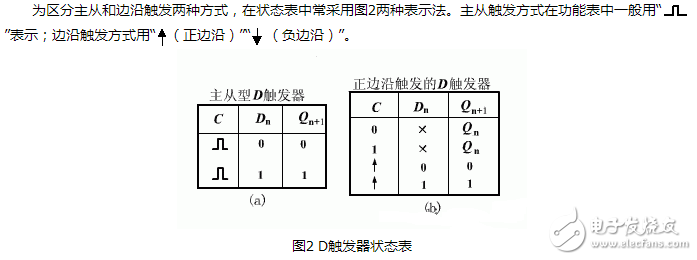

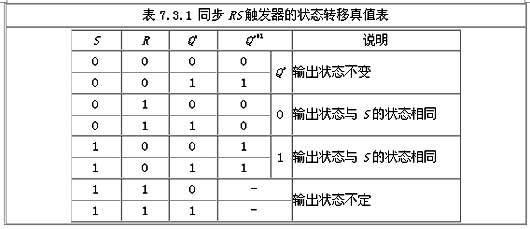

触发器逻辑功能的表示方法有:

(1)状态表或功能表:状态表中包括输入激励信号取值,触发器的原始状态(亦称初态)取值和翻转后的状态(亦称次态)的取值。而功能表则只列出输入激励信号取值和触发器次态取值,比较简洁。

(2)状态方程:由状态表归纳而列写出的逻辑方程。

(3)状态转换图。

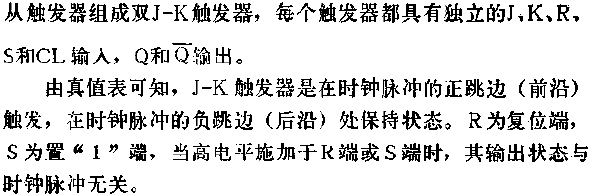

(4)波形图(又称时序图):画出对应输入状态波形的输出状态波形。

锁存器和触发器的区别

锁存器和触发器是具有记忆功能的二进制存贮器件,是组成各种时序逻辑电路的基本器件之一。区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然因为latch和flip-flop二者都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

1、latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

2、latch对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生;DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。latch是电平触发,相当于有一个使能端,且在激活之后(在使能电平的时候)相当于导线了,随输出而变化。在非使能状态下是保持原来的信号,这就可以看出和flip-flop的差别,其实很多时候latch是不能代替ff的。 4、latch将静态时序分析变得极为复杂。

5、目前latch只在极高端电的路中使用,如intel 的P4等CPU。 FPGA中有latch单元,寄存器单元就可以配置成latch单元,在xilinx v2p的手册将该单元成为register/latch单元,附件是xilinx半个slice的结构图。

一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

有些地方没有时钟,也只能用latch了。比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。

对latch进行STA的分析其实也是可以,但是要对工具相当熟悉才行。不过很容易出错。当前PrimeTime,是支持进行latch分析的。现在一些综合工具内置的STA分析功能也支持,比如RTL compiler, Design Compiler.除了ASIC里可以节省资源以外。latch在同步设计里出现的可能还是挺小的,现在处理过程中大都放在ff里打一下。

触发器的触发方式

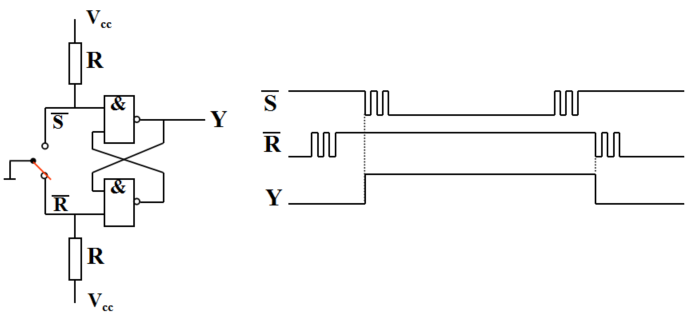

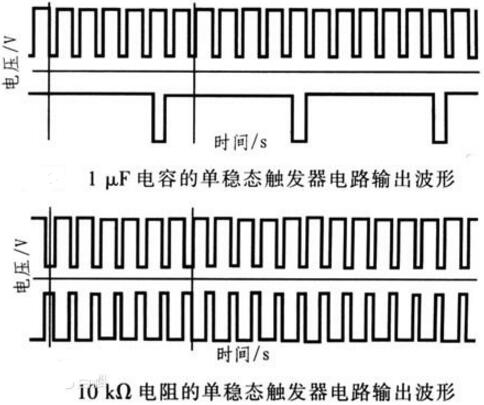

触发方式是研究触发器翻转时刻与时钟脉冲间的关系,在各类触发器中,存在三种触发方式:电平触发方式、主从触发方式、边沿触发方式。

1、电平触发方式

电平触发方式分为二种:高电平触发方式(在时钟脉冲C=1期间翻转);低电平触发方式(在时钟脉冲C=0期间翻转)。

电平触发方式结构简单、触发速度快。在时钟信号有效电平期间(C=1或C=0),触发器总是处于可翻转状态,输入信号的变化都会引起触发器状态的变化。在时钟信号无效电平期间,触发器状态保持不变。因此,在时钟信号有效电平宽度较宽时,触发器会连续不停地翻转。如果要求每来一个C脉冲触发器仅翻转一次的话,则对时钟脉冲的有效电平的宽度要求极为苛刻,所以实际中应用并不广泛。

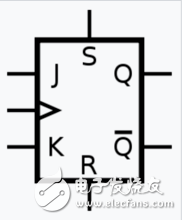

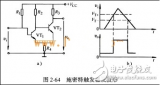

2、主从触发方式

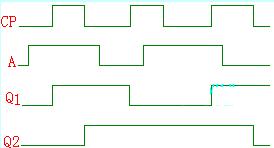

主从型JK触发器、由主从型JK触发器转换的各种功能的触发器都属于这种触发方式。这种触发方式的工作特点是:克服了在C有效电平期间多次翻转现象,具有一次翻转特性。就是说,在C有效电平期间,主触发器接受了输入信号发生一次翻转后,主触发器状态就一直保持不变,也不再随输入信号J。K的变化而变化。一次翻转特性有利有弊:利在于克服了空翻现象;弊是带来了抗干扰能力差的问题。

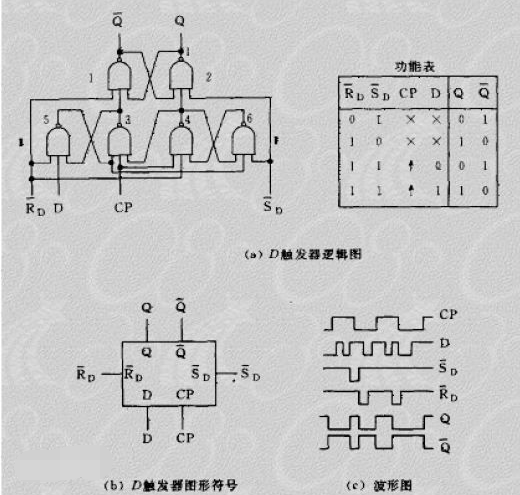

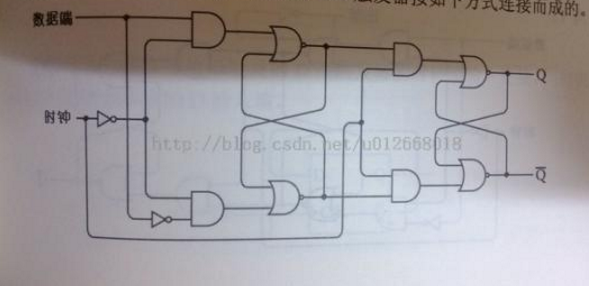

3、边沿触发方式

为了免除C=1期间输入信号不许扰动的限制,可采用边沿触发方式。其特点是:触发器只在时钟跳转时刻发生翻转,而在C=1或C=0期间,输入端的任何变化都不影响输出。比如前面介绍过的维持阻塞型的D触发器。除此以外,当然也有边沿触发的JK触发器。

如果翻转发生在上升沿就叫“前边沿触发或正边沿触发”。如果翻转发生在下降沿就叫“后边沿触发”或“负边沿触发”。

电子发烧友App

电子发烧友App

评论