十进制计数电路是数字电子技术里的重要环节,应用非常广泛。但此种电路的逻辑功能较为抽象,难于理解,学生不容易掌握。为此,我们设计了一款基于CD4518十进制计数器构成的逻辑功能测试电路,学生根据电路的测试结果推导CD4518的逻辑功能,从而解决了这个难题。

一、任务要求

根据电路原理图设计装配CD4518逻辑功能测试电路,检查无误后接入+5V电源,并利用单脉冲发生器给测试电路提供输入脉冲信号,根据测试结果推导CD4518的逻辑功能。

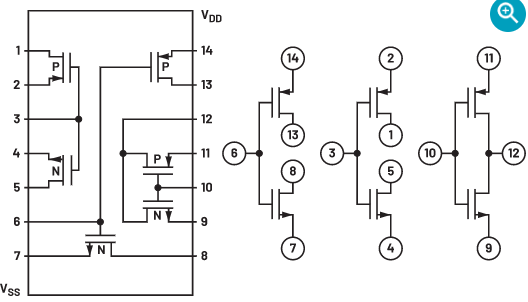

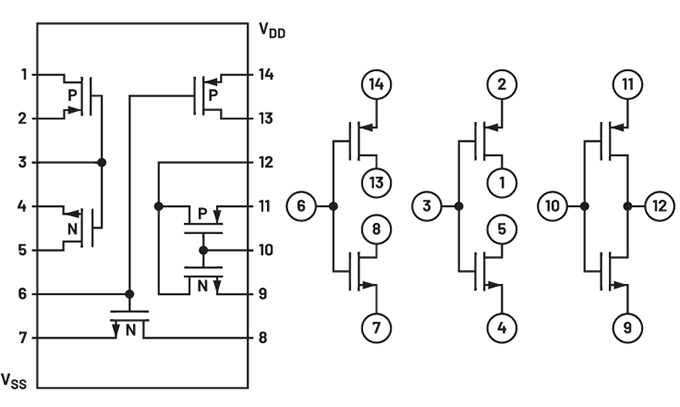

二、CD4518简介

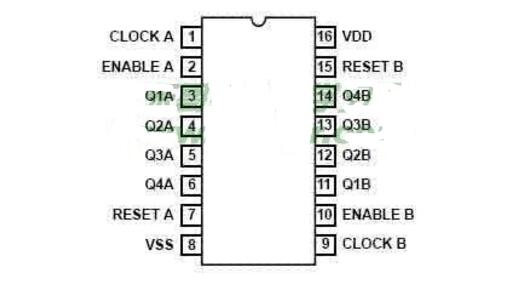

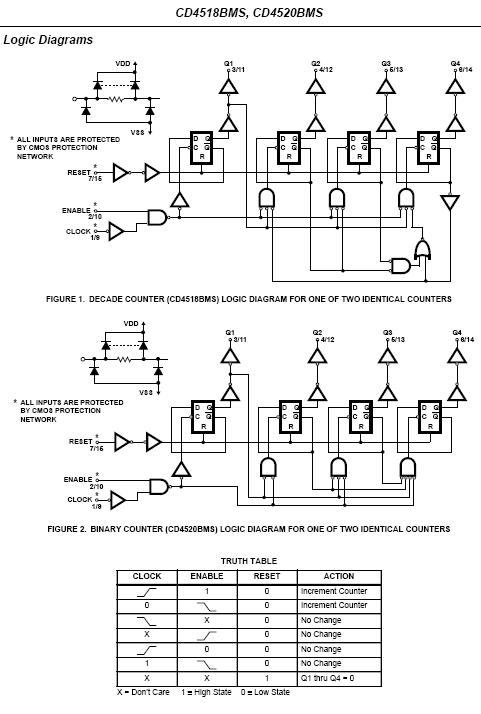

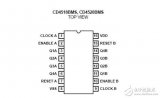

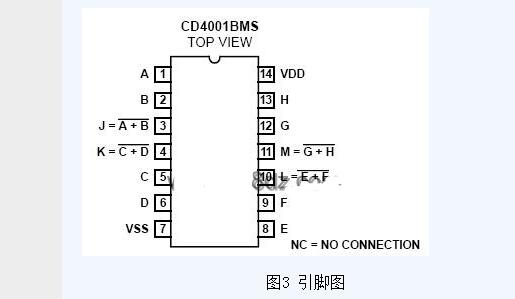

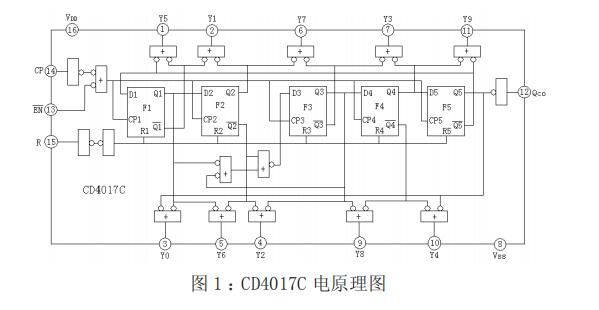

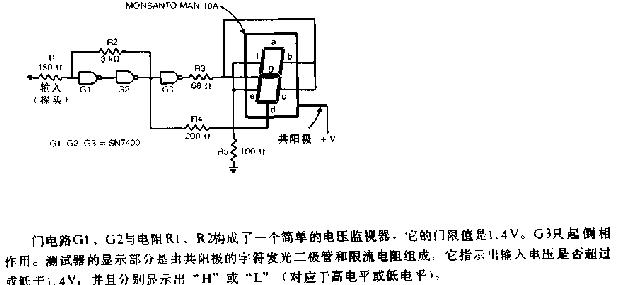

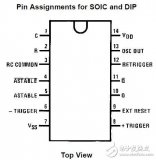

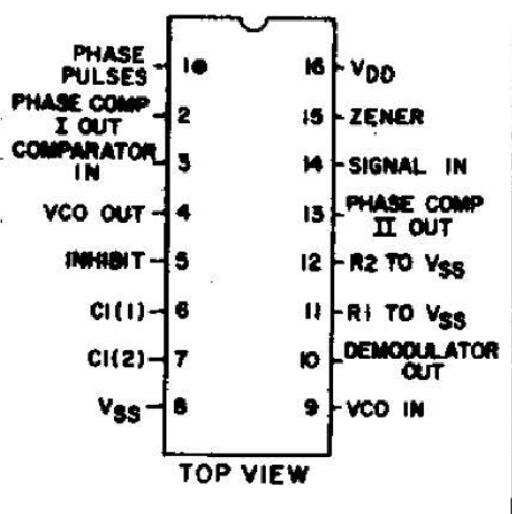

C D 4 5 1 8 为C M O S 型双B C D 同步十进制计数器,如图1所示。其引脚功能:

① 1 C P , 2 C P : 时钟输入端, 上升沿有效。②1EN,2EN:时钟输入端,下降沿有效。③1CR,2CR:直接置零(复位)端。④1Q0~1Q3,2Q0~2Q3:四位触发器输出端(BCD码)。⑤VDD:电源正极。

⑥Vss:电源负极。

图1 CD4518引脚分布

三、电路装配与测试

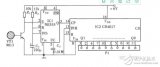

CD4518逻辑功能测试电路由CD4518十进制计数器、LED发光二极管指示电路两部分组成。另为了测试方便,还需设计一个单脉冲发生器,用来提供输入的脉冲信号。

1.单脉冲发生电路的装配与测试

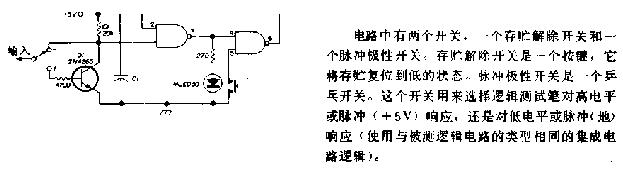

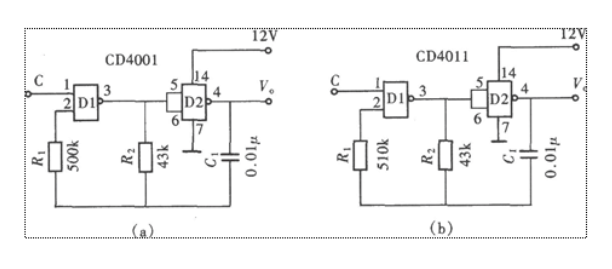

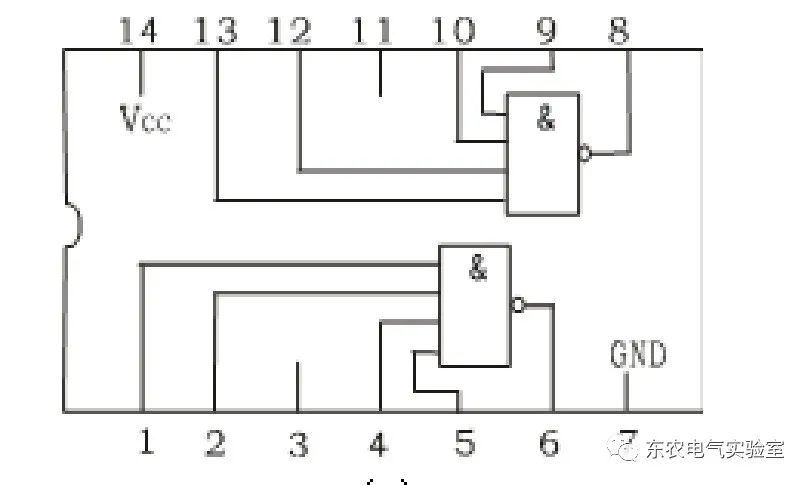

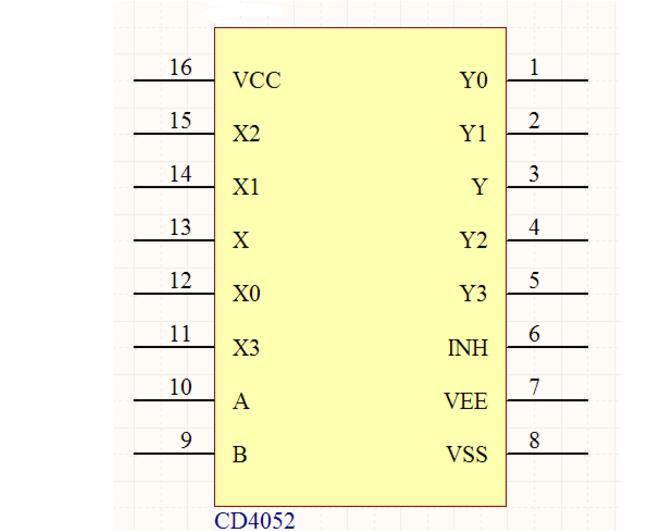

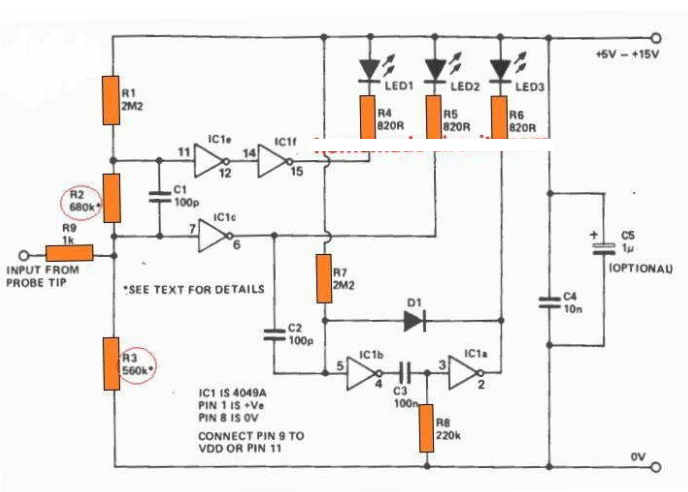

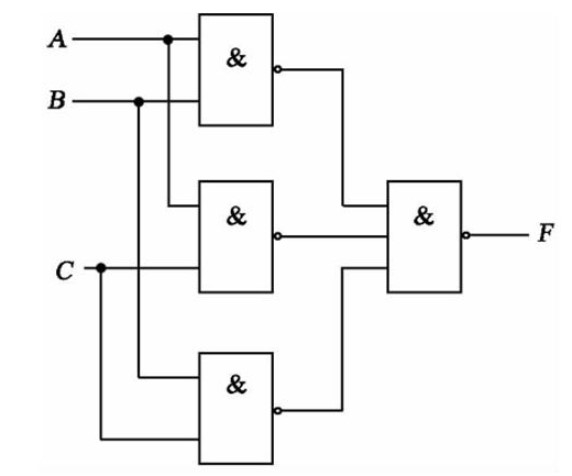

利用与非门集成块CD4011为基础设计装配单脉冲发生器,并以此作为CD4518逻辑功能测试电路的输入脉冲。其电路如图2所示。

图2 单脉发货时呢过器

单脉冲发生电路工作过程:当开关打在1处时,输出Vo=“0”,因输出端通过反馈加到输入端实现自锁功能,故开关在由1拨往2的中间位置时,因自锁输出仍为“0”;当开关打到2处时,输出Vo=“1”,同样,输出端通过反馈加到输入端实现了自锁,这样输出只有两种状态:“0”和“1”。

注意,开关从1处拨到2处时,输出状态从“0”变为“1”,即产生一个上升沿信号;开关从2拨至1处,输出状态从“1”变为“0”,即产生一个下降沿信号。

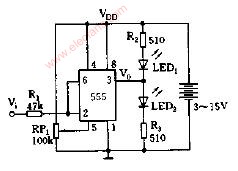

2.CD4518逻辑功能测试电路的装配与测试

1)电路的制作

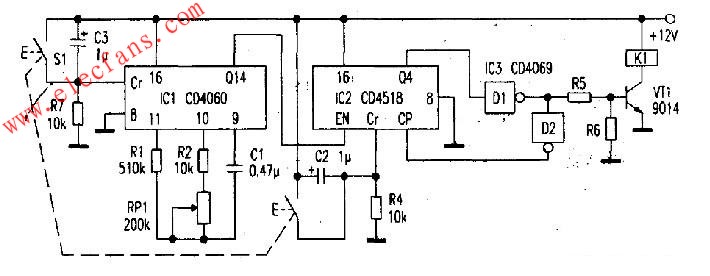

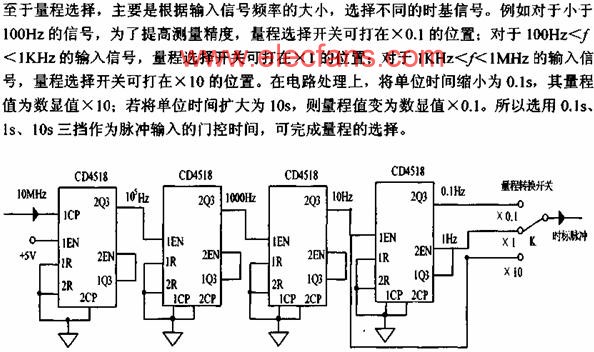

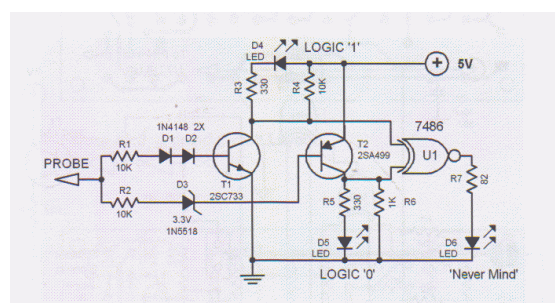

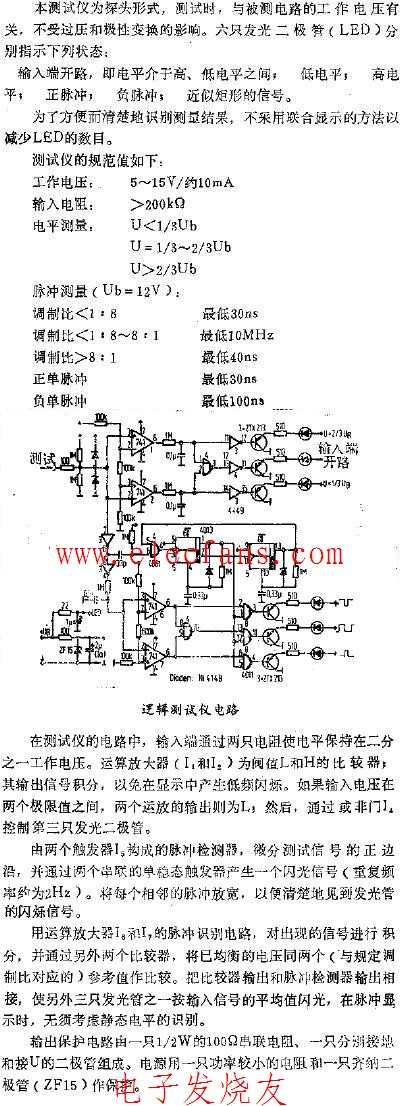

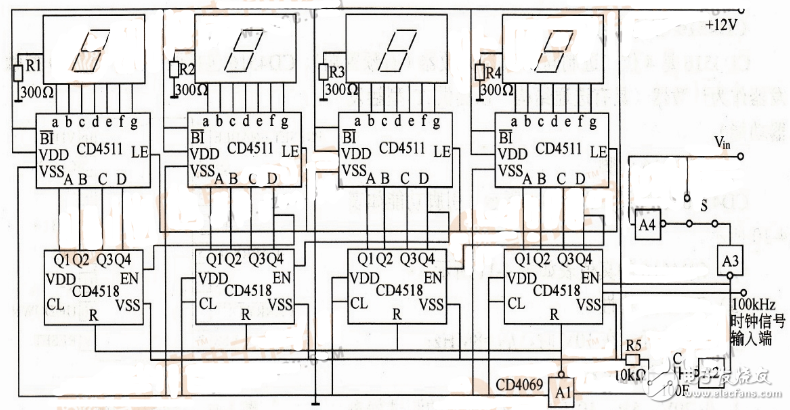

首先根据CD4518逻辑功能测试电路的元器件清单(表1)清点和检测元件,并将检测结果填入表中。然后根据电路原理图(图3),完成电路的装配操作。

表1 元件清单

图3 CD4518逻辑功能测试电路

CD4518逻辑功能测试电路装配完成经检查确认无误后,接入+5V电源,并给测试电路输入由单脉冲发生器提供的单脉冲信号,观察测试电路输出的现象。我们以输出指示电路中发光二极管发光表示逻辑“1”,发光二极管熄灭表示逻辑“0”,将测试结果记录在表2中。

表2 CD4518逻辑功能测试

四、CD4518逻辑功能推导

根据电路测试结果(表2)分析推导CD4518逻辑功能。

实测推导结果如下:

1.CD4518内部含有两个独立的十进制计数单元,每个单元各有两个时钟输入端CP和EN,其中CP为上升沿触发,EN为下降沿触发;

2.EN作为时钟输入端时,CP必须接地;CP作为时钟输入端时,EN必须电源正。

3.1CR和2CR分别为两个计数器的复位端(高电平有效);

4.1Q0~1Q3和2Q0~2Q3为计数器的四位输出端。

CD4518逻辑功能总结如表3所示。

表3 CD4518逻辑功能

五、结束语

通过CD4518逻辑功能测试电路的制作与测试,学生学习的主动性大大增强,并且能在教师的引导下利用单脉冲发生器给电路提供脉冲信号从而去探索新知识,通过学生动手操作的过程突破了本电路的教学难点,学生不仅较好地理解了CD4518的逻辑功能,同时,电路的制作与调试过程也提高了学生的技术应用能力。

电子发烧友App

电子发烧友App

评论