因项目需要使用到STM32的ADC功能,虽然对ADC的使用并不陌生,但是第一接触stm32的ADC功能还是有种无从下手的感觉,主要是因为STM32ADC设计较为复杂,一时对相关的专业术语较为生疏,此外固件库中涉及到的函数虽都进行了分门别类但是还是感觉函数较多,难以很快掌握,现就将个人理解写出,以便大家共同进步。

一、stm32 ADC特点

认识事物首先还是要从整体上把握,ADC也一样的道理,STM32的ADC外设提供了非常完善的功能,虽然其中很大一部分不见得能在项目中使用,但加深对其的认识对于合理利用其资源也是非常有必要的。

下面以项目采用的STM32L151为例,其他类型大同小异。

先看原文:

• 12-bit, 10-bit, 8-bit or 6-bit configurable resolution

• Interrupt generation at the end of regular conversions, end of injected conversions, and in case of analog watchdog or overrun events (for regular conversions)

//在规则转换结束、注入转换结束以及模拟看门狗溢出和overrun事件(规则转换模式)发生时能产生中断

• Single and continuous conversion modes //有单次和连续转换模式

• Scan mode for automatic conversions in a fully programmable order //在自动转换中支持完成可编程的扫描模式

• Programmable data alignment with in-built data coherency //数据对齐方式可编程

• Programmable and individual sampling time for each ADC channel //可以为每个通道设置独立的采样时间

• External trigger option with configurable edge detection for both regular and injected

conversions //外部触发模式对规则和注入转换模式均支持可配置的边沿触发方式

• Discontinuous mode //非连续模式

• ADC conversion time: 1 μs at full speed (ADC clocked at 16 MHz) down to 4 μs at low speed (ADC clocked at 4 MHz), independent of the APB clock//最低采样时间

• Automatic power-up/power-down to reduce the power consumption//自动的上下电便于节能

• ADC supply requirements:

– 2.4 V to 3.6 V at full speed or with reference zooming (VREF+ 《 VDDA)

– down to 1.8 V at slower speeds //工作电压范围

• ADC input range: VREF– ≤ VIN ≤ VREF+

• Automatic programmable hardware delay insertion between conversions

• DMA request generation during regular channel conversion //规则转换支持DMA

从官方的描述中可以了解到STM32ADC所提供的强大功能,及一些工作特性,那么如何才能使用这些功能呢?

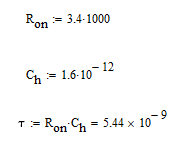

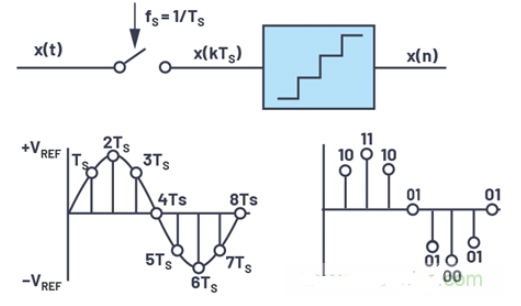

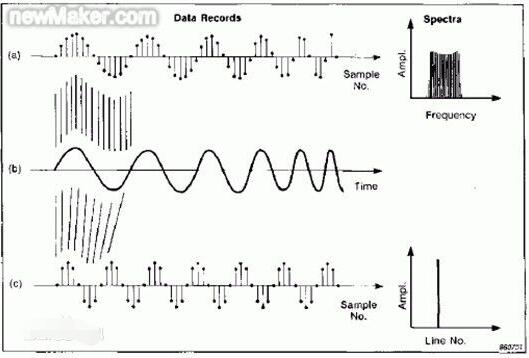

ADC转换就是输入模拟的信号量,单片机转换成数字量。读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。采样周期一般来说=转换时间+读取时间

转换时间=采样时间+12.5个时钟周期。采样时间是你通过寄存器告诉STM32采样模拟量的时间,设置越长越精确。

二、STM32 ADC采样频率时间、周期、计算方法分析

1. :先看一些资料,确定一下ADC的时钟:

(1),由时钟控制器提供的ADCCLK时钟和PCLK2(APB2时钟)同步。CLK控制器为ADC时钟提供一个专用的可编程预分频器。

(2) 一般情况下在程序 中将 PCLK2 时钟设为 与系统时钟 相同

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK_Div2);

(3)在时钟配置寄存器(RCC_CFGR) 中 有 为ADC时钟提供一个专用的可编程预分器

位15:14 ADCPRE:ADC预分频

由软件设置来确定ADC时钟频率

00:PCLK2 2分频后作为ADC时钟

01:PCLK2 4分频后作为ADC时钟

10:PCLK2 6分频后作为ADC时钟

11:PCLK2 8分频后作为ADC时钟

我们可对其进行设置 例如:

/* ADCCLK = PCLK2/4 */

RCC_ADCCLKConfig(RCC_PCLK2_Div4);

另外 还有 ADC 时钟使能设置

/* Enable ADC1, ADC2 and GPIOC clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1 | RCC_APB2Periph_ADC2 |

RCC_APB2Periph_GPIOC, ENABLE);

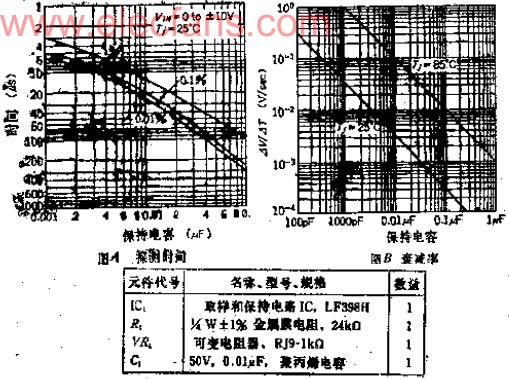

(4)16.7 可编程的通道采样时间

ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1和ADC_SMPR2寄存器中的SMP[2:0]位而更改。每个通道可以以不同的时间采样。

总转换时间如下计算:

TCONV(转换时间) = 采样时间+ 12.5 个周期

例如:

当ADCCLK=14MHz 和 1.5周期的采样时间:

TCONV = 1.5 + 12.5 = 14周期= 1μs

SMPx[2:0]:选择通道x的采样时间

这些位用于独立地选择每个通道的采样时间。在采样周期中通道选择位必须保持不变。

000:1.5周期100:41.5周期

001:7.5周期101:55.5周期

010:13.5周期110:71.5周期

011:28.5周期111:239.5周期

注:

– ADC1的模拟输入通道16和通道17在芯片内部分别连到了温度传感器和VREFINT。

– ADC2的模拟输入通道16和通道17在芯片内部连到了VSS。

2. 具体分析如下:

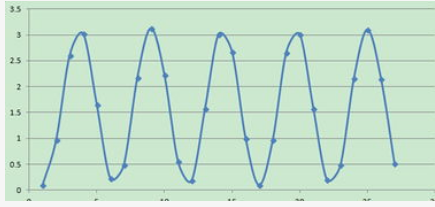

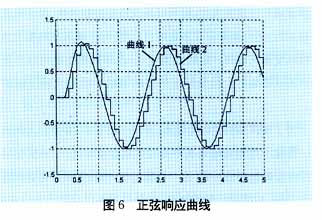

(1)我们的输入信号是50Hz (周期为20ms),初步定为1周期200个采样点,(注:一周期最少采20个点,即采样率最少为1k) ,每2个 采样点间隔为 20ms /200 = 100 us

ADC可编程的通道采样时间 我们选最小的 1.5 周期,则 ADC采样周期一周期大小为

100us /1.5=66us 。 ADC 时钟频率为 1/66us =15 KHz。

ADC可编程的通道采样时间 我们选71.5 周期,则 ADC采样周期一周期大小为

(100us /71.5) 。 ADC 时钟频率为 7.15MHz。

(2)接下来我们要确定系统时钟:我们 用的是 8M Hz 的外部晶振做时钟源(HSE),估计得 经过 PLL倍频 PLL 倍频系数分别为2的整数倍,最大72 MHz。为了 提高数据 计算效率,我们把系统时钟定为72MHz,(PLL 9倍频)。则PCLK2=72MHz,PCLK1=36MHz;

我们通过设置时钟配置寄存器(RCC_CFGR) 中 有 为ADC时钟提供一个专用的可编程预分器,将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为 9MHz

从手册可知: ADC 转换时间:

STM32F103xx增强型产品:ADC时钟为56MHz时为1μs(ADC时钟为72MHz为1.17μs)

(3)由以上分析可知:不太对应,我们重新对以上中 内容调整,提出如下两套方案:

方案一:我们的输入信号是50Hz (周期为20ms),初步定为1周期2500个采样点,(注:一周期最少采20个点,即采样率最少为1k) ,每2个 采样点间隔为 20ms /2500 = 8 us

ADC可编程的通道采样时间 我们选71.5周期,则 ADC采样周期一周期大小为

8us /71.5 。 ADC时钟频率约为 9 MHz。

将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为 9MHz

方案二:我们的输入信号是50Hz (周期为20ms),初步定为1周期1000个采样点,(注:一周期最少采20个点,即采样率最少为1k) ,每2个 采样点间隔为 20ms /1000= 20 us

ADC可编程的通道采样时间 我们选239.5周期,则 ADC采样周期一周期大小为

20us /239.5 。 ADC时钟频率约为 12 MHz。

将PCLK2 6 分频后作为ADC 的时钟,则可知ADC 时钟频率为 12MHz

电子发烧友App

电子发烧友App

评论