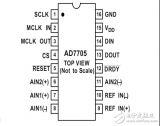

AD7705为完整16位低成本、Σ-Δ型ADC。采用SP IQ SPI兼容的三线串行接口,能够方便地与各种微控制器和DSP连接,也比并行接口方式大大节省了CPU的 I O口。本文主要以ad7705应用经验及应用所需注意的事项为中心而展开的讨论。

ad7705应用经验总结

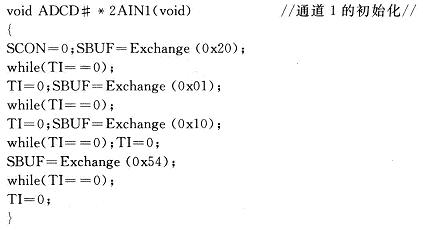

1.时序注意要点:数字接口迷失的时候可以通过ADIN输入持续32个脉冲周期(DCLK)以上的高电平将复位AD7705的数字接口,复位之后要等待500us以上才能访问AD7705芯片,这种复位方式不会影响AD7705内部的任何寄存器,所有的寄存器将保持复位之前的内容,但所有的寄存器在数字接口迷失的状态下内容是不确定的,因此强烈建议在复位之后重新设置AD7705内部所有的寄存器,防止错误。而芯片管脚RESET的复位将使片内所有的寄存器恢复到上电的默认值。时钟输入信号DCLK是一种施密特出发信号,能够适应光耦合器的慢速边沿,其他数字输入信号的上升和下降时间不应超过1us。

2.AD7705时钟大于2M时,时钟设置寄存器的CLK位应置1,小于2M时应置0。DCLK的脉冲宽度要满足最小的脉宽要求。在时钟DCLK下降之后的低电平期间读取数据ADOUT。在时钟DCLK的低电平期间设置要写入数据ADIN,然后在DCLK的上升沿写入到7705。写入数据以及读取数据的时钟DCLK的数目要与(被写入或被读取的寄存器)的位数长度一致,多于或少于(寄存器位长度)的时钟DCLK数目都将导致操作错误。在两次写操作之间,ADIN应最好保持在高电平:因为任何(读或写)操作都必须从写通信寄存器开始,而且写入通信寄存器的8个位中的第1位必须为0,后续的位才能被写入到通信寄存器。所以当ADIN为0的时候,万一时钟DCLK受到干扰导致0写入通信寄存器,AD7705会误认为是写通信寄存器的操作开始而等待后续的7位位串,发生这种干扰之后会导致AD7705的数字接口迷失,从而导致内部寄存器的内容也许会变得未知状态。此外,时钟信号DCLK在两次操作AD7705之间要保持高电平。即:在不访问AD7705的空闲时刻,或者两次操作之间的空闲时刻,ADIN、DCLK都最好保持高电平为最可靠。

3.DRDY信号为数据AD转换完成的指示信号,低电平期间表示AD转换完成,可以读取数据寄存器的内容,高电平期间表示AD转换正在进行,这时不能访问数据寄存器。对于系统校准和内部校准也一样,低电平期间表示校准完成,可以读取校准寄存器的内容,高电平期间表示校准正在进行,这时不能访问校准寄存器。违反这些规定的操作,结果时未知的。此外程序中千万不能把DRDY的逻辑搞反,否则结果不可预料。

4.不管是校准还是数据AD转换,数字滤波器同步位FSYNC都要置为0,这样AD7705的校准或者数据AD转换工作才能进行,否则校准和AD转换不会进行,DRDY信号也不会变低。当FSYNC=0时,在校准或AD转换结束后DRDY信号将变低,此时可以读取校准系数或者数据寄存器。

5.采用非缓冲模式时,AD7705模拟输入前端的电阻电容的变化对AD转换精度影响很大。若系统工作时的信号源、温度环境、器件参数变化很大,导致AD7705模拟输入前端电路的参数跟系统校准时的参数不一致,误差会非常大。缓冲模式能解决这种问题,当使能缓冲模式时,AD7705会在模拟输入端和AD转换器之间接入一个缓冲器Buffer,这样AD7705就能适应模拟输入前端信号源的大阻抗、器件参数(电阻电容)的变化、温度环境的变化等各种与系统校准时的不一致情况(即器件工作条件的变化)。所以,AD7705的校准和正常工作最好都要在缓冲模式下进行。

6.电压输入范围:对于非缓冲模式,模拟输入信号范围是GND-30mV至VDD+30mV之间。对于缓冲模式,模拟输入信号范围是GND+50mV至VDD-1.5V之间。

7.非缓冲模式、单极性、增益为GAIN:此时AD7705的反相输入端VIN-的范围是GND-30mV至VDD+30mV-VREF/GAIN之间,其中VREF为AD7705的参考电压。正相输入端VIN+的范围是V-至V-+VREF/GAIN。如右图,即V+和V-都必须大于GND小于VDD,同时还要考虑单极性的输入范围,即V-还必须小于VDD+30mV-VREF/GAIN,才不至于模拟输入为V+max=V-+VREF/GAIN时大于VDD+30mV。

8.非缓冲、双极性、增益为GAIN:此时V+和V-都必须大于GAN小于VDD,V-还必须小于VDD+30V-VREF/GAIN,这样输入V+max=V-+VREF/GAIN不至于大于VDD+30mV。V-还必须大于GND-30mV +VREF/GAIN,才不至于输入V+min=V――VREF/GAIN时小于GND-30mV。正相输入端VIN+的正信号输入范围是V-至V-+VREF/GAIN,正相输入端VIN+的负信号输入范围是V-至V--REF/GAIN。

9.缓冲模式、单极性、增益为GAIN:此时AD7705的反相输入端VIN-的范围是【GND+50mV】至【VDD-1.5V-VREF/GAIN】之间,其中VREF为AD7705的参考电压。正相输入端VIN+的范围是【V-】至【V-+VREF/GAIN】。如右图,即V+和V-都必须大于GND+50mV小于VDD-1.5V,同时还要考虑单极性的输入范围,即V-还必须小于VDD-1.5V-VREF/GAIN,才不至于输入V+max=【V-+VREF/GAIN】时大于VDD-1.5V。

10.缓冲模式、双极性、增益为GAIN:此时AD7705的反相输入端VIN-的范围是【GND+50mV+VREF/GAIN】至【VDD-1.5V-VREF/GAIN】之间,这样才不至于输入VIN+max=【V-+VREF/GAIN】时导致VIN+大于VDD-1.5V、输入VIN+min=【V――VREF/GAIN】时导致VIN+小于GND+50mV。其中VREF为AD7705的参考电压。正相输入端VIN+的正信号输入范围是【V-】至【V-+VREF/GAIN】,正相输入端VIN+的负信号输入范围是【V-】至【V--REF/GAIN】。

电子发烧友App

电子发烧友App

评论