相关推荐

截短Reed-Solomon码译码器的FPGA实现

截短Reed-Solomon码译码器的FPGA实现提出了一种改进的BM算法,并在此基础上提出了一种大量采用并行结构的截短RS码译码器的实现方式。验证表明,该算法能显著提高基于FPGA的RS译码器

2009-09-19 09:39:43

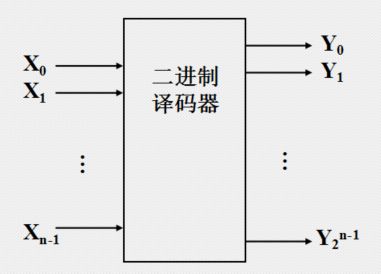

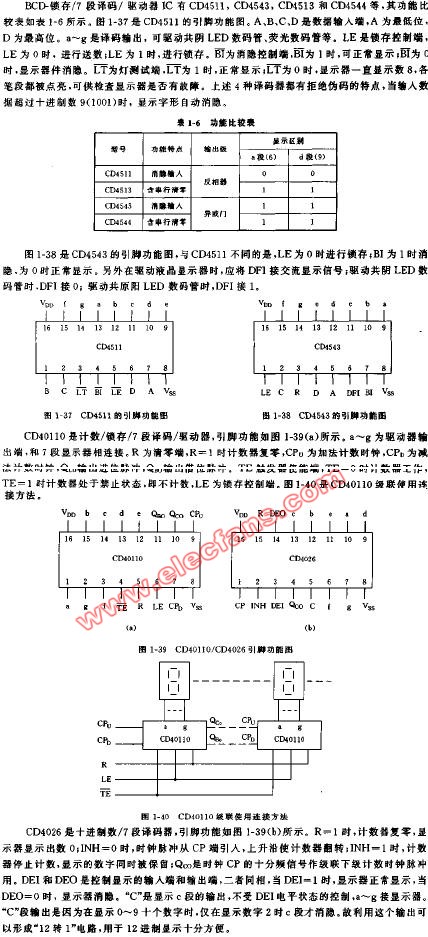

二进制译码器和二-十进制译码器介绍

输入:二进制代码,有n个;

输出:2^n 个特定信息。

1.译码器电路结构

以2线— 4线译码器为例说明

2线— 4线译码器的真值表为:

2023-04-30 16:29:00 684

684

684

684

常见译码器工作原理介绍

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出的高、低电平信号。常用的译码器电路有二进制译码器、二--进制译码器和显示译 码器。译码为编码的逆过程。它将编码时赋予代码的含义“翻译”过来。实现

2023-04-26 15:39:40 2201

2201

2201

2201

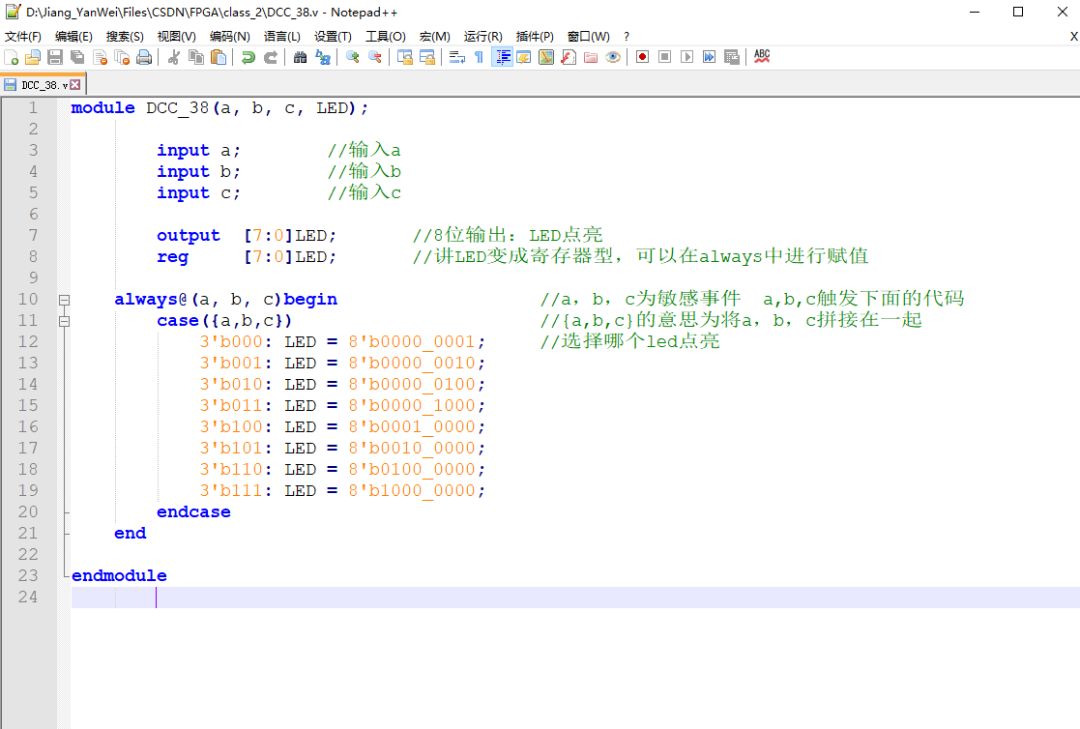

FPGA之三八译码器

一听到三八译码器这个东西可能会感觉有点熟悉,其实在STC89C51系列单片机中,里面就有一个三八译码器,就是一开始的流水灯程序,LED0-7这八个LED!但是怎么在FPGA中实现三八译码器呢?其实很简单。

2023-04-26 15:38:21 1061

1061

1061

1061

单片机 什么是编码器?什么是译码器?

译码器1. 译码器定义译码器是一种用以检测输入位(码)的特定组合是否存在,并以特定的输出电平来指示这种特定码的存在的数字电路。——《数字电子技术基础系统方法》译码器的功能是将具有特定含义的二进制码

2021-11-24 12:21:02 9

9

9

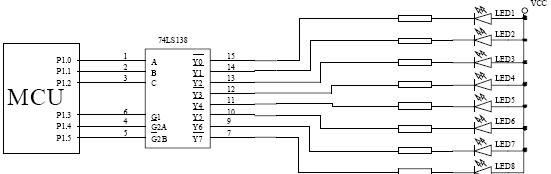

9使用38译码器扩展单片机接口

74HC138译码器1. 介绍在设计单片机电路的时候,单片机的IO口数量是有限的,有时并满足不了我们的设计需求,因此为了控制更多的器件,就需要使用一些外围的数字芯片进行引脚扩展。常用

2021-11-17 10:36:02 11

11

11

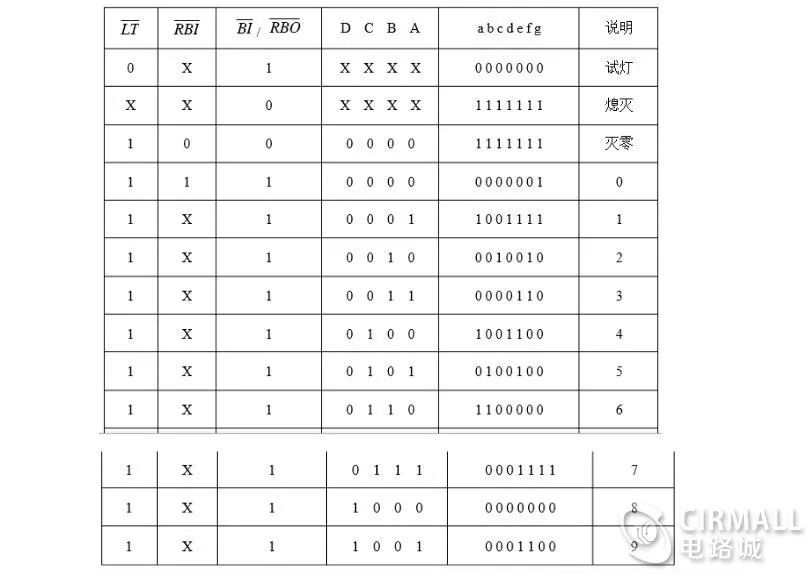

1138译码器真值表以及功能与原理

38译码器也就是三线八线译码器,那么38译码器真值表以及功能与原理是什么呢,下面小编就为大家来带38译码器真值表以及功能与原理。 三线八线译码器的三线是指三位二进制数字,其会组成000到111共八个

2021-07-08 15:55:54 97073

97073

97073

97073

如何使用FPGA实现跳频系统中的Turbo码译码器

给出了跳频系统中 Turbo码译码器的FPGA( field programmable gate array)实现方案。译码器采用了MaxLog-map译码算法和模块化的设计方法,可以对不同帧长

2021-04-01 11:21:46 5

5

5

5通过Viterbi译码算法实现译码器优化实现方案

由网格图的输入支路特点分析可知,产生任意一个状态节点Si的输入条件mi是确定的,即mi=‘1’,i为偶数;mi=‘0’,i为奇数。输入条件mi表示译码器最终需要输出的比特信息。此外,译码器所要找的留选路径是不同状态的组合。

2018-10-02 01:07:16 4926

4926

4926

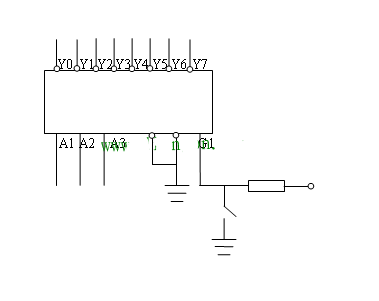

492674HC138组成32线译码器的电路图 74HC138组成32线译码器方法

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

2018-08-08 09:21:03 26807

26807

26807

26807译码器的分类和应用

本文主要介绍了译码器的分类和应用。译码器指的是具有译码功能的逻辑电路,译码是编码的逆过程,它能将二进制代码翻译成代表某一特定含义的信号(即电路的某种状态),以表示其原来的含义。译码器可以分为:变量

2018-04-04 11:51:12 35527

35527

35527

35527

译码器的逻辑功能_译码器的作用及工作原理

本文首先介绍了译码器的定义与译码器的分类,其次介绍了译码器的作用和译码器的工作原理,最后介绍了译码器的逻辑功能。

2018-02-08 14:04:06 104354

104354

104354

104354

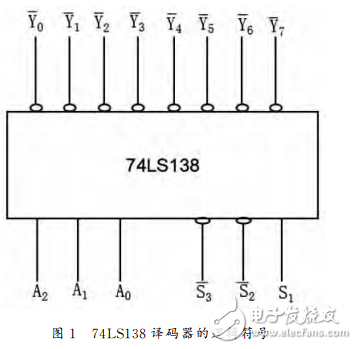

74ls138译码器的级联电路分析

74LS138是带有扩展功能的集成3线—8线译码器,它有3个使能控制端,3个代码输入端,8个信号输出端.控制端用来控制译码器的工作状态,如果仅为了控制译码器,一个使能端就够了,该器件之所以设置三个使能端,除了控制译码器的工作外,还可以更灵活、更有效地扩大译码器的使用范围.

2017-12-04 16:08:10 76265

76265

76265

76265

基于ASIC的高速Viterbi译码器设计

针对无线通信系统中对于高频率、高吞吐量的要求,提出了一种基于ASIC的高速Viterbi译码器实现方案。该译码器在约束度小于等于9的情况下,采用全并行结构的加比选模块。性能分析结果表明,在SMIC

2017-11-11 17:56:15 6

6

6

6基于RS译码器设计和仿真

为了解决在RS译码中存在的译码过程复杂、译码速度慢和专用译码器价格高等问题,以RS(255,239)码为例,采用了基于改进的无求逆运算的Berlekamp-Massey( BM)迭代算法。结合FP

2017-11-07 15:27:06 15

15

15

1574hc154译码器

74HC154 译码器可接受4 位高有效二进制地址输入,并提供16 个互斥的低有效输出。74HC154 的两个输入使能门电路可用于译码器选通,以消除输出端上的通常译码“假信号“,也可用于译码器扩展

2017-11-02 12:03:02 6116

6116

6116

6116基于译码器扩展的单片机键盘输入电路

文章从单片机系统键盘输入电路的各种方式入手,先后对各种不同输入方式进行了探讨,对带译码器扩展的动态扫描键盘输入方式进行了重点讨论和分析。

2016-03-28 17:59:03 6

6

6

6动态显示-译码器片选实现【C语言】

动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】

2015-12-29 15:51:36 0

0

0

0基于FPGA的RS码译码器的设计

介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构实现

2013-01-25 16:43:46 68

68

68

68基于FPGA的高速RS编译码器实现

本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45

45

45基于ME算法的RS译码器VLSI高速实现方法

利用ME算法实现结构设计了一种低资源占用率、低成本的高速RS译码器。逻辑综合及仿真结果表明,基于Altera公司CycloneII系列FPGA的RS(255,239)译码器,工作时钟达210 MHz,可满足数据速率1.68 Gb

2011-12-15 17:23:28 28

28

28

28WIMAX LDPC码译码器的FPGA实现

本文设计实现了一种支持WIMAX标准的码长、码率可配置LDPC码译码器,通过设计一种基于串行工作模式的运算单元,实现了对该标准中所有码率的支持

2011-06-08 09:52:17 1650

1650

1650

1650

Viterbi译码器回溯算法实现

该文介绍了两种Viterbi 译码器回溯译码算法,通过对这两种算法硬件实现结构上的优化,给出了这两种算法的FPGA 实现方法,比较了两种实现方法的优缺点。最后将其应用在实际的Viter

2011-05-28 15:18:48 33

33

33

33短帧Turbo译码器的FPGA实现

Turbo码虽然具有优异的译码性能,但是由于其译码复杂度高,译码延时大等问题,严重制约了Turbo码在高速通信系统中的应用。因此,如何设计一个简单有效的译码器是目前Turb

2010-11-25 10:10:26 1677

1677

1677

1677

基带芯片中Viterbi译码器的研究与实现

基于对传统Viterbi 译码器的分析和对改进的Viterbi 算法理论的修正,提出了一种新的Viterbi 译码器的实现方法。通过对路径度量值的深入分析和对回溯信息的重新编码,在不增加硬

2009-08-13 10:43:19 23

23

23

23IEEE 802.16e中LDPC译码器的实现

面向IEEE 802.16e 中 LDPC 码,分析了各种译码算法的译码性能,归一化最小(NMS)算法具备较高译码性能和实现复杂度低的特点。提出一种基于部分并行方式的LDPC 译码器结构,可以满

2009-08-05 08:46:59 23

23

23

23用TMS320C54X 实现Vertibi 译码器1

主要介绍卷积编码器和Vertibi 译码器的基本原理。对用TMS320C54X DSP 来实现Vertibi译码器中的两个主要环节——度量值更新和回溯, 作了详细说明, 并给出具体的实现程序。

2009-05-15 16:22:43 21

21

21

21译码器的定义及功能

译码器的定义及功能

译码是编码的逆过程,它的功能是将具有特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路称为译码器

2009-04-07 10:23:42 15826

15826

15826

15826

译码器和数据选择器

实验四 译码器和数据选择器一、 实验目的熟悉集成译码器、数据选择器,了解其应用二、 实验器材双踪示波器74LS139 2-4线译码器 &nb

2009-03-20 17:57:08 37

37

37

377段数码管译码器设计与实现

实验二 7段数码管译码器设计与实现[实验目的]熟悉VHDL语言的语法规范了解模块之间的连接[重点和难点]VHDL语言中port map的使用模块化设计方法[设备器材]

2009-03-14 17:26:19 126

126

126

126 电子发烧友App

电子发烧友App

评论