The CD4042BM/CD4042BC quad clocked ``D' latch is amonolithic complementary MOS (CMOS) integrated

2009-08-08 09:51:32 53

53 电子发烧友网为你提供TI(ti)CD4042B-MIL相关产品参数、数据手册,更有CD4042B-MIL的引脚图、接线图、封装手册、中文资料、英文资料,CD4042B-MIL真值表,CD4042B-MIL管脚等资料,希望可以帮助到广大的电子工程师们。

2018-11-02 19:16:06

CD4013 双D触发器 *CD4027 双JK触发器 *CD4042 四锁存D型触发器 *CD4043

2006-04-17 21:18:32 3219

3219 锁存器,锁存器是什么意思

锁存器定义一位钟控D触发器只能传送或存储一位二进制数据,而在实际工作中往往是一次传送或存

2010-03-09 09:44:12 11794

11794 你好什么是FPGA IO引脚的扇出....我正在使用LVTTL 3.3信号电平...我想将FPGA连接到比较器的锁存信号....我有32个比较器需要从FPGA给出锁存信号....问候,维诺德

2020-06-02 14:22:53

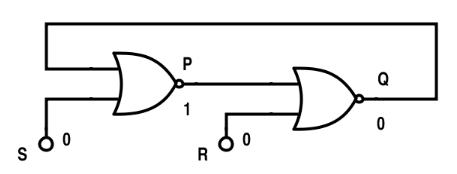

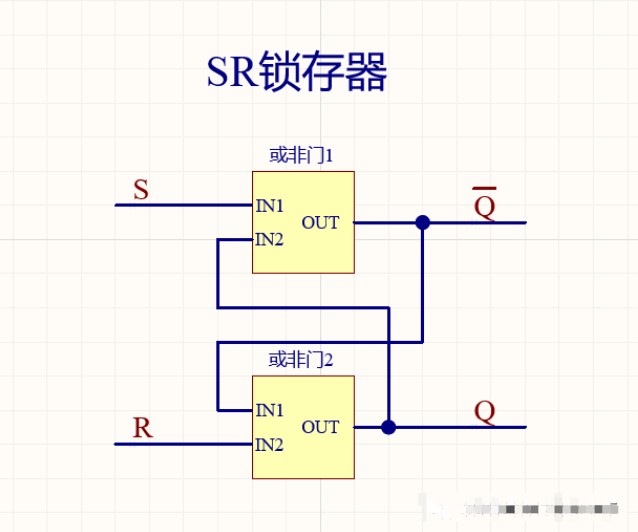

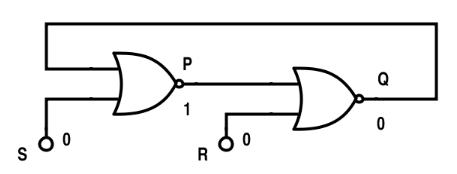

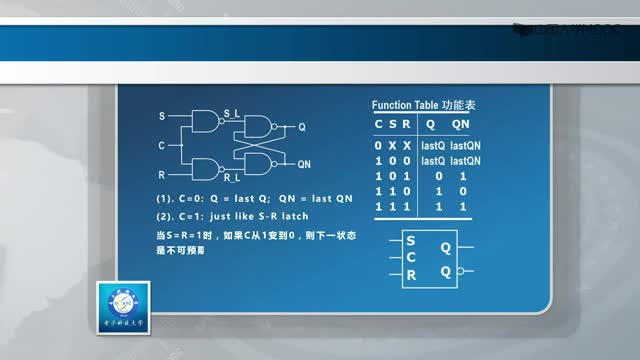

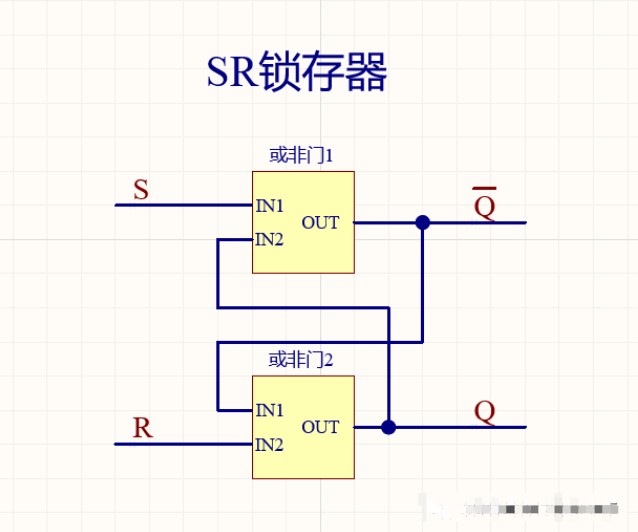

用或非门组成的基本SR锁存器。

2023-02-27 10:29:42 3582

3582

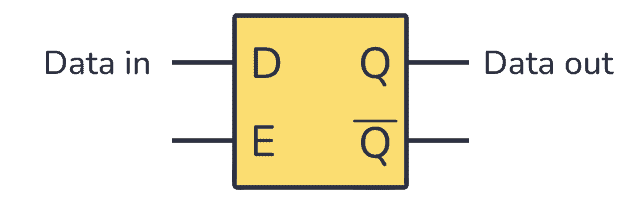

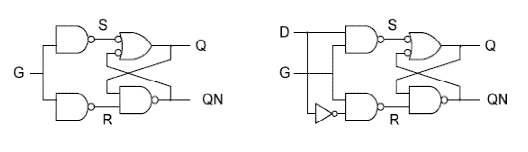

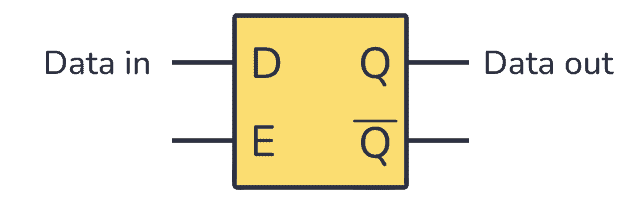

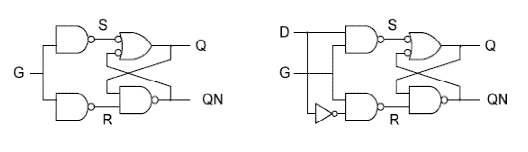

D锁存器是最常用于在数字系统中存储数据的逻辑电路。它基于 S-R锁存器,但没有“未定义”或“无效”状态问题。在本教程中,您将了解它的工作原理、其真值表以及如何使用逻辑门构建一个。

2023-06-29 14:14:03 1246

1246

1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 233

233 所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。 PS:锁存信号(即对LE赋高电平时Data端的输入信号)。锁存,就是把信号暂存以维持某种电平状态。

2017-10-30 14:35:53 58733

58733

地址锁存器,地址锁存器是什么意思

地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数

2010-03-09 09:49:49 4547

4547 一、SR锁存器 1、RS锁存器的电路结构及工作原理 RS锁存器是一两输入、两输出的电路,其电路如图1(a),其有两个互相交叉反馈相连的两个与非门构成,其两个输出为两个相反的输出(或称为互补输出),图

2020-10-07 15:24:00 42935

42935

D锁存器使用基本单元作为存储部件,但它只允许在时序控制信号有效时才能改变(或编程)存储器存储的逻辑值。因此,D锁存器有两个输入时序控制信号和数据输入。

2017-11-24 10:43:10 78724

78724

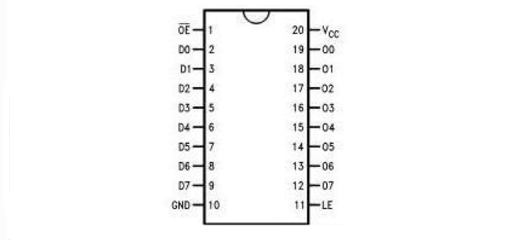

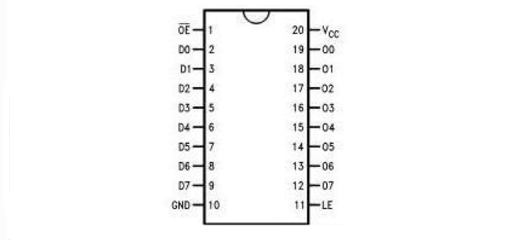

P0口作为分时复用接口,既要作为数据总线口,又要作为地址总线口 输出的低8位地址需要用8位锁存器锁存 ALE的下降沿将P0口输出的低8位地址锁存• 对于锁存器: ○ /OE为输出使能端 § /OE

2021-11-26 20:51:04 11

11 本文开始介绍了什么是锁存器与锁存器的工作原理,其次介绍了锁存器的作用与锁存器的应用实例,最后介绍了常用74系列锁存器芯片介绍。

2018-01-31 16:30:53 75002

75002

本文首先介绍了锁存器的工作原理,其次阐述了锁存器的作用,最后阐述了锁存器应用场合。

2018-08-21 18:57:52 86606

86606 字电路设计、计算机组成原理、自动控制等领域得到广泛应用。常见的锁存器包括SR锁存器、D锁存器、JK锁存器、T锁存器等。

2023-04-09 18:45:34 4102

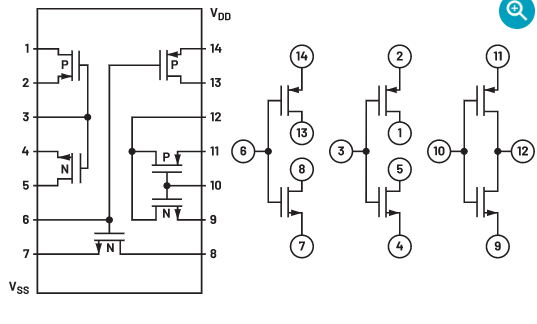

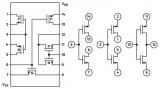

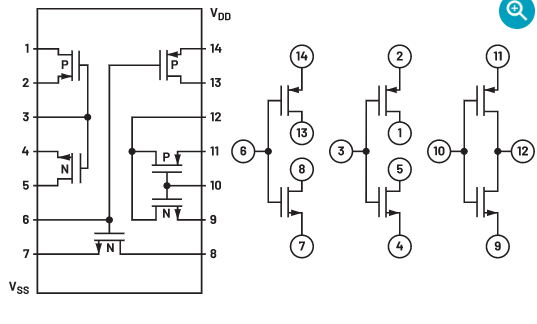

4102 本实验活动的目标是进一步强化上一个实验活动 “ADALM2000实验:使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建D型触发器或锁存器。

2023-05-29 14:16:27 345

345

一种单锁存器CMOS三值D型边沿触发器设计

2017-01-17 19:54:24 22

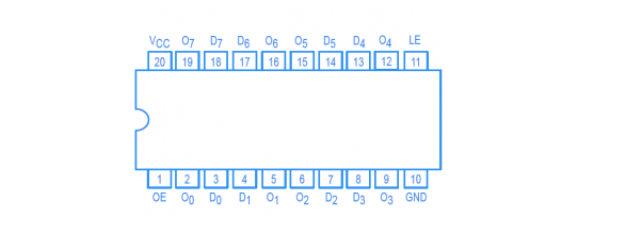

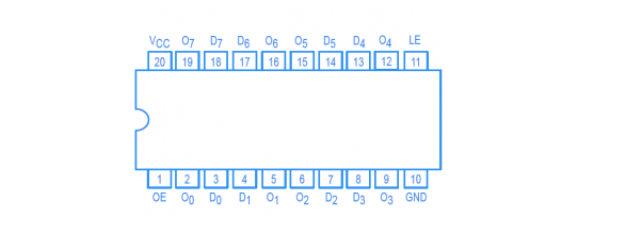

22 AiP74LVC573由8个D型锁存器组成,每个锁存器具有独立的D型输入以及面向总线应用的三态输出。所有内部锁存器共用一个锁存使能(LE)输入和一个输出使能(OE)输入。 当LE为高电平时,Dn输入

2022-02-21 15:46:10 5

5 20位总线接口D型锁存器;三态-74ALVCH16841

2023-02-21 18:51:23 0

0 八路D型透明锁存器;三态-74AHC373

2023-02-20 20:09:49 0

0 16位透明D型锁存器;三态-74ALVT16373

2023-02-16 19:51:26 0

0 前言 在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数

2020-11-16 11:42:00 7206

7206

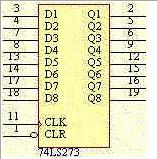

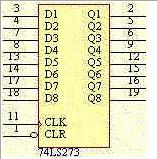

地址锁存器--74LS273

74LS273是带清除端的八D触发器,只有清除端为高电平时才具有锁存功能,锁存控制端为11脚CLK,在上升沿锁存。单片机的ALE端输出的锁存控制信号必须经反

2009-03-14 15:37:57 4529

4529

八路D型透明锁存器;三态-74ALVC373

2023-02-16 20:38:23 0

0 八路D型透明锁存器;三态-74ALVC573

2023-02-16 20:36:43 0

0 18 位总线接口 D 型锁存器;三态-74ALVCH16843

2023-02-23 19:08:01 0

0 锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 1357

1357

CD4042B types contain four latch circuits, each strobed by a common clock. Complementary buffered

2010-08-03 14:14:42 26

26 锁存器的原理分析

锁存器就是把单片机的输出的数先存起来,可以让单片机继续做其它事.. 比如74HC373就是一种锁存器 它的LE为高

2010-03-09 09:54:52 66975

66975 CMOS 四路时钟控制“D”锁存器 Number of channels (#) 4 Technology Family CD4000 Supply voltage (Min

2022-12-12 15:19:30

锁存器(Latch)是一种对脉冲电平敏感的存储单元,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。

2023-07-06 15:10:39 344

344

IC 74LS373 是一款透明锁存器,由 20 个锁存器和 0 个状态输出组成,适用于总线组织系统应用。它是一款 7 引脚 IC,由 0条输入数据线 (D7-D74) 和 373 条输出线 (O

2023-07-03 10:23:41 767

767

当复位输入为假且锁存输入为真时,输出为真。无论锁存器输入如何,输出仍然是真实的,直到复位输入为真。

2019-02-11 08:00:00 6

6 锁存器是具有两个稳定状态的时序逻辑电路,即它是双稳态多谐振荡器。锁存器有一个反馈路径来保留信息。因此,锁存器可以是存储设备。只要设备处于开机状态,锁存器就可以存储一位信息。当使能启用时,锁存器会在输入更改时立即更改存储的信息,即它们是电平触发设备。当使能信号打开时,它会持续对输入进行采样。

2022-09-12 16:13:00 6069

6069

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48:13 28618

28618

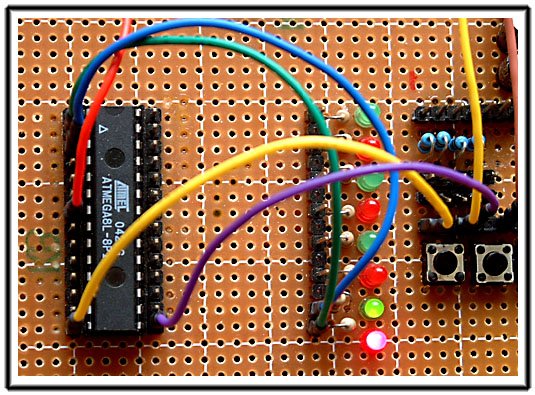

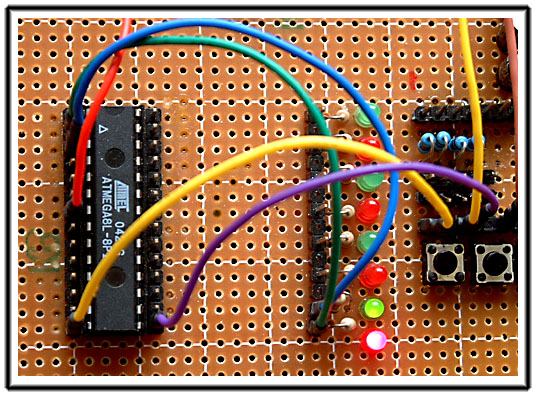

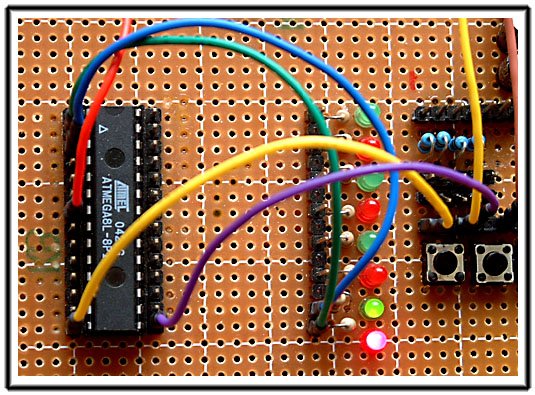

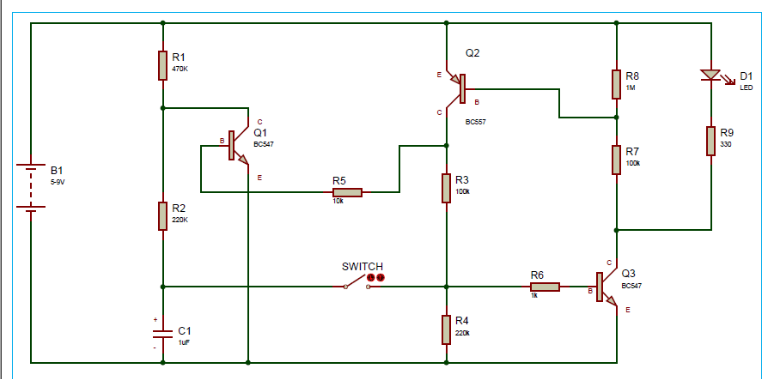

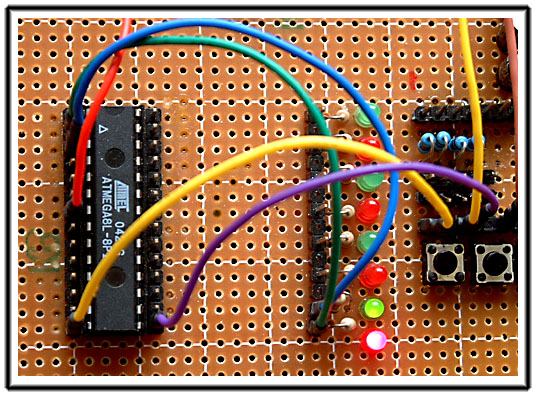

8路键盘D触发锁存器的制作

实现目的:

当管脚设定为输入时,了解如何可以编程设定上拉电阻,以达到简化硬件的目的。

2010-05-12 10:06:48 1016

1016

SL74hc573中文资料(三态输出的八D透明锁存器),原理图及各篇573详细介绍。

2015-12-31 14:26:51 24

24 CD4511是一片CMOSBCD锁存/7段译码/驱动器,用于驱动共阴极LED(数码管)显示器的BCD码-七段码译码器。具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉

2017-11-22 19:54:23 57635

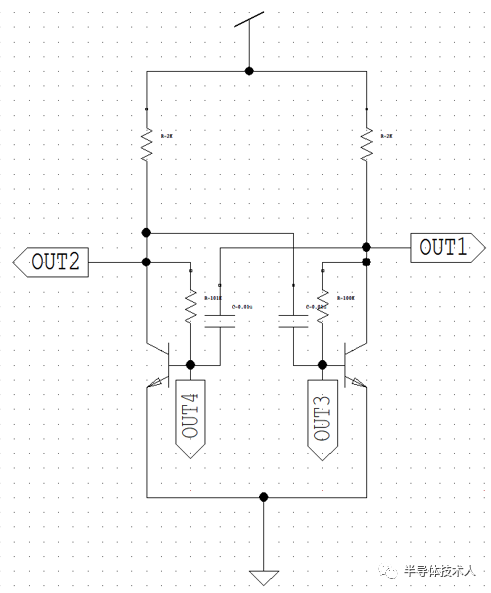

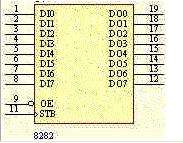

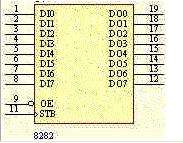

57635 地址锁存器--8282

8282是带有三态门的八D锁存器,当使能信号线OE为低电平时,三态门处于导通状态,允许1Q-8Q输出到OUT1-OUT8,当OE端为高电平时,输出三态门断开,输出线OUT1-O

2009-03-14 15:37:24 8894

8894

一组输出,当前什么输入就根据函数得到什么输出,实时跟踪变化,这样也就容易有冒险、竞争之类的问题产生毛刺。 锁存器:电平敏感 always @ (enable) ??if (enable) ?q 《= d; 那就是说,在enable有效的时间内,q完全跟踪d的值,

2021-08-12 10:26:12 3567

3567 本实验活动的目标是进一步强化上一个实验活动“ADALM2000实验:使用CD4007阵列构建CMOS逻辑功能”中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建D型触发器或锁存器。

2023-07-10 09:55:07 164

164

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 92855

92855

八路D型透明锁存器;三态-74HC_HCT373_Q100

2023-02-17 19:51:12 0

0 3.3 V 八进制 D 型透明锁存器;三态-74LVT573

2023-02-15 20:08:01 0

0 低功耗D型透明锁存器;三态-74AUP1G373

2023-02-14 18:49:37 0

0 八路D型透明锁存器;三态-74HC_HCT573_Q100

2023-02-17 18:36:15 0

0 八路D型透明锁存器;三态-74HC_HCT573

2023-02-15 19:36:03 0

0 八路D型透明锁存器;三态-74AHC_AHCT573_Q100

2023-02-17 19:53:45 0

0 低功耗D型透明锁存器;三态-74AUP1G373_Q100

2023-02-14 18:49:25 0

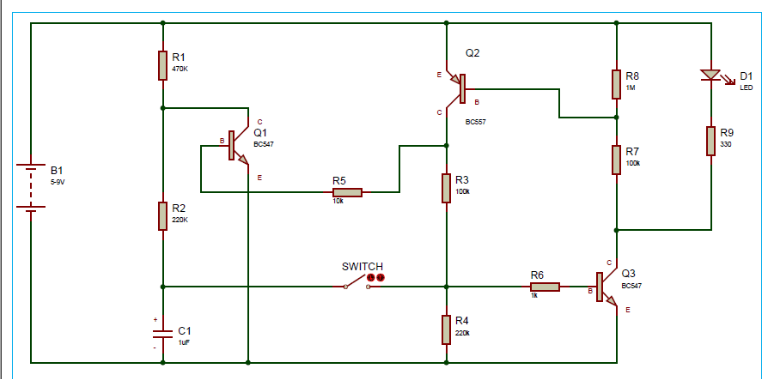

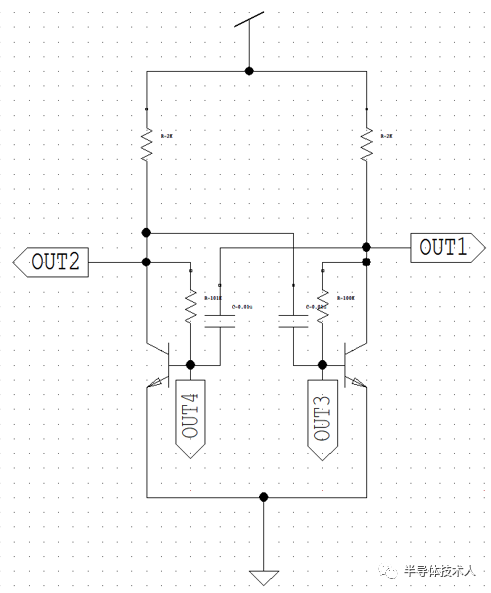

0 在这个项目中,我们将制作一个软锁存电路,通过按一个按钮来打开和关闭电子设备。该电路称为软锁存开关。软锁存电路与普通锁存电路不同,在软锁存器中,可以使用外部手段(按钮)改变开启和关闭状态,但在普通锁存

2022-08-25 16:32:47 2779

2779

八路D型透明锁存器;三态-74AHC_AHCT573

2023-02-17 19:54:03 0

0 3.3 V 16 位透明 D 型锁存器;三态-74LVT16373A

2023-02-15 20:07:03 0

0 八路D型透明锁存器;三态-74HC_HCT373

2023-02-15 19:42:19 0

0 16位D型透明锁存器;3.6 V 耐受;三态-74AVC16373

2023-02-23 18:56:02 0

0 2.5 V/3.3 V 16位D型透明锁存器;三态-74ALVCH16373

2023-02-15 18:51:06 0

0 ATMEGA8设计的8路键盘D触发锁存器

实现目的:

当管脚设定为输入时,了解如何可以编程设定

2010-02-09 17:47:35 1446

1446

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题

2018-01-31 13:57:22 11284

11284

作为电路设计者,锁存器很多场合都会用到,今天和大家分析一下SR锁存器的原理。

2022-08-20 17:30:23 5589

5589

作者:电子工程师小李 1)锁存器 锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。 简单地说

2020-11-29 11:02:11 20662

20662

正在加载...

电子发烧友App

电子发烧友App

评论