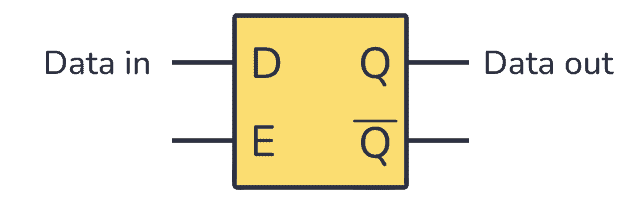

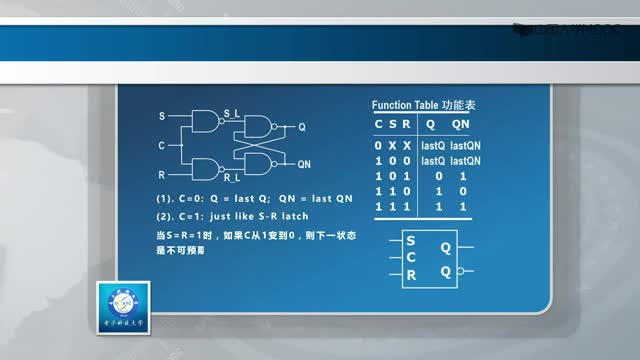

基本单元是最基础的存储器器件,并在特定的情况下发挥着重要的作用。但是,如果在一个基本单元上再加上两个逻辑门,那么就可以构造出更有用的存储器器件,该器件就称为D锁存器。

D锁存器使用基本单元作为存储部件,但它只允许在时序控制信号有效时才能改变(或编程)存储器存储的逻辑值。因此,D锁存器有两个输入时序控制信号和数据输入。

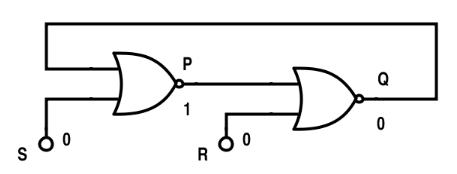

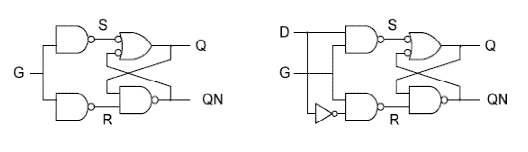

时序控制信号,通常也称为“门信号”,或“时钟”,或是“锁存使能”,主要用于同步新数据何时可以写入存储器,何时不能写入。如下图左图所示,可以看出当门信号无效时,S和R信号为1且输出Q由存储在基本单元反馈回路的值决定(所以Q就是存储的逻辑值)。再看右图,可以看出当门信号有效时,D(数据)输入将S和R驱动到各自相反的电平,从而在基本单元中强制了一个置位或复位操作。通过组合时序信号和数据输入信号来强制基本单元的置位或复位操作,我们就构造出了一个非常有用的存储器器件。D锁存器已经广泛使用在所有类型的现代数字电路中了。

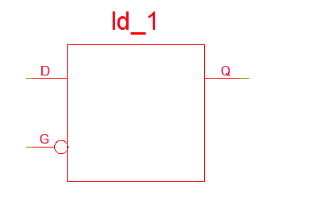

如下图所示为D锁存器时序方框图。注意,当门信号有效时,输出Q只是简单的“跟随”输入。但是当门信号无效时,输出“记住”了门信号下降沿时的D值。

d锁存器时序方框图

1、 在G有效前,Q未定义;Q有效时,Q得到D的值

2、 G无效而D有效,Q不改变

3、 D和G都有效;Q得到D的值

4、 G下降沿;Q存储了D值

5、 D下降沿,而G无效,Q值不改变

6、 G有效,Q得到D值

7、 G有效时,Q跟随D值

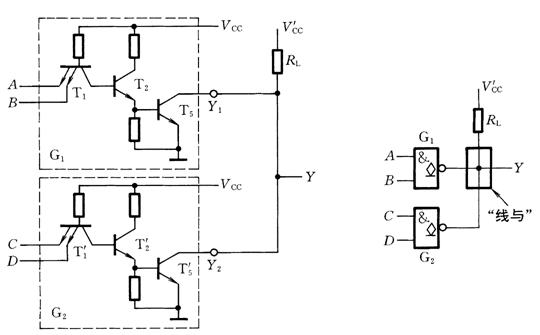

左右可用的存储器器件都至少有两个输入-一个是需要存储的数据输入,还有一个是时序控制输入以定义数据信号存储的确切时间。如图所示,存储器器件的当前输出称为“当前状态”,而输入称为“下一状态”。这是因为输入定义了下一个时序控制信号有效时的存储值。在D锁存器中,只要时序控制信号有效,那么当前状态和下一状态是完全相同的。而D触发器在本质上修改了D锁存器这一功能:即下一状态(D输入)只能在时序信号的沿(信号转换时)上才能被写入到存储器中。

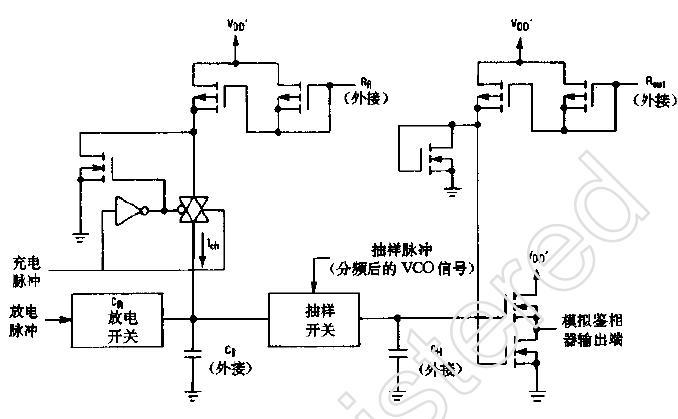

D触发器(DFF)是最基本的存储器件。DFF一般有三个输入:定义下一状态的数据输入;告诉触发器何时存储输入数据的时序控制输入;以及产生存储器复位到0而不考虑其它两个输入的复位输入。DFF中的“D”来自data input;因此,触发器也可称为数据触发器。时序控制输入,称为“时钟”,用于同步新数据何时可以写入存储器,而何时又不可以写入。时钟信号一般是一个方波并以某一频率规则的重复。当有一个有效时钟沿时,DFF记录(寄存)下新数据-有效沿既可以是上升沿,也可以是下降沿。上升沿触发(RET)的DFF符号使用一个小三角来表示该触发器是边沿触发的;下降沿触发(FET)的DFF符号也用一个小三角表示,但要在表示触发器方框的外面,小三角的旁边加一个小圆圈(就像是其它那些低有效输入的符号)。如下图所示的时序图表明了RET DFF的行为特性。注意,输出Q只在时钟有效边沿上改变,且复位信号可以强制输出为0,而与其它两个输入信号无关。

由于存在基本单元,D触发器和D锁存器在其输入同时改变时,都有可能进入亚稳定态。在D锁存器中,当控制信号无效时,数据必须是稳定的。在D触发器中,当时钟沿出现时,该沿之前或之后很短时间内,数据输入必须是稳定的。如果在时钟沿上输入数据不稳定,那么一个亚稳定态就有可能随着时钟节拍进入了存储器单元中。如果这种情况发生,存储器单元可能不能够立即解决问题并进入到低电平或高电平上,那么就有可能振荡一段时间。因此,当使用沿触发器设计电路时,一定要保证在时钟沿到来之前和之后一段时间内,输入数据是稳定的(即我们知道的建立时间和保持时间)。建立时间和保持时间在几十皮秒(单片集成IC设计中)到几纳秒(分立逻辑芯片设计中)之间不等。

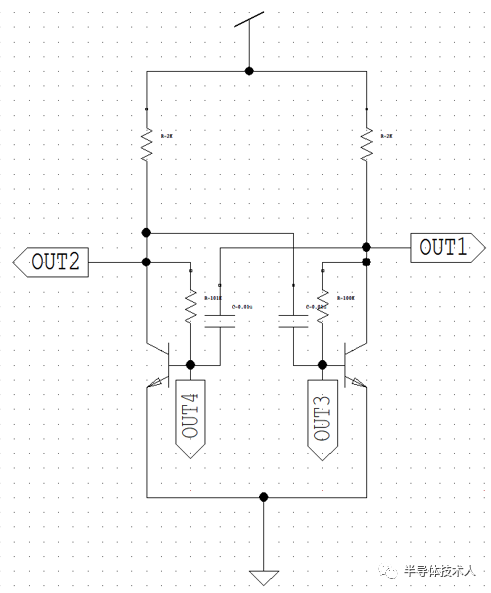

基本D触发器的原理图如右图所示。在不同的参考中各原理图都会稍有不同,但只要是DFF,那么其行为特性就一定相同。

d锁存器逻辑图

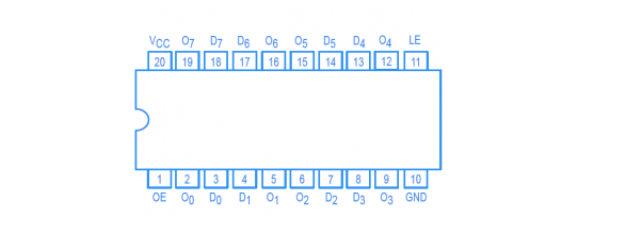

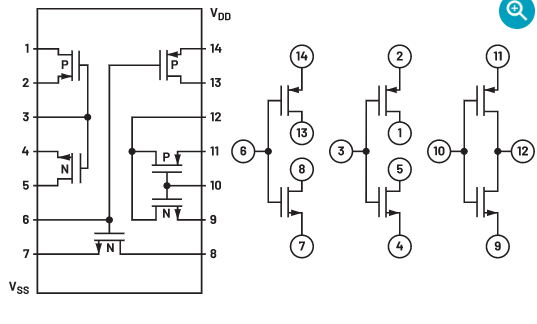

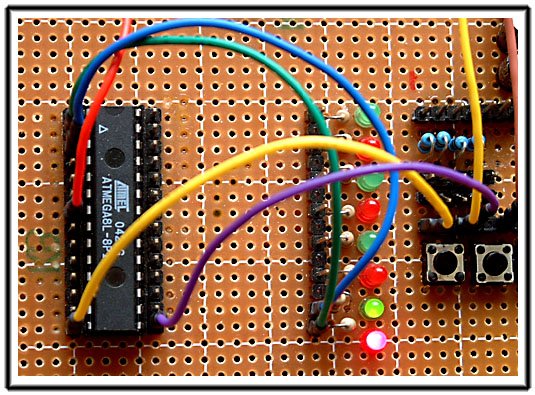

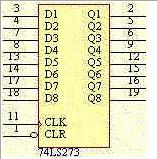

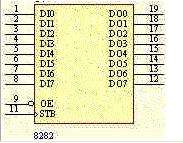

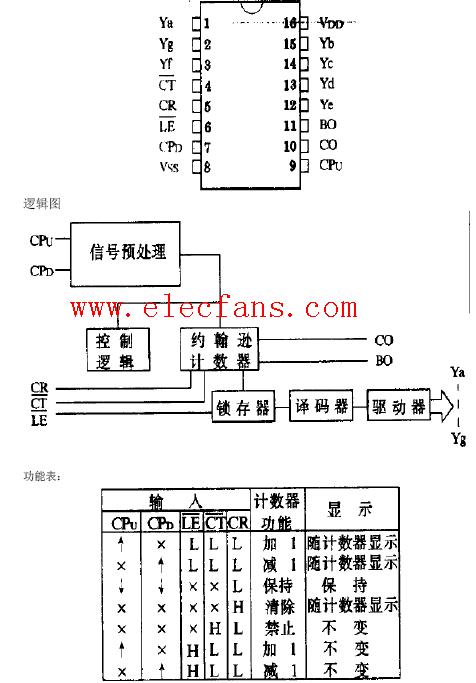

8位锁存器74LS373的逻辑图见图所示。其中使能端G加入CP信号,D为数据信号。输出控制信号为0时,锁存器的数据通过三态门进行输出。

电子发烧友App

电子发烧友App

评论