数字电路简介:

用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。现代的数字电路由半导体工艺制成的若干数字集成器件构造而成。逻辑门是数字逻辑电路的基本单元。存储器是用来存储二进制数据的数字电路。

数字电路特点:

1、 同时具有算术运算和逻辑运算功能

数字电路是以二进制逻辑代数为数学基础,使用二进制数字信号,既能进行算术运算又能方便地进行逻辑运算(与、或、非、判断、比较、处理等),因此极其适合于运算、比较、存储、传输、控制、决策等应用。

2、 实现简单,系统可靠

以二进制作为基础的数字逻辑电路,可靠性较强。电源电压的小的波动对其没有影响,温度和工艺偏差对其工作的可靠性影响也比模拟电路小得多。

3、 集成度高,功能实现容易

集成度高,体积小,功耗低是数字电路突出的优点之一。电路的设计、维修、维护灵活方便,随着集成电路技术的高速发展,数字逻辑电路的集成度越来越高,集成电路块的功能随着小规模集成电路(SSI)、中规模集成电路(MSI)、大规模集成电路(LSI)、超大规模集成电路(VLSI)的发展也从元件级、器件级、部件级、板卡级上升到系统级。电路的设计组成只需采用一些标准的集成电路块单元连接而成。对于非标准的特殊电路还可以使用可编程序逻辑阵列电路,通过编程的方法实现任意的逻辑功能。

数字电路的划分:

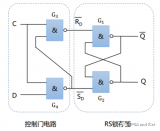

1.按功能分为组合逻辑电路和时序逻辑电路两大类。

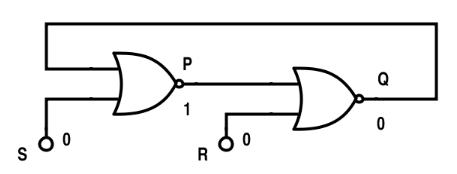

前者在任何时刻的输出,仅取决于电路此刻的输入状态,而与电路过去的状态无关,它们不具有记忆功能。常用的组合逻辑器件有加法器、译码器、数据选择器等。后者在任何时候的输出,不仅取决于电路此刻的输入状态,而且与电路过去的状态有关,它们具有记忆功能。

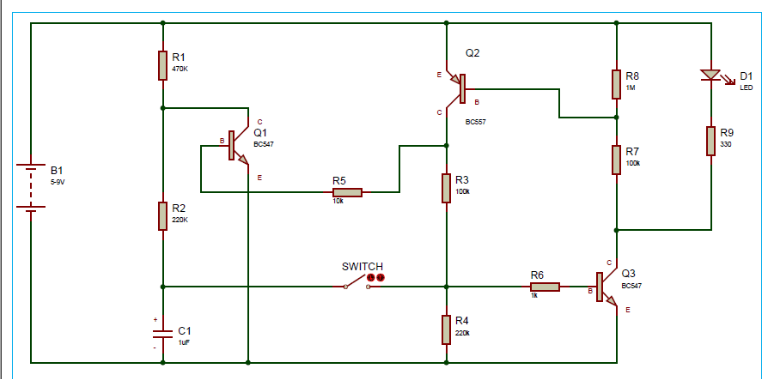

2.按结构分为分立元件电路和集成电路。

前者是将独立的晶体管、电阻等元器件用导线连接起来的电路。后者将元器件及导线制作在半导体硅片上,封装在一个壳体内,并焊出引线的电路。集成电路的集成度是不同的。

数字电路中如何避免产生不必要的锁存器方法解析:

1. if……else……结构中缺少else

先看一个实际的例子:

用quartus综合一下这两个电路,看看产生的RTL图是怎样的:

左边的电路:

右边的电路:

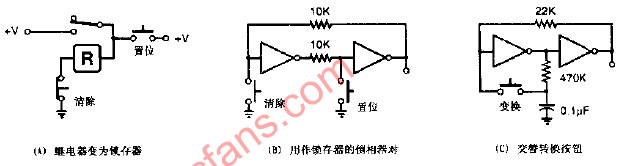

由RTL视图可以直观的看出,左边的电路没有生成锁存器,而右边的电路生成了一个我们不想要的锁存器(q1$latch)。左边的电路是时序逻辑,生成触发器,而触发器是有使能端(en)的,使能端无效时就可以保存数据,无需锁存器。右边的电路是组合逻辑,在en为低电平时,输出q1要保持不变,而组合逻辑没有存储元件,只能生成锁存器来保持数据。所以在时序逻辑中,不完整的 if…else… 结构并不会生成锁存器,而组合逻辑中不完整的 if…else… 结构就会生成锁存器。为了避免我们设计的组合逻辑中出现不想要的锁存器,在使用 if…else… 结构时一定要写完整。把刚才例子中右边的电路写完整,并查看其RTL视图如下:

写完整后,就没有生成锁存器,而是生成了一个二选一的选择器,这正是我们想要设计的。

2. case结构中的分支没有包含所有情况且没有default语句

case结构中一般要加上default语句,以保证出现意外情况也可以作出相应的反应。如果没有加default并且case分支不完整,当出现case分支中没有列出的情况时,电路状态保持原来的状态不变,于是就会生成锁存器来保存状态,如下图的电路所示:

图中case分支中只写了(se=0)的情况,而(se=1)的情况未给出,且没有写default,于是当(se=1)时,q1保持原来的值不变,这样就产生了锁存器(q1$latch)。

如果将case分支补全,或者加上default语句,则如下图所示:

补全case分支后,就不会生成锁存器了。

同样,只有在组合逻辑中的case结构才有可能产生锁存器,而在时序逻辑电路中,即使case结构中的分支不完整,也不会产生锁存器,如下图所示:

实际上,在时序逻辑中,由于触发器具有锁存数据的功能,所以不会生成锁存器,锁存器只会在组合逻辑电路中产生。

因此,在设计组合逻辑电路时,要注意将 if…else… 结构中的else写完整,case结构中一定要加上default语句,这样可以减少综合出锁存器的可能性。

电子发烧友App

电子发烧友App

评论