什么是异步复位和同步释放:

是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

下面说明一下如何实现异步复位和同步释放的。

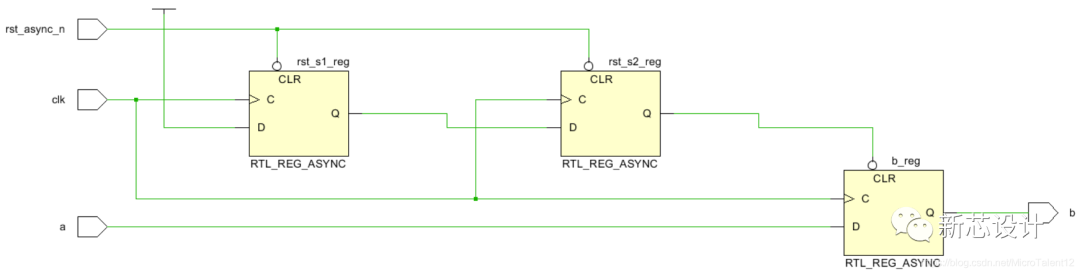

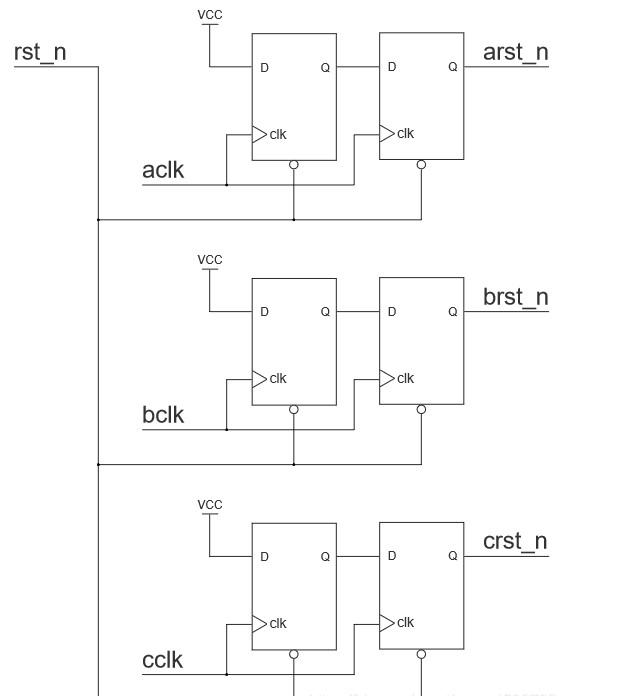

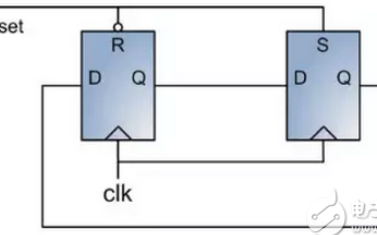

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路(双寄存器)的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件,但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器1输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器clk来之前时的Q1输出状态。显然Q1之前为低电平,顾第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

如图第一个方框内是异步复位和同步释放电路。有两个D触发器构成。第一级D触发器的输入时VCC,第二级触发器输出是可以异步复位,同步释放后的复位信号。

电路目的:方式复位信号撤除时产生亚稳态事件。

所谓异步复位和同步释放,是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除(释放)则与clk相关,即同步的。

代码实现:

always @ (posedge clk, negedge rst_async_n)

if (!rst_async_n) begin

rst_s1 《= 1‘b0;

rst_s2 《= 1’b0;

end

else begin

rst_s1 《= 1‘b1;

rst_s2 《= rst_s1;

end

assign rst_sync_n = rst_s2;

endmodule

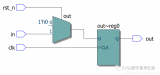

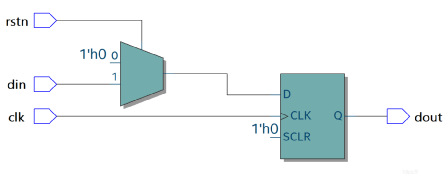

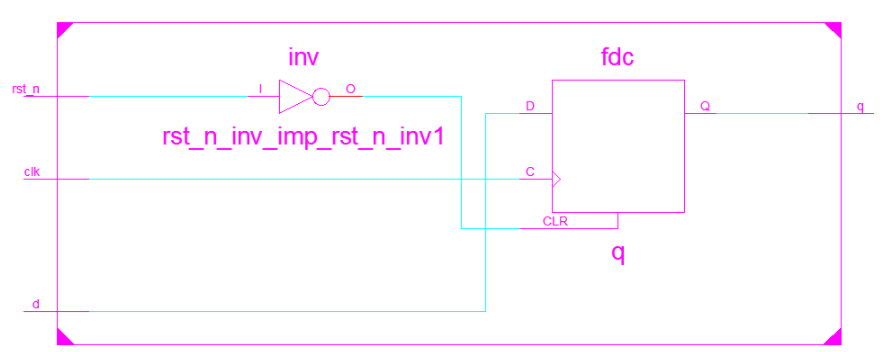

对于实际的实现TECH MAP视图

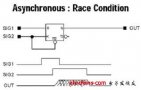

其实异步复位的话,优点就是可以直接用EDA工具综合库DFF的异步复位端,相对同步复位来说又简单又省逻辑资源,但其致命缺点就是复位结束也就是释放的时刻恰在时钟上升沿的建立时间和保持时间之间时无法决定现在的复位状态是1还是0,造成亚稳态。

试想下,如果这样的复位信号应用在一个大的系统中,复位信号路径到每一个模块乃至到每一个寄存器的偏斜都会不同,如果恰在时钟上升沿时刻附近必然引起诸多问题。

因此最好全局复位信号送出之前做一个“异步复位,同步释放”的处理。

下面是常见两种方式:

方式一:(自己看来应该是“异步复位同步化”)

always @ (posedge clk)

rst_nr 《= rst_n; //现将异步复位信号用同步时钟打一拍

always @ (posedge clk or negedge rst_nr)

if(!rst_nr) b 《= 1‘b0;

else b 《= a;

方式二:(自己看来才是“异步复位,同步释放”)

reg pllrst1,pllrst2;

wire pllrst;

always @(posedge clk or negedge rst_n)

if(!rst_n) begin pllrst1 《= 1’b1;

pllrst2 《= 1‘b1; end

else begin pllrst1 《= 1’b0;

pllrst2 《= pllrst1; end

assign pllrst = pllrst2; //锁相环复位信号

电子发烧友App

电子发烧友App

评论