异步复位信号亚稳态的原因:

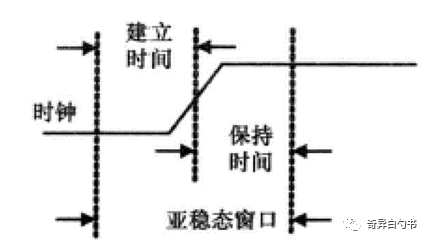

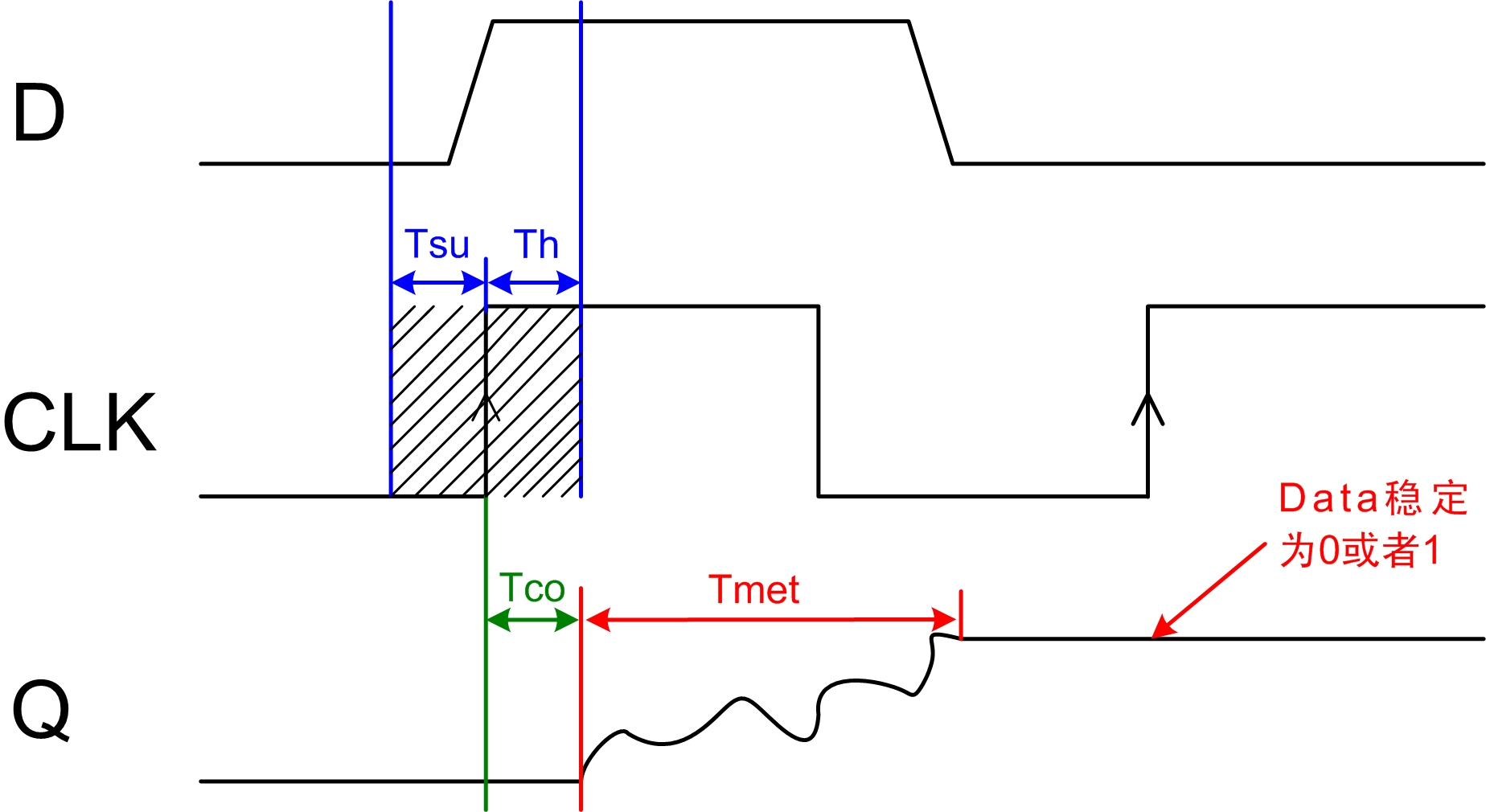

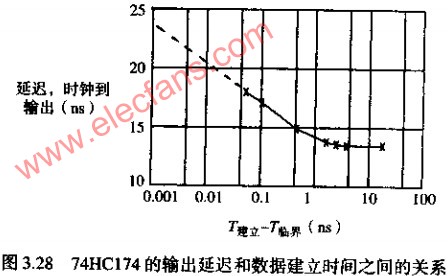

复位结束也就是释放的时刻恰在时钟上升沿的建立时间和保持时间之间时无法决定现在的复位状态是1还是0,造成亚稳态。

下面是具体解释:

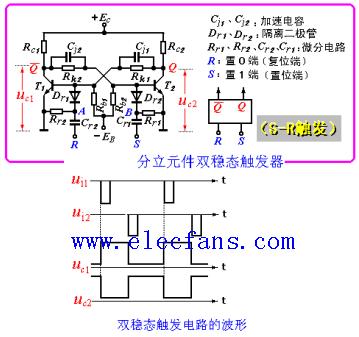

在带有复位端的D触发器中,当reset信号“复位”有效时,它可以直接驱动最后一级的与非门,令Q端“异步”置位为“1”or“0”。这就是异步复位。当这个复位信号release时,Q的输出由前一级的内部输出决定。

然而,由于复位信号不仅直接作用于最后一级门,而且也会做为前级电路的一个输入信号,因此这个前一级的内部输出也受到复位信号的影响。前一级的内部电路实际上是实现了一个“保持”的功能,即在时钟沿跳变附近锁住当时的输入值,使得在时钟变为高电平时不再受输入信号的影响。

对于这一个“维持”电路,在时钟沿变化附近,如果“reset”信号有效,那么,就会锁存住“reset”的值;如果reset信号释放,那么这个“维持”电路会去锁当时的D输入端的数据。因此,如果reset信号的“释放”发生在靠时钟沿很近的时间点,那么这个“维持”电路就可能既没有足够时间“维持”住reset值,也没有足够时间“维持”住D输入端的值,因此造成亚稳态,并通过最后一级与非门传到Q端输出。如果reset信号的“释放”时间能够晚一点点,也就是说,让“维持”电路有足够的时间去锁住“reset”的值,那么,我们就可以肯定输出为稳定的“reset”状态了。这一小段锁住“reset”值所需要的时间,就是寄存器的removal time要求。

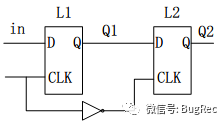

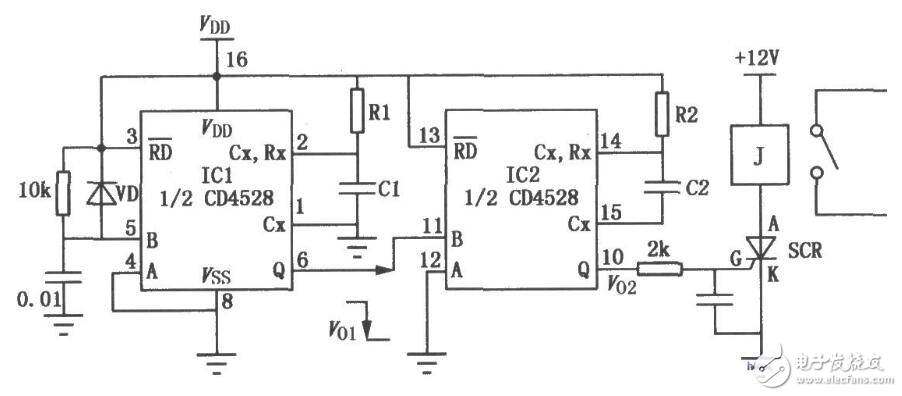

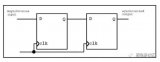

如图第一个方框内是异步复位和同步释放电路。有两个D触发器构成。第一级D触发器的输入时VCC,第二级触发器输出是可以异步复位,同步释放后的复位信号。

利用前面两级触发器实现。特点:

第一级触发器的数据端口是接电源,即高电平1’b1。

第一级触发器的输出,不能使用,因为仍存在亚稳态的危险。两级触发器做同步,是非总线信号的最常见异步处理方法。总线信号的异步处理方法,最常见的是异步fifo实现。

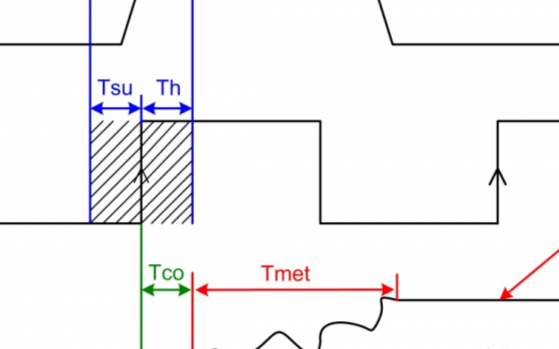

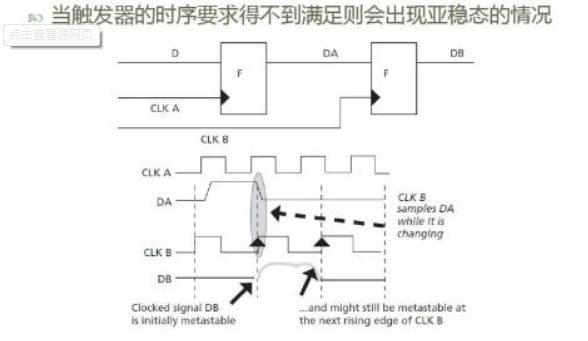

很多人只知道触发器D端口来源是异步的话,会因为建立保持时间的时序违反而在触发器Q端口产生亚稳态。

但是不清楚,异步复位信号为什么会导致亚稳态的产生。

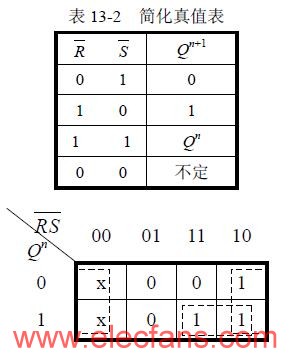

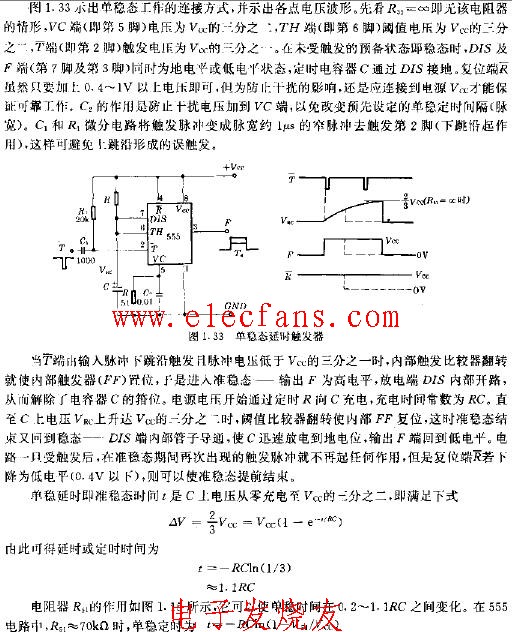

首先,回顾理论教材里介绍的建立保持时间违反分析,教材一般都是拿没有复位端口的D触发器举例。

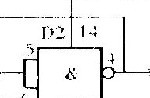

然后,画出带有异步复位端口的D触发器,下图带异步复位Rd,并带有异步置位端口Sd。

由此得知,异步复位信号或者异步置位信号,跟数据端口D信号,没有什么区别,都会存在建立保持时间的违反,从而时序冲突,引发输出亚稳态。

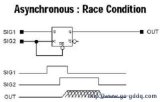

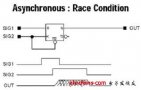

亚稳态,出现的问题或者麻烦,是在信号变化的时候,不能保证第一拍采样的值是固定的。

如果信号稳定,不会出现亚稳态的。就是采样后的跳变,时刻不确定,也许早,也许晚。

系统不希望这样的未知状态发生,系统希望知道在某一个时刻,后续逻辑需要的输入信号,是稳定值。

二级触发器同步后,第二季触发器的输出基本上是稳定值。后续逻辑根据稳定值,会有稳定的行为。这就是追求的系统稳定性。

最好是系统一起复位释放,但是时钟域不同,不可能保证系统一起复位释放。一般来说,系统复位释放的顺序,是需要保证的。否则系统就是不安全的。

举个例子,系统启动时,内核读取启动指令,要powerdown某外设;但是powerdown的逻辑要求外设和内核没有通信请求正在发生。此时,外设比内核先释放复位的情况(复位释放的时刻,外设有可能已经开始与内核发生请求),与内核比外设先释放复位的情况(复位释放的时刻,外设肯定与内核没有发生请求),是不一样的,powerdown也许不能处理成功。

这也是异步复位信号需要同步释放的原因,目的都是为了避免亚稳态的产生。

第一级触发器的输出,永远存在亚稳态的可能。亚稳态,导致系统不会复位初始化到已知状态。

当第一级触发器采样异步输入之后,允许输出出现的亚稳态可以长达一个周期,在这个周期内,亚稳态特性减弱。在第二个时钟沿到来时,第二级同步器采样,之后才把该信号传递到内部逻辑中去。第二级输出是稳定且已被同步了的。如果在第二级采样时保持时间不够,第一级的输出仍然处于很强的亚稳态,将会导致第二级同步器也进入亚稳态,但这种故障出现的概率比较小。

一般情况下,两级同步器总体的故障概率是一级同步器故障概率的平方。在大部分的同步化设计中,两级同步器足以消除所有可能的亚稳态了。

基本D触发器、同步D触发器和异步D触发器的Verilog描述

//基本D触发器

module D_EF(Q,D,CLK)

input D,CLK;

output Q;

reg Q; //在always语句中被赋值的信号要声明为reg类型 寄存器定义

always @ (posedge CLK) //上升沿,下降沿用negedge表示,^_^ 需要记忆

begin Q 《= D; end

endmodule

//带异步清0、异步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;//寄存器定义

always @ (posedge clk or negedge set or negedge reset)

begin

if(!reset) begin q《=0;qn《=1;end//异步清0,低有效

else if(!set) begin q《=1;qn《=1;end //异步置1,低有效

else begin q《=~d;qn《=~d;end

end

endmodule

//带同步清0、同步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;

always @ (posedge clk)

begin

if(reset) begin q《=0;qn《=1;end//同步清0,高有效

else if(set) begin q《=1;qn《=1;end //同步置1,高有效

else begin q《=~d;qn《=~d;end

end

endmodule

电子发烧友App

电子发烧友App

评论