Xilinx大部分的开发板上都集成了Si570时钟芯片,该时钟的性能指标比较好,可以满足大部分高速串行接口应用对于参考时钟的要求。同时该时钟还可以通过I2C接口配置其输出频率。

该专题详细介绍如何给Xilinx 7系列以及Ultrascale系列开发板上的Si570重新配置频率。

Xilinx 7 Series开发板配置详细步骤

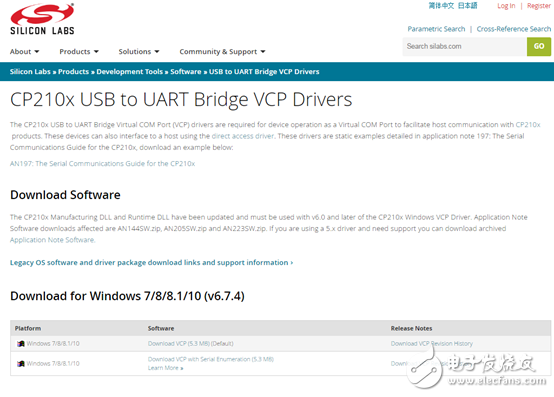

安装USB UART驱动

在Silicon Labs的官网上CP210x USB-to-UART Bridge VCP Drivers 下载页面下载驱动。

下载完成后解压安装。

参考UG1033。

安装Tera Term软件

在Tera Term的下载页面下载软件。

下载完成后进行安装

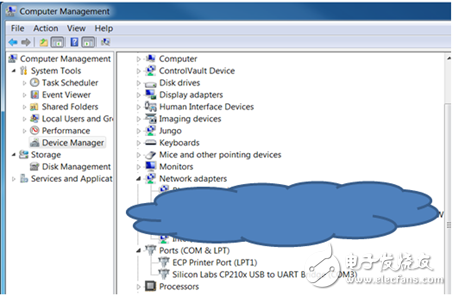

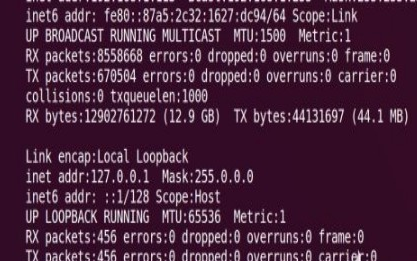

安装完成后接好UART的cable,给FPGA上电,就会自动扫描器件,在Windowsàdevice manager中就出现了UART的信息。这个过程不需要提前向FPGA中下载任何专门的程序。

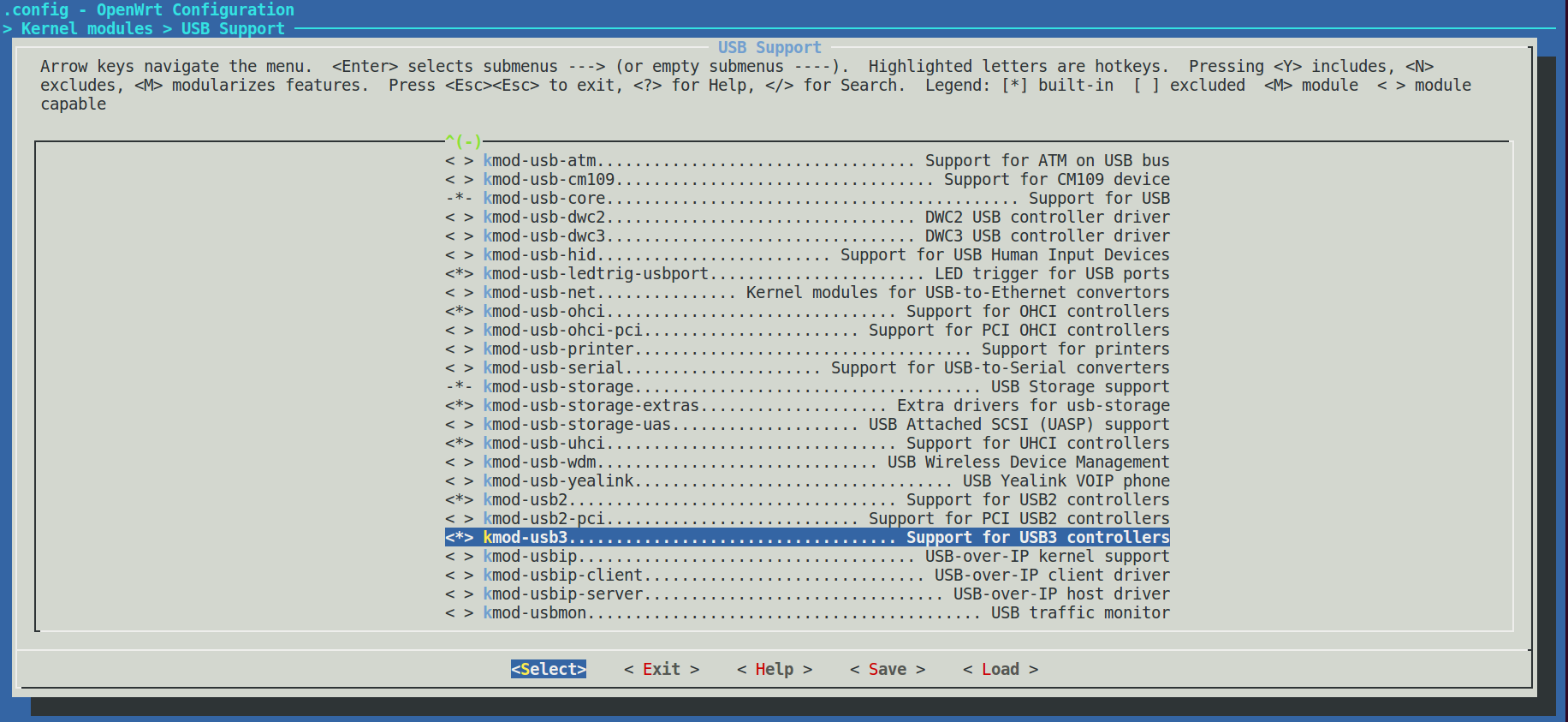

向FPGA加载KC705 Si570 Programming的Bit文件

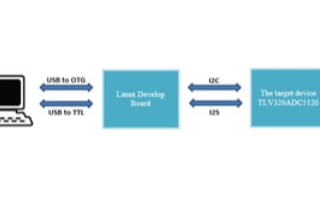

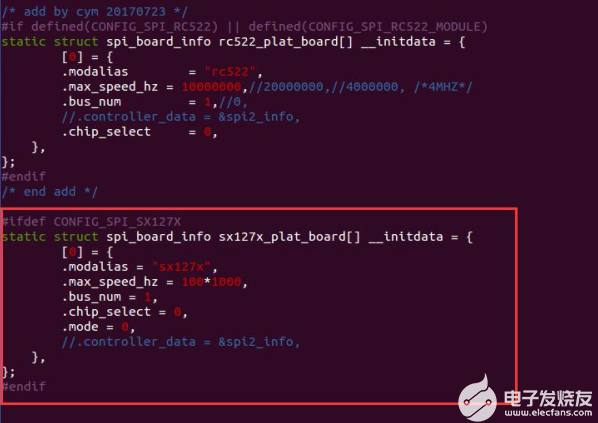

Si570的配置接口为I2C,还是需要通过FPGA间接下载,所以必须在FPGA设计相应的逻辑。通过UART从外部接收指令,经FPGA内部的逻辑控制连接Si570的IO引脚,以I2C的时序向Si570中写命令。

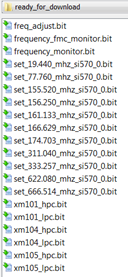

以7系列中的KC705开发板为例,在Xilinx官网上下载KC705 SI570 Programming的压缩包

压缩包中有很多bit文件,如图 6所示。

其中:

与fmc相关的文件暂时不关心。

set_xxx.xx_mhz_si570_0.bit的文件是FPGA直接控制Si570,将其配置到指定频率的程序,其中包含了大部分应用所需要的频率值。

freq_monitor.bit文件的作用只是配着debug_nets.ltx,对Si570的输出频率进行监测。

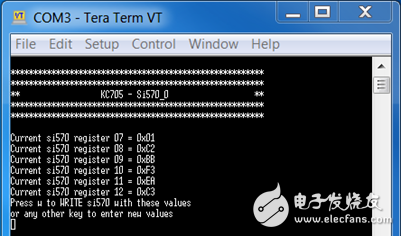

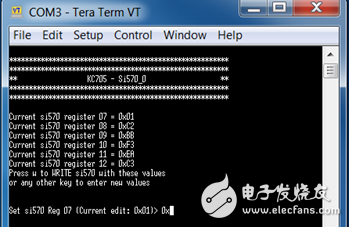

freq_adjust.bit文件的作用可以读取和重新配置Si570中所有寄存器的值,即可以将Si570配置到任意频率的程序,该bit文件下载后首先将当前

Si570芯片内部的寄存器信息读出来,通过串口发送到Tera Term,如图 7所示。

接着可以通过UART,按照指令的顺序配置Si570中各个寄存器的值,简单演示步骤:

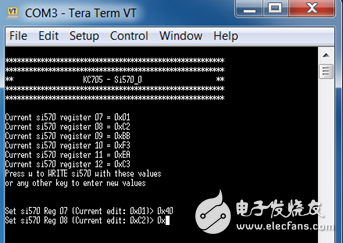

在图 7的基础上按下任意键,Tera Term有新的数据信息。

按照显示的信息提示,输入第一个需要配置寄存器的值。

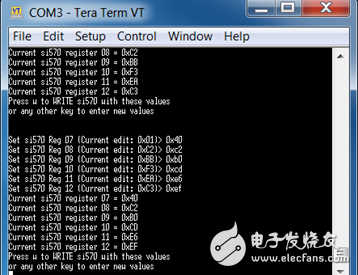

将剩余的寄存器全部按照提示信息输入完成,系统显示新输入的寄存器值,同时提示按下w键将新的值写入Si570。

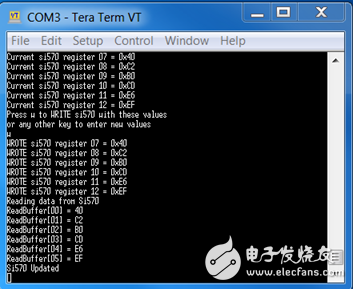

系统自动更新Si570,并显示更新成功。

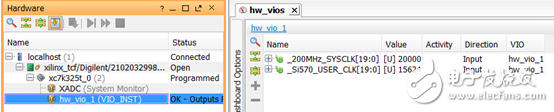

此时回到VIO中,Si570的输出频率已经按照要求改变了。

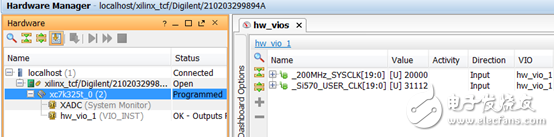

使用VIO Probes检测Si570输出频率

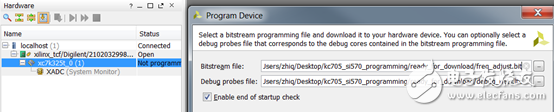

在下载上述bit文件的同时选择上配套的debug_nets.ltx文件。

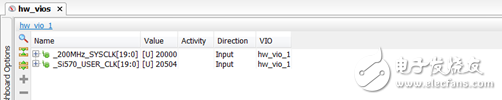

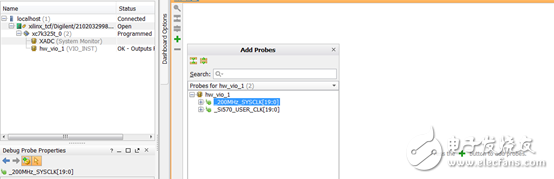

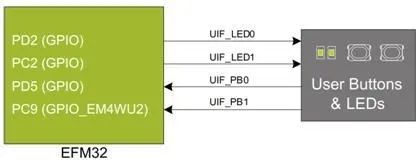

下载完成之后点击Add probes的按键,加入设置好的两个probes,分别是200MHz的clock和Si570输出时钟的频率。

初始状态下显示200MHz时钟输出频率为2000,Si570输出频率为15624。

当下载了set_311.040_mhz_si570_0.bit之后,再回到VIO显示界面时,Si570的输出频率已经更新了。

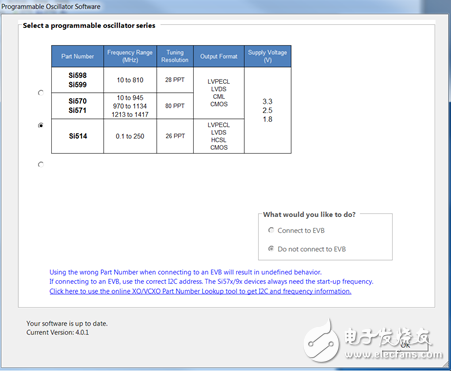

使用Programmable Oscillator Calculator计算并配置其他频率

Xilinx的工程中只提供了一些特殊频率的配置文件,如果想要将Si570的输出修改成其他频率,就需要直接对Si570的寄存器进行配置了。

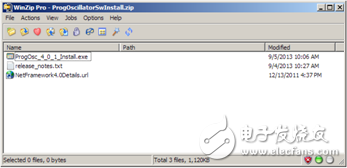

Silicon Labs提供了一个计算不同输出频率对于寄存器值的软件ProgOscillatorSwInstall.zip,下载完成后进行安装。

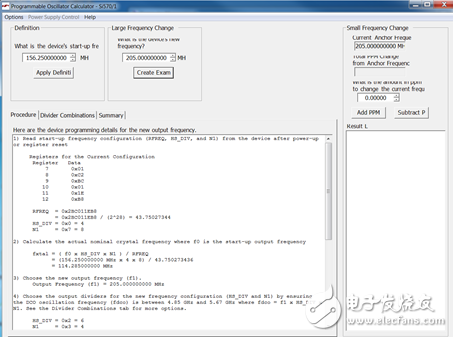

安装完成后打开软件,按照要求填写参数。设置好初始输出频率和期望输出频率,系统会自动给出相应寄存器的值。

按照计算出的寄存器值进行配置,

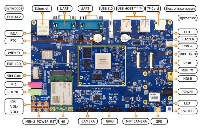

Xilinx Ultrascale Series开发板配置详细步骤

Ultrascale Series的开发板与7 Series的开发板不同,不需要再向FPGA实现烧入程序,上电后自动启动System controller。

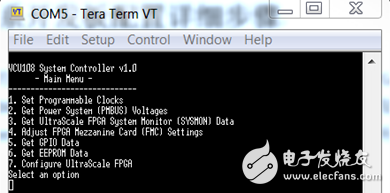

具体的操作方法是(以VCU108为例):连接好USB_UART的cable,上电后打开Tera Term,按下开发板上的复位按键,此时Tera Term就会收到System Controller传来的数据,如图 21所示。

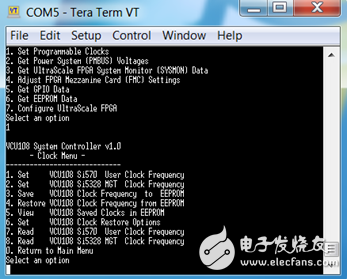

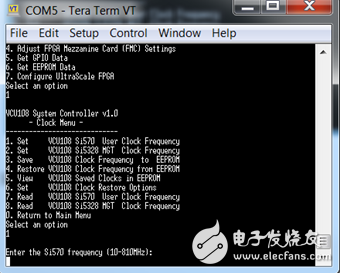

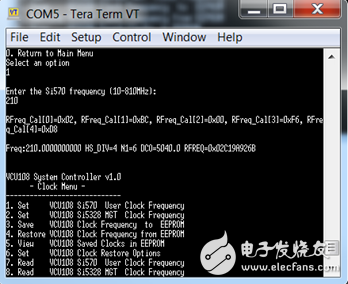

在Ultrascale的开发板上集成的这个System Controller,提供给客户一个通过UART直接进行菜单的选择,对板上可编程的配置部分进行配置的方法。例如需要修改Si570的输出频率的整个过程如下所示。

输入选择的数字后需要按回车确认。

至此就配置完成了,Ultrascale的配置相当简单,且不需要实现下载相关的bit文件。

电子发烧友App

电子发烧友App

评论