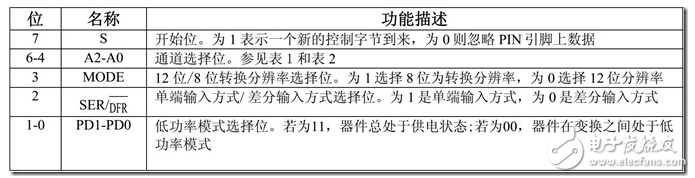

PD0和PD1:表5展示了掉电和内部参考电压配置的关系。ADC的内部参考电压可以单独关闭或者打开,但是,在转换前,需要额外的时间让内部参考电压稳定到最终稳定值;如果内部参考源处于掉电状态,还要确保有足够的唤醒时间。ADC要求是即时使用,无唤醒时间的。另外还得注意,当BUSY是高电平的时候,内部参考源禁止进入掉电模式。XPT2046的通道改变后,如果要关闭参考源,则要重新对XPT2046写入命令。

表4 控制字段每一位功能的具体说明

表5 PD位功能说明

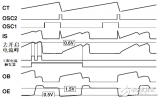

上述通过24时钟周期的转换时序讲解了单次转换的时序,在实际应用中,为了提高转换效率,XTP2046提供了16时钟转换模式和15时钟转换模式。

二)16时钟周期转换

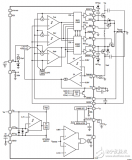

第n+1次转换的控制位可以与第n次转换部分重叠,所以可以用16个时钟周期完成一次转换,如图16所示。图16也说明了处理器和转换器之间的串行通信是可以双向独立进行的。此时,每次转换必须在开始后(接收到start)的1.6mS内完成,否则输入采样保持电路取样的信号会逐渐被放电衰减,影响转换结果。另外,在转换过程中另一串行通信的存在会使XPT2046工作于全功耗状态下。

8位总线接口,无DCLK时钟延迟16时钟周期转换时序

该模式下,DCLK的时钟高电平和低电平均要求最小值为200ns,即DCLK的时钟周期为2.5MHz。

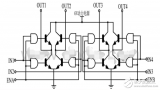

三)15时钟周期转换

下图给出了XPT2046的最快时序。这种方法不支持大部分的微控制器和数字信号处理器的串行接口,因为它们一般都不提供15周期的串行传输方式。但是,这种方法适用于FPGA和ASIC。需要注意的是,这样有效地提高了转换器的最大转换速率。

最快转换速率,15时钟周期转换

在不影响输出精度的前提下提高数据吞吐量,XPT2046可以采用8位的转换模式。切换到8位转换模式,完成提前4个时钟完成一次转换。不仅每次转换缩短了都4位(数据吞吐量提高了25%),而且由于精度的降低,可以工作在更快的转换速率下,时钟速度可以提高50%,时钟速度的提高和转换周期的减少,共同可以使转换速率提高2倍。

电子发烧友App

电子发烧友App

评论