大家都知道74hc138是一个译码器,那么什么是译码器,74hc138又有怎样的功能呢?本文将主要介绍的是关于74hc138的的原理功能解析,帮助你更深的了解74hc138元器件。

译码器

译码器简介

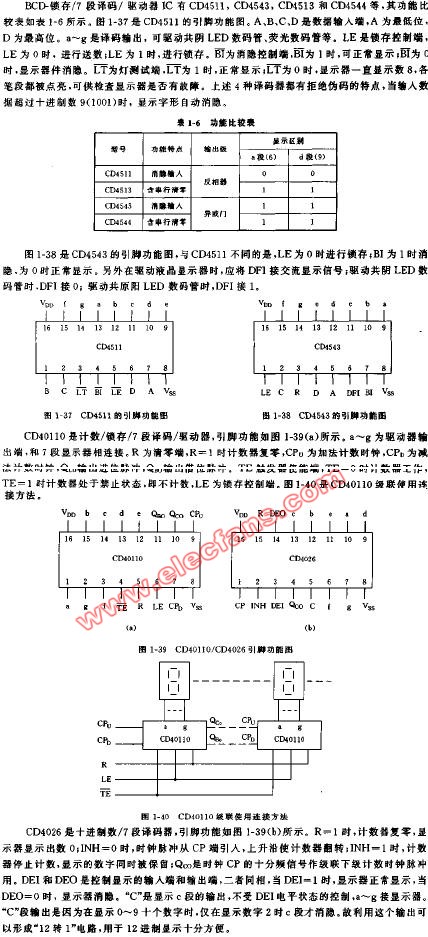

码器(decoder)是一类多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类。变量译码器一般是一种较少输入变为较多输出的器件,常见的有n线-2^n线译码和8421BCD码译码两类;显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动LED和驱动LCD两类。

译码器分类

译码器的种类很多,但它们的工作原理和分析设计方法大同小异,其中二进制译码器、二-十进制译码器和显示译码器是三种最典型,使用十分广泛的译码电路。

二进制码译码器,也称最小项译码器,N中取一译码器,最小项译码器一般是将二进制码译为十进制码;

代码转换译码器,是从一种编码转换为另一种编码;

显示译码器,一般是将一种编码译成十进制码或特定的编码,并通过显示器件将译码器的状态显示出来。

74hc138

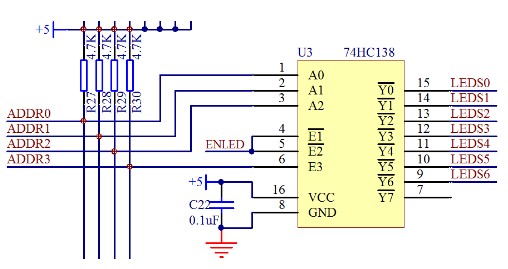

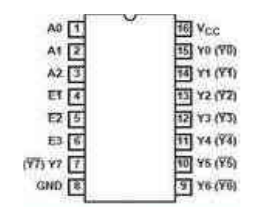

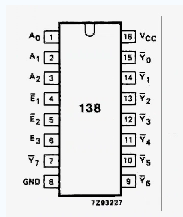

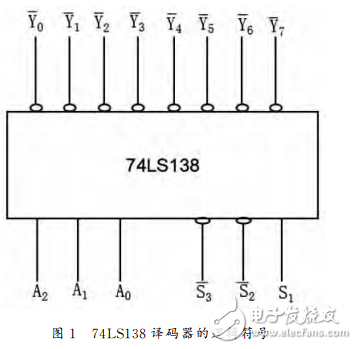

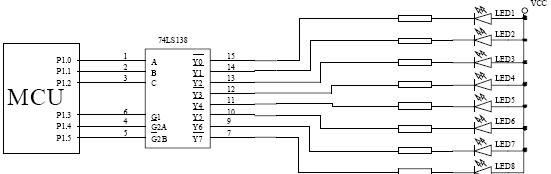

74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

74HC138是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。74HC138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在 高性能存贮器系统中,用这种译码器可以提高译码系统的效率。将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个 低电平输出。两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。在解调器应用中,赋能输入端可用作数据输入端。

74hc138的功能

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

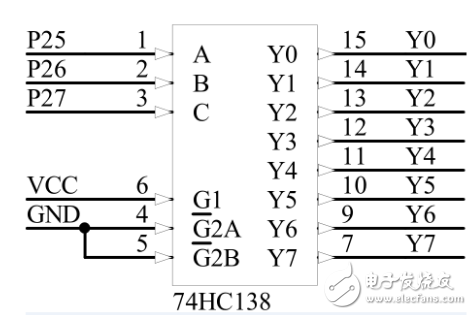

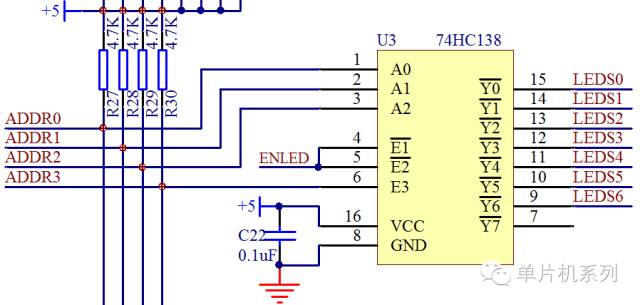

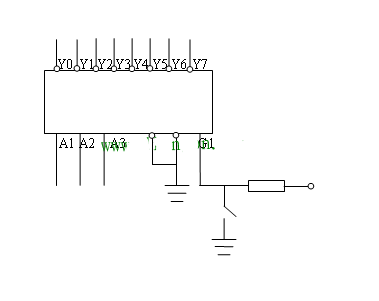

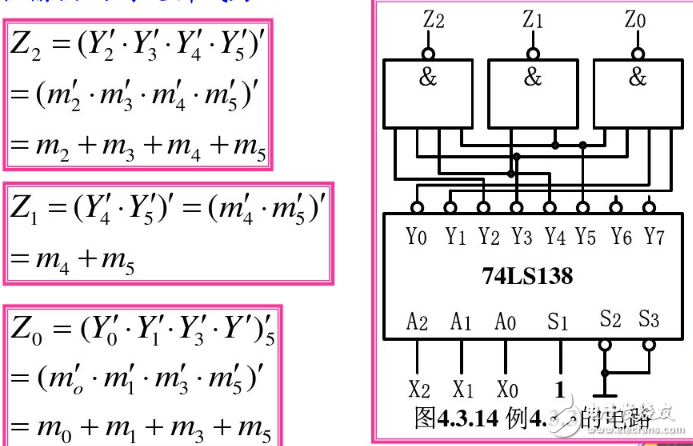

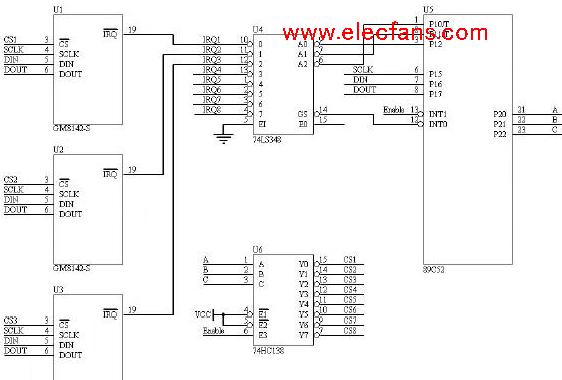

74HC138原理图

以上便是138译码器的原理图。其中,在芯片第4、5引脚处,标识符G2A和G2B上面有一横杠,这个意思是代表此端口输出低电平有效(可见,4、5引脚连接的是GND),而第6引脚连接的VCC。

74HC138译码器可接受3位二进制加权地址输入(A,B和C),并当使能时,提供8个互斥的低有效输出(Y0~Y7)。74HC138特有3个使能输入端:两个低电平有效(G2A、G2B)和一个高有效(G1)。除非G2A和G2B置低且G1置高,否则74HC138将保持所有输出为高。

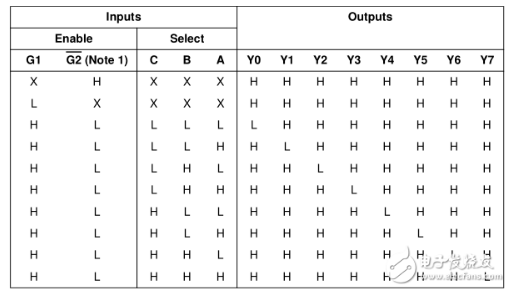

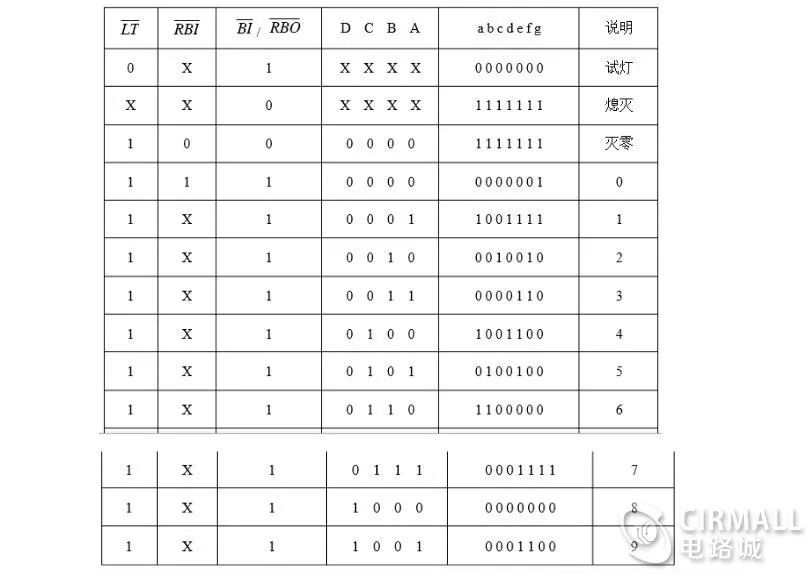

其真值表如下所示(可通过芯片手册进行查阅):

74HC138真值表

如图表下的注解所示:H—高电平,L—低电平,X—任意电平,G2(—)是代表G1A和G2B之和(其实看原理图便知,G2A和G2B是一起控制的)。

通过真值表,我们知道正确的控制方式为,G1给高电平,G2给低电平。于是,通过控制ABC三者输入的值(二进制),控制Y0-Y7的输出值(二进制)。

例如,ABC = 000,Y0-Y7 = 0111 1111 ; ABC = 101,Y0~Y7 = 1111 1011。

有一点请注意:

前面说到,138译码器是提供8个互斥(Y0-Y7,8个脚互不影响)的低电平输出,但是输出来除了被ABC地址选中的那一个,其他的都是1,这是因为芯片内部的每个输出端口前,都接有一个与非门,于是输出端电平反相了。

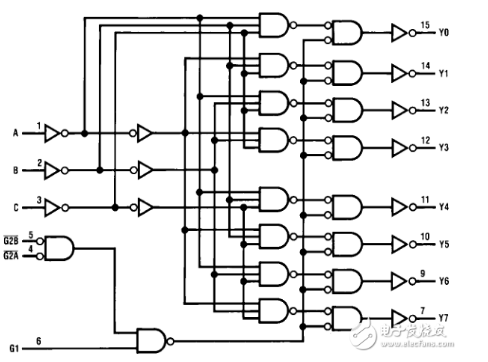

下面附上74HC138译码器的逻辑图:

在每一个输出端口前面,可以看到都存在一个与非门电路(简单的数电知识),我们可以在逻辑图中对ABC赋值,再去查看Y0~Y7的输出,再与真值表核对一下。

到此为止,可能已经能看出来,138译码器的功能之一了:如原理图所示,使得P2.5P2.6P2.7三个引脚,控制了8个输出!但是大家会问到,每次输出都会是7个高电平,1个低电平。

74HC138的应用

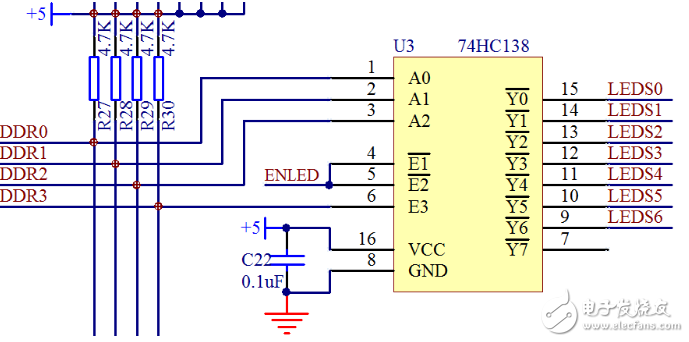

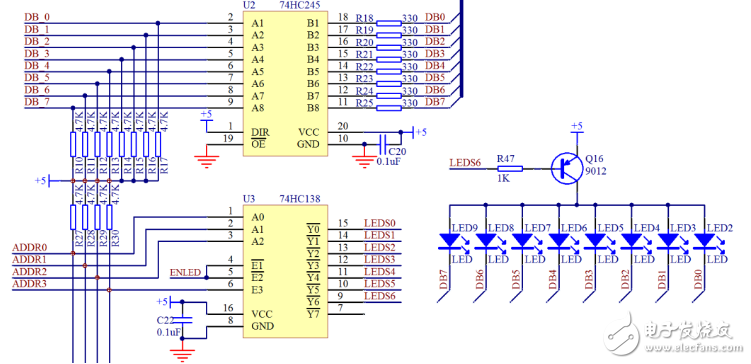

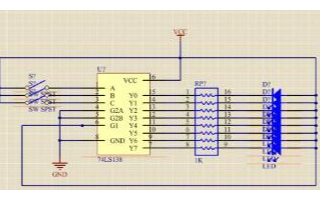

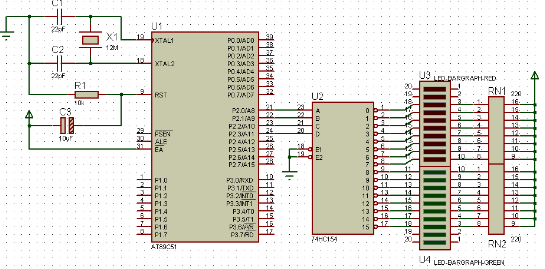

一般在单片机电路中,为了掌握更多的器件,就要运用一些核心的数字芯片,这种数字芯片由复杂的输出逻辑来掌握输入逻辑,比方 74HC138这个三八译码器,图 3-15 是 74HC138 在我们道理图上的一个使用。

74HC138应用原理图

从这个名字来剖析,三八译码器,就是把 3 种输出形态翻译成 8 种输入形态。从图 3-15所能看出来的,74HC138 有 1~6 一共是 6 个输出引脚,然则个中 4、5、6 这三个引脚是使能引脚。使能引脚和我们前边讲 74HC245 的 OE 引脚是一样的,这三个引脚假如不契合规则的输出请求,Y0 到 Y7 不论你输出的 1、2、3 引脚是什么电平形态,老是高电平。所以我们要想让这个 74HC138 正常任务,ENLED 谁人输出地位必需输出低电平,ADDR3 地位必需输出高电平,这两个地位多是使能掌握端口。不晓得人人能否记得我们第二课的程序有这么两句 ENLED = 0;ADDR3 = 1;就是掌握使这个 74HC138 使能的。

这类逻辑芯片,大多多是有使能引脚的,使能契合请求了,那下面就要研讨掌握逻辑了。关于数字器件的引脚,假如一个引脚输出的时分,有 0 和 1 两种形态;关于两个引脚输出的时分,就会有 00、01、10、11 这四种形态了,那么关于 3 个输出的时分,就会呈现 8 种形态了,人人可以看下边的这个真值表——图 3-16,个中输出是 A2、A1、A0 的次序,输入是从Y0、Y1.。..。.Y7 的次序。

74HC138在任一输出形态下,只要一个输入引脚是低电平,其他的引脚多是高电平。在后面的电路中我们曾经看到,8 个 LED 小灯的总开关三极管 Q16 基极的掌握端是LEDS6,也就是 Y6 输入一个低电平的时分,可以守旧三极管 Q16,从右侧的愿望输入的后果,我们可以推导出我们的 A2、A1、A0 的输出形态应当是 110,如下图:

那么我们再全体捋一遍点亮 LED 小灯的进程,起首看 74HC138,我们要让 LEDS6 为低电平才干导通三极管 Q16,所以 ENLED = 0;ADDR3 = 1;包管 74HC138 使能。然后 ADDR2 =1; ADDR1 = 1; ADDR0 = 0;如许包管了三极管 Q16 这个开关守旧,5V 电源加到 LED 上。

而 74HC245 左侧是经过 P0 口掌握,我们让 P0.0 引脚等于 0,就是 DB_0 等于 0,而右侧 DB0 等于 DB_0 的形态,也是 0,那么如许在这一排共 8 个 LED 小灯傍边,只要最右侧的小灯和 5V 之间有压差,有压差就会有电流畅过,有电流畅过我们的 LED2 就会发光了。

结语

关于74HC138的介绍就到这了,在本文中我们共同探讨的译码器以及74HC138的介绍、原理功能分析,希望通过本文能让你对74HC138有更好的认知,如有不足之处欢迎指正。

电子发烧友App

电子发烧友App

评论