加法器是如何实现的

verilog实现加法器,从底层的门级电路级到行为级,本文对其做出了相应的阐述。

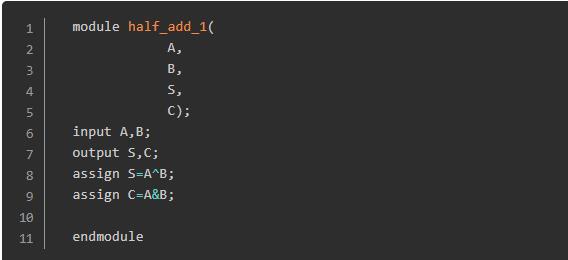

1、一位半加器

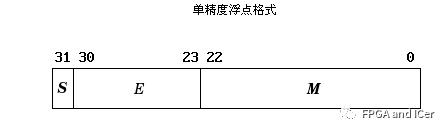

所谓半加器就是有两个输入,两个输出,不考虑进位。其真值表如下:

由此,我们可以得到S=A^B,C=A&B。用相应的与门、异或门来实现半加器。

对应的Verilog代码如下:

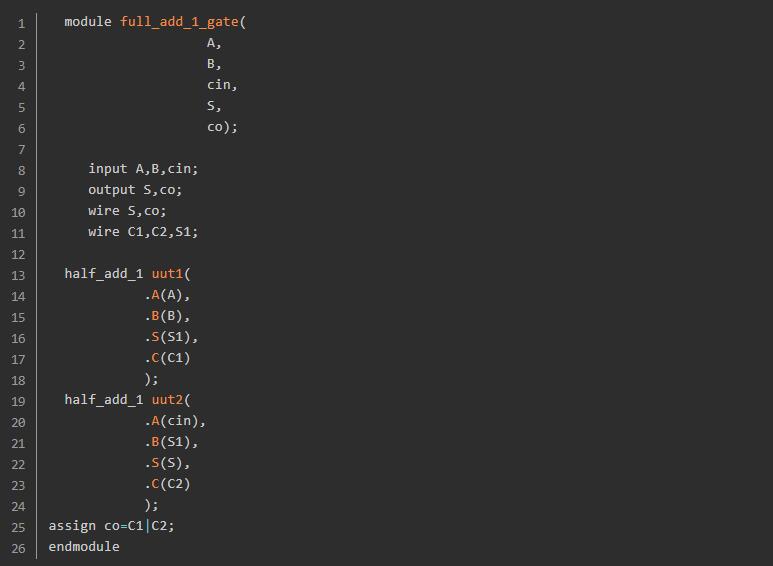

2、一位全加器

全加器包含三个输入,两个输出,其中包含一个进位。

2.1 实现方式一

与半加器类似画出其真值表,进一步通过画卡诺图得到相应的函数表达式。

S=A^ B^cin,co=(A&B)|(A&cin)|(B&cin)。

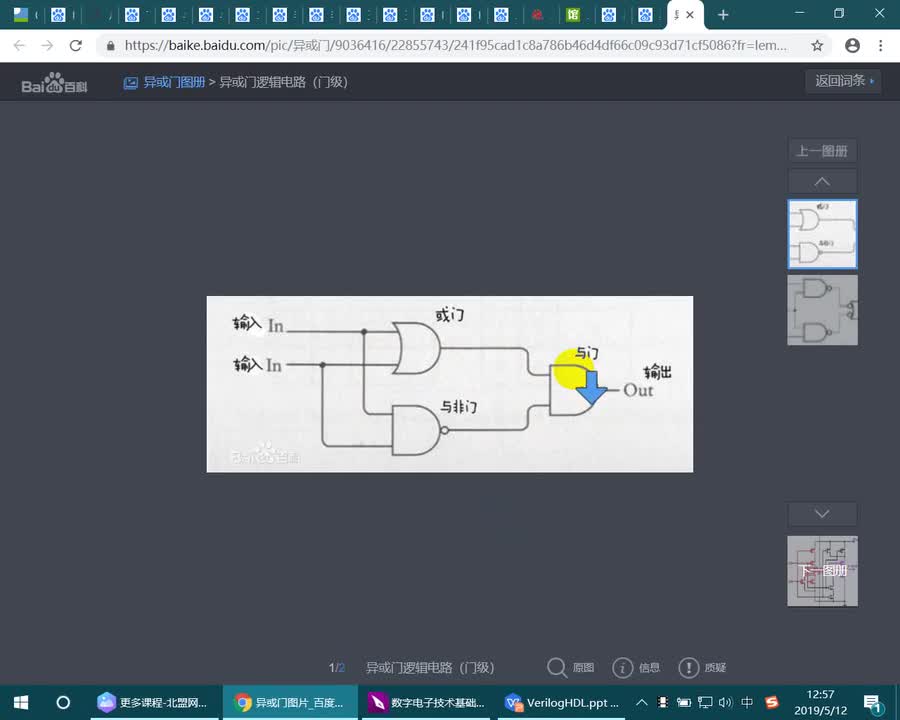

2.2 实现方式二

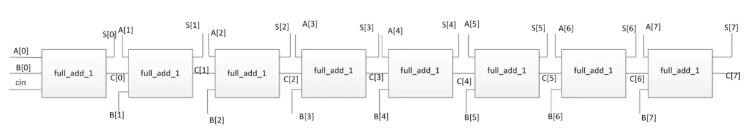

利用两个半加器和一个或门实现全加器。其电路结构图如下:

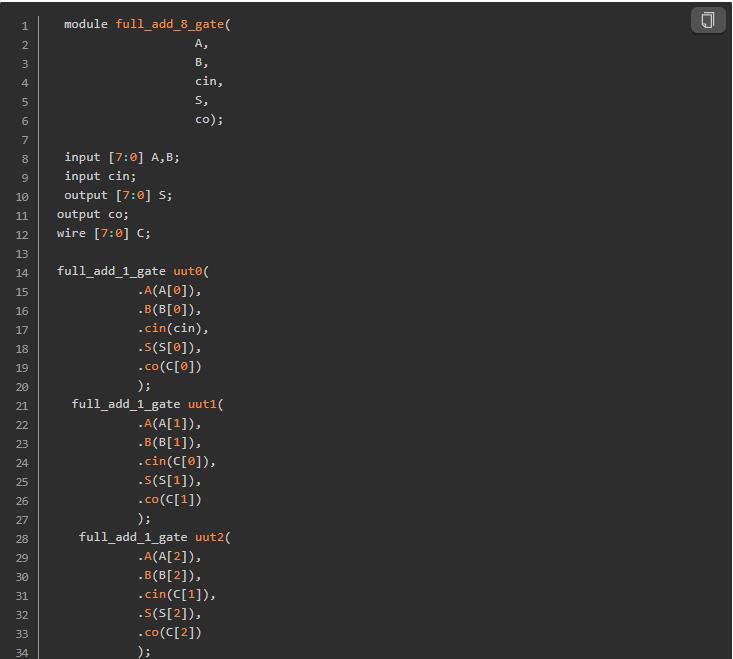

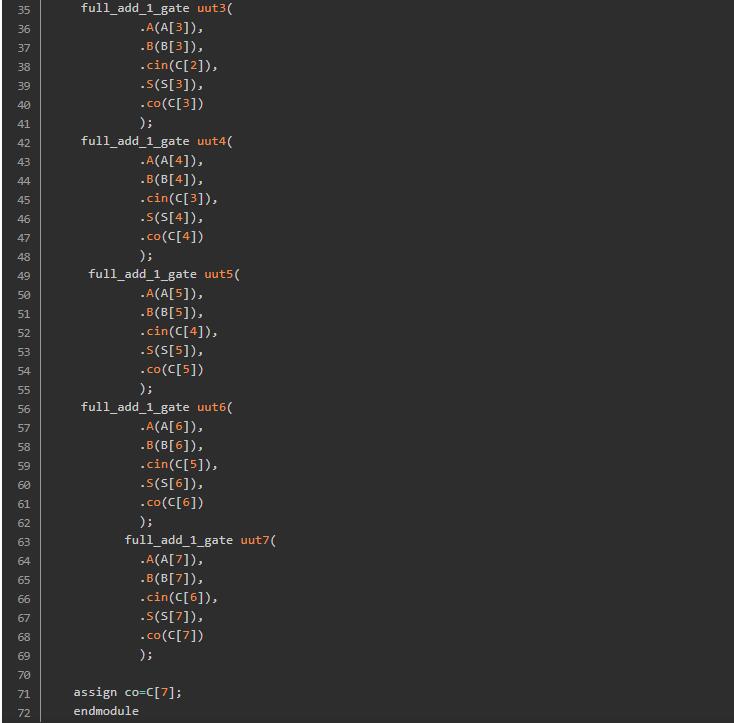

3、多位加法器的实现

在数字信号处理的快速运算电路中常常用到多位数字量的加法运算,对于多位宽加法器的处理,我们以逐位进位加法器为例。

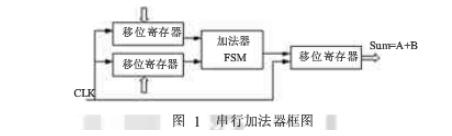

代码和电路结构框图如下:

串行加法器限制了运行的速度,在实际应用中,我们一般用到并行加法器。大致可以分为以下几类:进位旁路加法器、线性进位选择加法器、平方根进位选择加法器、超前进位加法器、对数超前进位加法器。并行加法器比串行加法器快得多,电路结构也不太复杂,它的原理很容易理解。

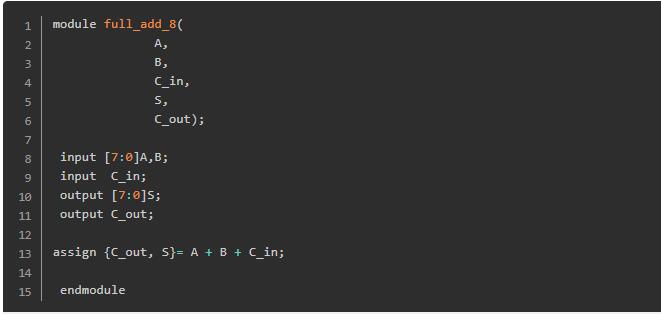

4、行为级描述加法器

用Verilog HDL来描述加法器是相当容易的,只需要将运算表达式写出就可以了。

一位全加器

八位加法器

这样设计的加法器在行为仿真时是没有延时的。借助综合器,可以根据以上Verilog HDL源代码将其自动综合成典型的加法器电路结构。综合器有许多选项可供设计者选择,以控制自动生成电路的性能。设计者可以考虑提高电路的速度,也可以考虑节省电路元件以减少电路占用硅片的面积。在FPGA的库中或某工艺的ASIC库中,都有参数化的加法器供设计者选用。

加法器的设计优化

逻辑改造后,电路也应该相应地进行优化设计,因为如果用普通的门电路来实现式(12)~(15)的逻辑,晶体管数目(面积)会增加。另外,在电路级也可以采用减少节点翻转和寄生电容的方法来降低功耗。

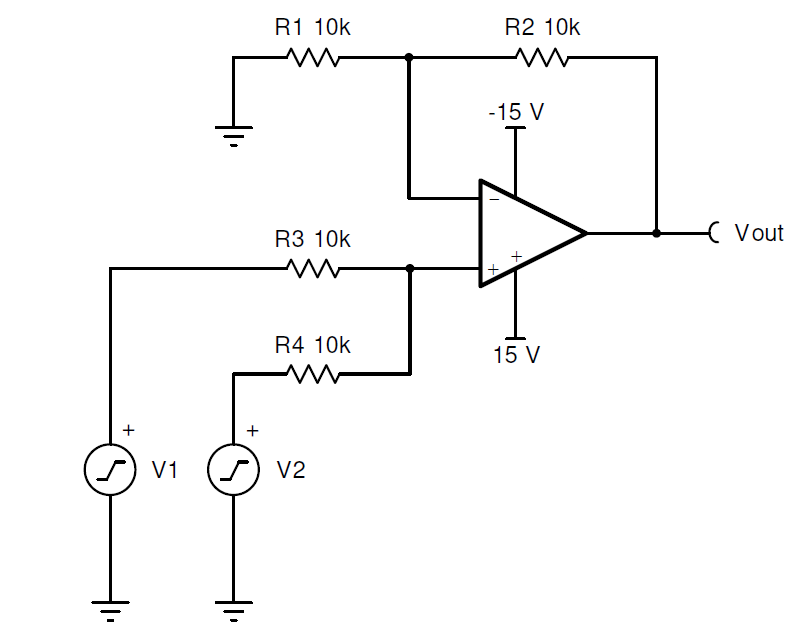

式(12)~(15)中多处要用到同或门,设计中,我们用基于旁路的静态逻辑[4]实现产生gs的同或门,如图2。旁路逻辑通过由附加管形成的旁路,可以把“串并交错”的电路结构简化为单一的串或者并的形式。它的电路和版图都有很好的规整性,并且可以减小寄生电容。是两种同或门N块版图不同部分的比较,(b)是基于旁路逻辑实现的,与(a)相比,少了一条金属连线和两个金属接触,使版图变得十分规整,扩散区不会被隔断。在拓扑上,两条分支用公共的漏区,达到最少的接触孔和金属互连,比“串并”和“并串”的晶体管配置方式规整,且寄生电容小。

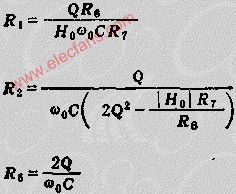

加法器电路上的延迟值

旁路逻辑不能实现传输门,因而不能用传输门实现同或和异或,但是容易证明,三态门在速度和功耗方面都比传输门优越。参照传输门的结合方式,我们用两个三态反相器和一个反相器实现了同或门。

实现了式(13)括号内的两个同或逻辑,平均只需要1级门延时,而用普通门实现的“与非或与非”形式的同或门需要2级或3级门延时。由上面的同或门设计得到启发,根据形如式(13)的逻辑,设计了一个10管单元utiandor2。

该单元电路实现s=c0CK+0CKN,只要把式(12)~(15)中的括号部分从CK和CKN输入,输出就相应得到了s0~ s3 。仅当CKN=时,电路(a)两边均是三态反相器,构成图5(b)的同或门,两个反相器交替导通,s=c0⊙CK ;当CKN=CK(发生几率比较大),左边P管和右边N管,或者左边N管和右边P管交替导通,输出s=CK,从而屏蔽了c0的变化。考察第一组4位CLA中的进位产生逻辑最复杂的s3,参考式(15),当g2,g1,g0均为0,p2,p1,p0均为1时,s3= gs3⊙c0,显然这是一种特殊情况,即低位各位都不产生进位,但可以传递进位时,直接把c0传至高位与gs同或即可产生和。c0在各位和生成逻辑的最后一级才加入,可以消除过早加入带来的不必要的翻转。左右两块交替导通,只存在下拉或上拉延时,有类似动态电路延迟小的优点。仅用了10个晶体管,比常规门实现的积之和节省8个。

责任编辑:YYX

电子发烧友App

电子发烧友App

评论