对于FPGA开发而言,仿真是开发流程中必不可少的一步,也是非常重要的一步,仿真是将RTL代码模拟运行,得到module中信号波形,再进行功能分析的过程。强大的功能与速度兼具的modelsim仿真就是

2020-09-30 13:52:33 8685

8685

仿真功能概述 仿真FPGA开发中常用的功能,通过给设计注入激励和观察输出结果,验证设计的功能性。Vivado设计套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 4722

4722

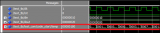

我们在Windows系统下使用Vivado的默认设置调用第三方仿真器比如ModelSim进行仿真时,一开始仿真软件都会默认在波形界面中加载testbench顶层的信号波形

2023-09-13 09:23:49 712

712

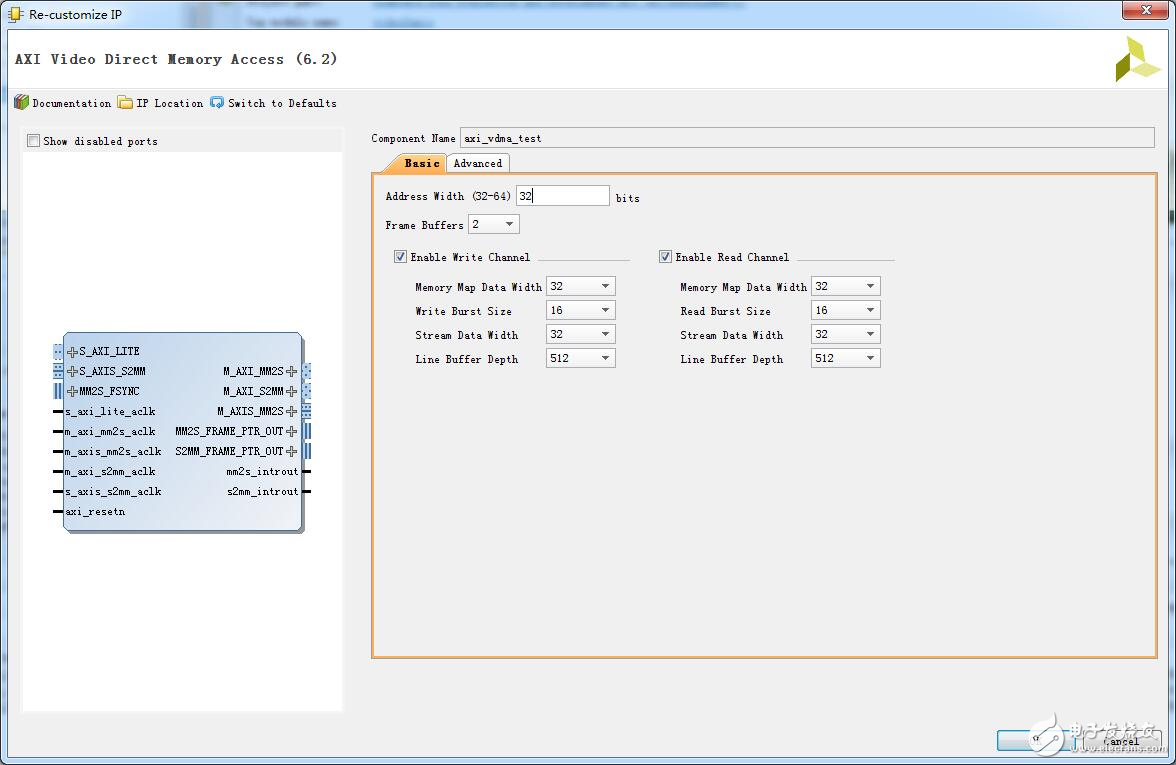

直接在modelsim软件内执行.do文件进行仿真,不通过vivado调用modelsim,vivado仅用于生成IP核。

2023-12-04 18:26:34 477

477

ModelSim是工业界最优秀的语言仿真器,它提供最友好的调试环境,是作FPGA、ASIC设计的RTL级和门级电路仿真的首选。它支持PC和UNIX、LINUX平台,是单一内核支持VHDL和Verilog混合仿真的仿真器

2011-11-11 09:53:59 8136

8136

大家好!我在使用Modelsim进行仿真时,从 ISE 启动 Modelsim 仿真是完全正常的,但从 Modelsim 直接建立工程,进行仿真,总是提示“Module 'IBUFG

2015-01-26 23:17:51

各位,小弟最近遇到一个很奇怪的问题。我在使用modelsim进行仿真时,无论是通过quartus调用还是直接运行modelsim,都会遇到提示:“error loading design“,从而仿真

2015-08-30 22:14:39

本压缩包包含了许多modelsim例程代码,有助于modelsim仿真学习。点击下载

2019-04-26 17:21:10

modelsim 仿真

2013-09-09 19:27:29

我在用quartus调用modelsim仿真波形时出现波形窗口,但没有信号名也没有波形,求高手给指点下

2013-08-27 11:12:03

请问一下在ISE14.6中编译完modelsim10.0a,在用modelsim进行仿真时会闪退是怎么回事,有什么解决办法?期待热心的你给以指教!

2016-05-19 21:10:18

用modelsim仿真时出来Modelsim is exiting with code 7然后就关闭了是怎么回事

2020-04-13 04:23:07

为什么简单的分频器程序调用modelsim仿真不了,同样的方法仿真与门程序就没有问题啊?下面是自己写的源程序和测试程序。module ff (clk,q);input clk;output q

2013-10-08 20:28:56

在使用quartusii modelsim仿真时。。功能仿真可以好用,。但是时序仿真就出错。。无论是手动打开modelsim,还是直接调用。。时序仿真就是出错。。没有输出。。但是用quartus自带的vwf那个仿真时。。功能和时序仿真就都好用。。到底什么原因呢。。{:4:}。。谁能给指点一下

2013-11-26 21:06:56

我使用的是vivado软件和modelsim联合仿真,但是每次vivado中的测试文件修改之后,我都是关闭modelsim再点击vivado中的simulation重启modelsim,这样很

2017-12-15 20:53:06

vivado中如何对edif封装后的文件进行modelsim下的时序仿真,求教

2017-09-03 14:52:44

Altera和Xilinx Modelsim仿真库Altera和Xilinx Modelsim仿真库 我们通常使用modelsim软件作为仿真工具,不同阶段的仿真使用不同的库文件,在开始仿真前将库

2012-08-10 18:31:02

quartus和modelsim联合仿真容易出现问题,所以一般单独用modelsim仿真,附件是modelsim仿真的步骤

2017-02-17 20:21:18

FPGA基础篇(三):modelsim仿真的几个常见问题对于FPGA开发的流程无外乎就三步,第一编写程序,第二仿真,第三仿真结束之后下载到板子。其中仿真是必须经历的过程,对于altera的芯片来说

2017-04-15 21:46:29

用ISE和modelsim联合仿真,每次在ISE修改程序后必须把原来打开的modelsim关闭了再重新打开吗?

2017-02-21 20:40:27

刚开始用modelsim,在ise和modelsim的联合仿真中,一般都是从ise中启动modelsim的,但是如果仿真文件有错,或者要修改仿真文件,难道都要先关掉modelsim,然后再在ise中打开modelsim,不能不关闭modelsim直接进行修改仿真文件,然后直接进行仿真吗

2015-11-12 10:11:44

最近,做 rom 的modelsim 仿真时,遇到了一些问题 (error 主要是rom初始化文件 .hex的 问题),在网上 找了一些资料,现在记录下 解决思路和 解决办法:rom初始化文件可以用

2014-03-06 16:22:21

我现在将vivado和modelsim做了联合仿真,用来仿真蜂鸟e203协处理器扩展实现的功能。现在的问题是:使用vivado的仿真器仿真时vivado的TCL console可以打印输出C程序中

2023-08-11 06:44:51

:/modeltech64_10.4”下的modelsim.ini文件夹的属性,具体的操作参照ISE和modelsim的联合仿真库编译步骤。2、 vivado里面每次修改完程序之后无需关闭modelsim,直接

2018-10-16 19:43:20

想要仿真quartus下工程中的一个IP核,但是不知道怎么样才能把这个IP核弄到modelsim下进行仿真,求指教!!!!!

2014-04-04 00:36:25

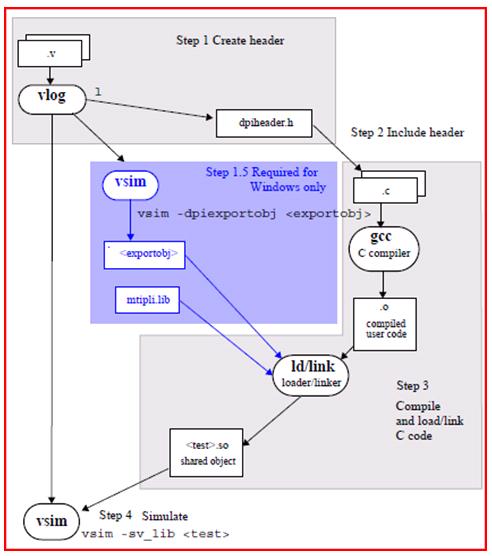

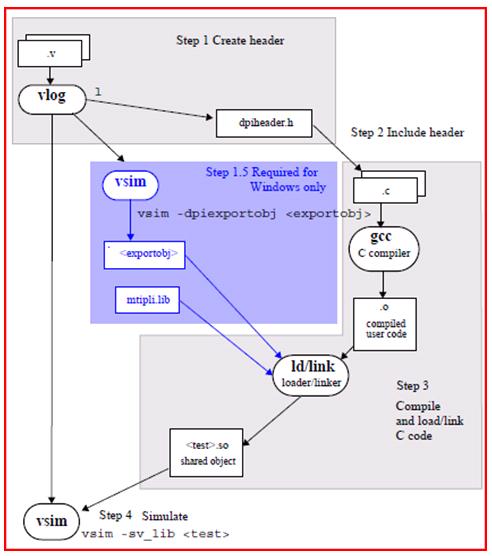

1前言协同仿真就是利用仿真工具提供的外部接口,用其它程序设计语言(非HDL语言,如c语言等)编程,用辅助仿真工具进行仿真。Modelsim提供了与c语言的协同仿真接口。以Windows平台为例,用户

2019-06-06 05:00:38

如何使用modelsim仿真?是不是一定要有testbench .v 文件?

2014-03-29 09:56:53

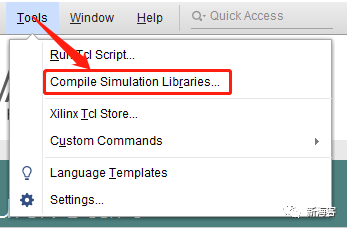

嗨,我需要在vivado工具中为Modelsim编译模拟库。我需要知道完整的程序。我应该在编译模拟库wiondow中为“Compiled Library Block”和“Simulator Executable Path”块选择什么路径。谢谢,Nishant Angadi

2020-05-05 12:09:24

原来仿真使用的是vivado simulator,最近将vivado的仿真器改成modelsim,发现仿真的时候modelsim的transcript没法打印出e203实时运行的信息。请问要在modelsim中设置什么地方吗

2023-08-11 09:47:12

嗨, 我想知道是否有像ISE一样的vivado中的任何测试平台。在ISE中点击添加源我们得到vhd testbech module.but在vivado我们将如何创建测试平台

2020-03-19 09:43:58

本文在开环时序仿真的基础上提出一种基于QuartusII、DSP Builder和Modelsim的闭环时序仿真测试方法,并借助于某一特定智能控制器的设计对该闭环测试方法进行了较为深入的研究。

2021-05-06 09:36:44

。ISE可以添加多个不同的testbench文件,也可以自动识别和被测试源文件的层次关系,如图1所示。图1 ISE中testbench文件管理Vivado中对于testbench的管理,增加了一个

2016-01-13 12:04:16

安路平台如何在Modelsim上做仿真?

2023-08-11 09:02:37

1 前言协同仿真就是利用仿真工具提供的外部接口,用其它程序设计语言(非HDL语言,如c语言等)编程,用辅助仿真工具进行仿真。MODELsim 提供了与c语言的协同仿真接口。以Windows平台为例

2019-05-15 07:00:10

在Modelsim SE中如何指定altera仿真库

2008-09-09 17:50:04 44

44 本文主要描述了如何在 QUARTUS II 中输入程序文件,生成网表及标准延时文件,然后通过MODELSIM 进行功能仿真与后仿真的过程,主要为图解,含全部代码及仿真波形。

2009-07-22 15:44:53 0

0 我把我用到的软件说明一下。如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

2009-07-22 15:46:27 0

0 我想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。一些步骤被作者有意无意地省略掉,这常常给读

2010-03-31 09:46:36 112

112 当我们使用QuartusII,但是大多数朋友都习惯用Modelsim SE来做仿真,由于Quaruts有很多本身器件的特色,所以造成了在仿真上的麻烦,当然网路上也有一些讲解,但是都是不太系统,特

2010-06-24 17:57:18 216

216 ModelSim和QuestaSim功能简介及应用

ModelSim是工业界最优秀的语言仿真器,它提供最友好的调试环境

2010-04-29 09:07:27 19277

19277

1 前言 协同仿真就是利用仿真工具提供的外部接口,用其它程序设计语言(非HDL语言,如c语言等)编程,用辅助仿真工具进行仿真。Modelsim提供了与c语言的协同

2010-06-07 08:33:59 1124

1124

ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程序进行仿真,支持IEEE常见的各种硬件描述语言标准。可以进行两种语言的混合仿真,但推荐大家只对一种语言

2011-04-19 20:52:46 151

151 第一章 1、 关于 Modelsim中库的编译 2、 如何在modelsim中指定Altera的仿真库 3、 Modelsim波形文件 4、 后仿真时,是不是要对复位信号GSR/GTR做特别特殊处理?为什么? 5、 功能仿真加STA能不

2011-05-26 15:48:05 0

0 ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程序进行仿真,支持IEEE常见的各种硬件描述语言标准。可以进行两种语言的混合仿真,但推荐大家只对一种语言

2011-05-27 16:41:59 132

132 Altera ModelSim 6.5仿真入门教程,需要的可自行下载。 平台 软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容 1 设计流程 使用ModelSim仿真的基本流程为: 图1.1 使用 ModelSim仿真的基本

2012-08-15 15:40:24 255

255 用ModelSim 进行功能仿真,进行功能仿真首先要检查设计的语法是否正确;其次检查代码是否达到设计的功能要求。下文主要介绍仿真步骤和测试激励的加载。

2012-11-13 15:35:59 8536

8536 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 本章为ModelSim的初级教程,读者读完本章可以较为熟练的使用ModelSim进行设计仿真,本章没有也不可能涉及ModelSim的各个方面,要想全面的掌握ModelSim可以参阅软件文档。

2015-12-24 18:29:37 0

0 在我们用ModelSim仿真的时候经常是修改一点一点修改代码,这样会造成一个无奈的操作循环:修改代码--->编译代码--->仿真设置--->进入仿真页面--->添加需要观察的波形--->运行仿真

2017-02-11 15:25:07 10138

10138

在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软件 VCS软件最好安装

2018-07-05 03:30:00 10732

10732

本文列出了能够与 Vivado 设计套件联用的支持性第三方仿真器。 这些也在随该软件一起发布的“Vivado 设计套件用户指南:版本说明、安装与许可”(UG973) 中列出。 请参阅“架构支持与需求

2017-11-15 16:18:36 1893

1893 Modelsim是Mentor公司开发的专业仿真软件,支持VHDL、VerilogHDL和混合仿真的全系列流程。作为目前最流行的仿真工具之一,Modelsim提供了图形界面和命令行两种工作模式

2017-11-24 11:54:06 24957

24957

modelsim仿真详细过程(功能仿真与时序仿真).ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。 ModelSim的使用中,最基本的步骤包括创建工程、编写源代码、编译、启动仿真器和运行仿真五个步骤。

2017-12-19 11:14:11 63885

63885

如何通过ModelSim-Altera生成测试台,并通过NativeLink运行RTL仿真

2018-06-22 09:00:00 4278

4278 本文通过一个简单的例子,介绍Vivado 下的仿真过程。主要参考了miz702的教程,同时也参考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 37132

37132 了解如何使用Vivado中的Synopsys VCS仿真器使用MicrBlaze IPI设计运行仿真。

我们将演示如何编译仿真库,为IP或整个项目生成仿真脚本,然后运行仿真。

2018-11-29 06:57:00 6822

6822 ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。 ModelSim的使用中,最基本的步骤包括创建工程、编写源代码、编译、启动仿真器和运行仿真五个步骤,仿真流程如图1所示:

2018-12-29 11:35:14 9227

9227 本次使用的Vivado版本为Vivado_2017.3版本,从Xilinx官方文档可以了解到,该版本的Vivado只支持Modelsim10.6或者更高版本,但是笔者只有Modelsim

2019-03-30 09:51:46 16946

16946

本文档的主要内容详细介绍的是modelsim仿真使用教程资料免费下载。

2019-04-02 08:00:00 6

6 笔者一直以来都在纠结,自己是否要为仿真编辑相关的教程呢?一般而言,Modelsim等价仿真已经成为大众的常识,但是学习仿真是否学习Modelsim,笔者则是一直保持保留的态度。笔者认为,仿真

2019-04-30 18:24:00 23

23 的时候是定位到win64文件夹,而不是应用程序 4.然后设置setting 这里值得注意的是我们选的仿真器是modelsim而不是modelsim

2020-03-16 16:13:03 889

889

之前玩过Altera的板子,不不, 现在应该叫intel PSG。在QuartusII13.0上老喜欢用modelsim_ae做仿真,小工程用起来也方便,但是我做IIC配置摄像头的时序仿真时,就显得有些吃力,所以还是用modelsim_se才是正点。

2020-04-10 08:00:00 1

1 本文档的主要内容详细介绍的是FPGA仿真的学习课件和工程文件免费下载包括了:1、testbench编写,2、仿真工具使用,2、仿真工具使用,4、Vivado与Modelsim联合仿真。

2020-12-10 15:28:18 30

30 本文介绍如何在教程(三)基础上, 关联ELF输出文件并使用vivado对系统进行行为仿真。

2021-03-01 10:25:43 24

24 本公众号专辑《芯片设计课程及相关实验》。本文是孙义雯同学采用Python语言实现的Vivado和Modelsim联合仿真的自动化脚本,已经在实际项目中经过较长时间的检验,今天开源出来,供大家学习,欢迎留言交流心得体会和改进建议。同时,后续我们会

2021-05-03 10:06:00 1709

1709

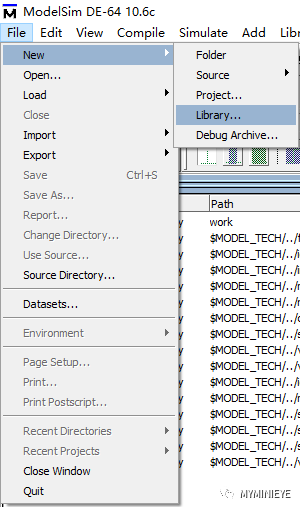

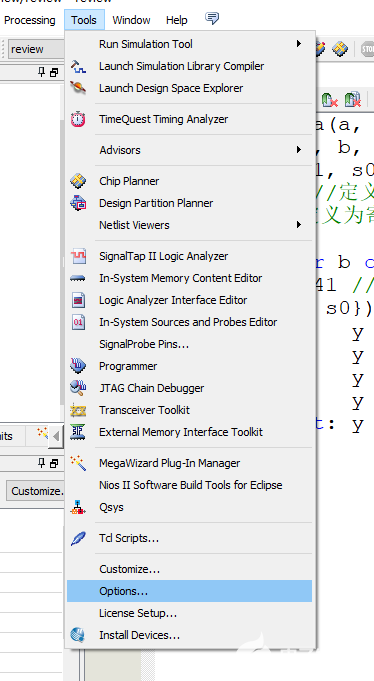

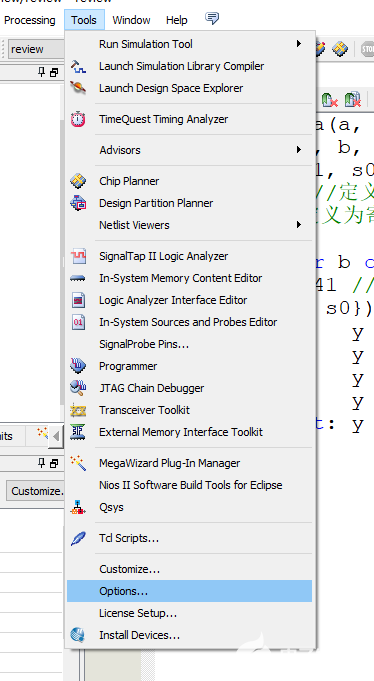

在vivado中设置modelsim(即第三方仿真工具)的安装路径。在vivado菜单中选择“Tools”——》“Options.。。”,选择“General”选项卡,将滚动条拉倒最底部

2021-04-15 10:10:49 4693

4693

总体思想是现在 MATLAB 中产生仿真所需要的输入信号,以十六进制形式存放在数据文件中,在modelsim 中用 vhdl 语言编写测试文件,做时序仿真,最后将结果存入另外一个数据文件,最后在 matlab中将 modelsim 的仿真输出文件读入一个数组中,以便可以作图分心,进一步做误差分析。

2021-06-01 10:31:20 33

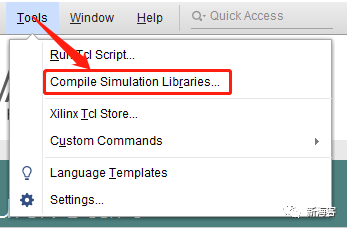

33 1.modelsim编译vivado库 1)双击启动vivado软件,如下图操作。 2)Simulator:选对应的, Language:都选all, Verilog与vhdl都用可能

2021-06-01 11:33:56 2357

2357

3 ModelSim工程实战之自动仿真说完了 ModelSim 的使用流程,接下来我们将会对每个流程进行详细的操作演示,一步步、手把手带领大家学习使用 ModelSim 软件。首先我们讲解

2021-07-23 10:51:17 1710

1710

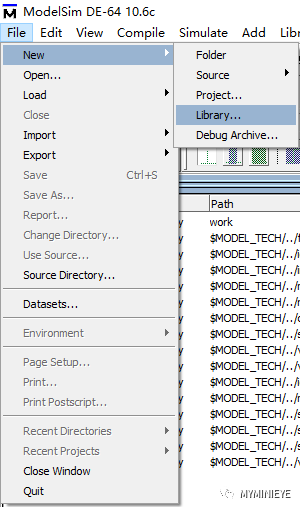

4.1 新建仿真工程 在开始动手仿真之前,首先,我们需要创建一个文件夹用来放置我们的 ModelSim 仿真工程文件,这里我们就在之前创建的 Quartus 工程目录下的 simulation

2021-07-23 11:10:48 3514

3514 时序仿真与功能仿真的步骤大体相同,只不过中间需要添加仿真库、网表(.vo)文件和延时(.sdo)文件。到了这里,问题来了,仿真库、网表(.vo)文件和延时(.sdo)文件怎么获得呢?网表(.vo

2021-07-23 11:55:41 1915

1915 Modelsim使用技巧—波形白底黑线设置 在发表期刊或者论文时,我们需要夹带modelsim的仿真波形在我们的论文里,在modelsim默认模式下的波形一般是黑底绿线白字,如图1所示。打印出来几乎

2021-08-26 11:23:12 3451

3451 Vivado调用Questa Sim或ModelSim仿真中存在的一些自动化问题的解决方案。 Vivado调用Questa Sim仿真中存在的一些问题 首先说明一下Modelsim与Questa

2021-09-02 10:12:06 7274

7274

Vivado自带的仿真,个人觉得跑一些小模块的仿真还是可以的,不过跑大的仿真系统,容易无体验感,建议用第三方工具,这边就直接对ModelSim下手了,接下来介绍下这两者联合仿真的操作。

2022-03-11 11:32:11 6150

6150 在该页面中,如果你安装的是 ModelSim 软件,那么你需要在 ModelSim 路径中进行设置,这里我们使用的 ModelSim-Altera , 所 以 我 们 将 ModelSim-Altera 路 径 设 置 成 了C:altera13.1modelsim_asewin32aloem。

2022-05-17 10:09:42 1898

1898 在开始动手仿真之前,首先,我们需要创建一个文件夹用来放置我们的 ModelSim 仿真工程文件,这里我们就在之前创建的 Quartus 工程目录下的 simulation 文件夹中创建

2022-07-11 10:58:09 4454

4454 本文主要介绍使用 Vivado 仿真器进行混合语言仿真的一些要点。

2022-08-01 09:25:56 1008

1008 在 Windows 下,我喜欢在批处理模式下运行 Vivado 仿真器。 我创建了仿真批文件 (.bat) ,包含以下命令。当我运行批文件,执行第一条命令后脚本中止。如何正确在批模式下运行 Vivado 仿真器?

2022-08-01 09:43:01 728

728 Modelsim仿真将设计以树状表示,设计中的每一个实体,每一个module、每一个进程(always块、initial块等)在Modelsim仿真中以对象的形式展现。

2022-08-12 15:04:36 2136

2136 整体步骤基本一样,只是do文件分成了两个文件。使用工具Vivado2017.2 && Modelsim 10.5。

2023-02-06 14:22:51 2668

2668 首先说明一下Modelsim与Questa Sim都可以与Vivado联调,也比较相似,但是Questa Sim比Modelsim功能更加广泛,对于System Verilog的语法支持更加完善

2023-02-10 16:28:22 2434

2434 联调仿真分析,操作简单。你几乎不需要手动敲Tcl指令就可以进行仿真,自动化程度更高。

2023-03-14 10:55:43 5933

5933 首先说明一下Modelsim与Questa Sim都可以与Vivado联调,也比较相似,但是Questa Sim比Modelsim功能更加广泛

2023-05-08 11:19:49 3151

3151

有一天使用Vivado调用questasim(modelsim估计也一样),仿真报错

2023-05-08 17:12:56 1759

1759 vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

2023-07-18 09:06:59 2137

2137

大家好!今天给大家带来的是modelsim自动化仿真程序。我们在代码编写完成时,通常都需要先进行仿真,然后上板实验。但是如果我们每次仿真都要去新建一个工程,添加.v文件以及testbench文件

2023-07-19 10:10:56 941

941

Modelsim是十分常用的外部仿真工具,在Vivado中也可以调用Modelsim进行仿真,下面将介绍如何对vivado进行配置并调用Modelsim进行仿真,在进行仿真之前需要提前安装Modelsim软件。

2023-07-24 09:04:43 1817

1817

本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。

2023-08-07 15:48:00 1478

1478

Vivado自带的仿真工具在一些基本功能的仿真测试时是可以满足的,但如果你的工程较为庞大,那么自带的仿真工具将有些勉强,除了在数据输出方面的卡顿,在仿真速度上也可能无法接受,这里可以借助第三方仿真工具进行工程仿真测试,Vivado2018各版本支持的仿真工具见下。

2023-11-08 14:47:30 515

515

ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程 序进行仿真,支持IEEE常见的各种硬件描述语言标准。可以进行两种语言的混合仿真,但 推荐大家只对一种语言仿真。

2024-01-14 09:47:47 0

0 首先,你需要选择一个FPGA仿真软件,如ModelSim、Vivado、Quartus II等。这些软件都提供了强大的仿真功能,可以帮助你验证FPGA设计的正确性。

2024-03-15 14:00:29 88

88

正在加载...

电子发烧友App

电子发烧友App

评论