浪潮联合赛灵思宣布推出全球首款集成HBM2高速缓存的FPGA AI加速卡F37X,可在不到75W典型应用功耗提供28.1TOPS的INT8计算性能和460GB/s的超高数据带宽。

2018-10-16 18:50:24 1915

1915 为了帮助大家解决FPGA开发中碰到的相关问题,电子发烧友网和FPGA资深工程师吴厚航(网名“特权同学”)进行了深入的交谈,希望能为工程师群体在电子设计道路上提供参考。

2013-08-20 14:31:45 5641

5641 2018年10月16日, 中国北京 (赛灵思开发者论坛) –今日, 华为在赛灵思开发者论坛( XDF)上与赛灵思联合发布了FX系列FPGA加速卡,为基因测序、视频编码、图片处理、数据压缩等业务提供

2018-10-17 13:42:02 3892

3892 跪求两位数累加显示函数代码谢谢

2017-01-12 16:29:46

FPGA 中的Block Diagram能直接联合Modelsim仿真吗?如果不使用Block Diagram,是能够正常联合Modelsim仿真的,但是使用了Block Diagram模式后,配置一样,但是总是报错

2016-10-08 17:12:26

CPU降低20倍,FPGA处理性能是CPU机器的6倍,验证了FPGA能进行计算加速的能力,同时也增强了FPGA联合团队的自信心。(图1)图片转码中FPGA和CPU延时对比(图2)图片转码中FPGA和CPU

2017-04-15 16:17:41

`急急急!两位一体共阳极数码管显示驱动代码表是什么?`

2013-01-12 23:50:06

小弟现在想做一个利用51单片机(at89s52)做一个倒计时定时器,为节约io口,我想采用两位一体数码管(十脚),还希望通过按键设定初始值,不知道电路如何设计,程序这么写,望各位大侠伸出援助之手,小弟不胜感激。。。

2011-08-05 16:25:47

我现在是让他先亮2,然后把2灭掉。再亮1,1灭掉。再亮2,如此循环。。。虽然看上去数码管一直都是显示21。但是总感觉有点怪怪的。所以就来问一下论坛的大神。两位数码管显示两个相同的数字还是理解的,但是

2020-05-26 16:03:00

哪位朋友有两位共阴数码管封装图,我下载了很多封装图库但都是一位或四位的,求资源,谢谢

2017-01-09 11:27:20

程序想实现两位共阴数码管显示两位数值,数值设定大于50时候,蜂鸣器响的频率比较快,数值设定不大于50时候,蜂鸣器响的频率比较慢。蜂鸣器和数码管单独程序的时候都是正常,但是两个程序工作的时候,蜂鸣器

2016-07-05 22:59:11

各位大神有两位半数码管的显示程序吗?套用函数那种,我写的就是一个个列出来的那种,太长了。。。所以想优化一下,拜托,嘿嘿嘿(抱拳)

2017-07-17 15:28:44

你好,xilinx工程师2位文件可以一起下载到FPGA吗?这样做的目的是使用FMC板上的GTX。我希望将KC705的晶振时钟映射为FMC子板的refclk。所以我有2位文件:一个是IBERT,另一个

2019-04-10 10:44:04

ARM微处理器中支持字节、半字、字三种数据类型,其中,字需要4字节对齐(地址的低两位为0)、半字需要2字节对齐(地址的最低位为0)。我想问的是括号中的内容是什么意思呢?请牛人帮忙解释一下!谢谢

2022-11-03 15:23:57

BURKERT伺服辅助两位两通隔膜阀00138962现货促销德国宝德BURKERT伺服辅助2/2路隔膜阀媒体分开降低功耗不锈钢外壳,适用于腐蚀性介质电路功能NC或NO输入2516上海就瑞机械设备

2018-07-24 18:44:09

协议要求pid包有4位进行区分,但是ch 554作为从设备只能有两位pid识别码,如何区分?是数据,还是令牌?CH554 作为设备时,pid只有两位,bUIS_TOKEN1 和 bUIS_TOKEN0,如何区分令牌包是数据还是其他?

2022-06-13 07:16:26

Debussy 能和64位的modelsim联合吗?

2017-09-19 20:31:35

USB 芯片和软件厂商飞特蒂亚(FTDI)公司发布一款灵活而强大的开发平台 Morph-IC-II,可加速基于FPGA的应用与制作,并简化先进逻辑电路设计中整合高速480Mbit/s USB通讯作业

2019-07-03 08:29:05

错误、两位错误和其他错误。请参阅下面的屏幕截图。 然而,当我在自定义 PCB 中将相同的参数值更改为更高的值时,我没有得到任何一位和两位错误。请参阅下面的屏幕截图; 如果我将此参数设置为必须的值,那么

2023-04-18 07:07:16

Numatic两位五通电磁阀维修与保养NUMATICS电磁阀阀门使用维修与保养: 1.每周检查一次阀门关闭时的密封性能,即用手摸、耳听感觉判定阀门密封效果,发现问题及时报告处理;上海就瑞机械设备

2018-07-01 17:02:54

各位大神求指导, S3C2410AGPB端口低两位与次低两位两个反逻辑LED指示灯的交替闪烁,这个当初没好好学,求指导

2023-11-14 20:22:42

iMPACT下载界面,将本实例工程下的sp6.bit文件烧录到FPGA中在线运行。确保P10的PIN2和PIN3用跳线帽短接。此时当我们使用导航按键进行DA输出数据设定,则相应的高两位和低两位数码管都会发生变化,而且基本是一致的。这说明AD和DA芯片都能正常的工作。 `

2016-05-30 08:23:06

`作者从2009年1月起,在《电子世界》杂志上连载了《手把手教你学CPLD/FPGA设计》讲座。《手把手教你学CPLD/FPGA与单片机联合设计》以此为蓝本,另外增加了大量的篇幅与实验例子进行充实

2015-01-06 17:21:59

作者从2009年1月起,在《电子世界》杂志上连载了《手把手教你学CPLD/FPGA设计》讲座。《手把手教你学CPLD/FPGA与单片机联合设计》以此为蓝本,另外增加了大量的篇幅与实验例子进行充实

2014-12-29 17:10:05

去形容了。本文Andrew不仅仅对FPGA入门学习流程做了详细的分享,更是对FPGA开发工作的要求分成大公司和小公司两个层面来分析。你能想象曾经从一个疏忽学业的人成为一名资深FAE的嘛? &

2014-08-18 15:38:50

/*本例程是C语言的位域操作示例这里为什么位域结构体与联合体一起使用?-->因为这样定义后,即可以单独使用标志位 也可同时使用整个字节数据主要应用:单片机C语言好处:用标志位可以节省RAM空间

2021-07-14 06:23:12

求助,不怎么懂这题该怎么做。求教。用两片四位全加器74283和必要的逻辑门设计一个数制转换电路,实现将输入的两位十进制数转换成二进制数,十进制数的输入采用8421BCD码来表示。用multisim仿真画图。

2016-07-01 20:13:27

32.768kHz振荡器为OSCSCLK,此控制位无效。是不是可以这样理解,假设外接晶振 12MHz 作为系统时钟,那么(CLKS1CLKS0)两位配置情况的机器周期对应如下:00:一个机器周期 = 1/12MHz

2013-12-06 13:47:38

,其值显示在数码管的低两位。图10.80 AD和DA联合实例功能框图本实例模块划分如图10.81所示。图10.81 AD和DA联合实例模块层次板级调试连接好下载线,给CY4开发板供电。打开Quartus

2019-01-26 16:52:56

单片机串口显示正常,为什么数据统计的数量少两位呢

2023-10-25 06:34:02

`吓到两位大叔了。。。`

2012-10-24 16:23:08

在FPGA上加速过winograd吗,有没有和arm端做过加速结果比较

2022-09-21 11:28:56

FPGA加速卡是如何产生的?主要的FPGA加速卡产品有哪些?基于加速卡的FPGA生态系统布局是怎样的?

2021-06-17 06:07:15

keil proteus仿真软件 三、实验内容在proteus软件上实现8个发光LED,并通过编写程序控制LED发光现象并显示自己的学号末两位。 四、实验要求: 在LED中显示自己的学号后两位

2018-07-19 07:00:04

堆栈指针的最低两位永远是0的原因是什么?

2022-01-26 06:09:38

FAST包处理器的核心功能是什么如何使用赛灵思FPGA加速包处理?

2021-04-30 06:32:20

我在用c语言编写lcd显示的简易计算器,现在遇到一个问题,除法运算时怎样编写可以实现结果保留两位小数呢?大神们给个大概思路就好

2019-09-26 22:52:56

前言:做STM32的时候,定时器有两个倍频系数,有时候频率需要精确到小数后面,本例说明如何在小数点后面两位精确:STM31F103的最大频率为7.2000e+07,那么如果要精确到小数点后面两位

2021-08-17 07:02:19

设计一个两位倒计时秒表,可通过按键启动和暂停,计时显示于数码管。

2019-10-20 10:31:01

宝德0330型两位两通电磁阀,宝德中国区域总代理原装德国宝德BURKERT 0330 两位两通产品特性两位两通电磁阀的技术参数,带伺服膜片和与介质隔离的三通先导控制。标准供货为常闭和常开回路功能

2018-07-18 08:58:27

新手求助5脚两位半数码管是怎样进行工作的?使用5脚两位半数码管有何注意事项?

2022-03-01 06:45:13

本人想用dsp和fpga联合弄步进电机控制,请问一个大概的实现方向是什么样的

2015-04-16 16:24:17

以前没有做的两位停止位的485通信,最近刚碰到

2023-06-19 10:29:31

想用ARM和FPGA联合调用控制电机等,不知道现在主要用哪些芯片呢

2017-02-04 10:32:17

求助,如何利用ne555,lm393,74ls47芯片实现两位共阳数码管的动态显示。

2021-12-23 19:37:01

!大家一起来看看特权同学告诉你哪些不为人知的秘诀:设计教训如何成就称职的FPGA资深工程师?作为ASIC领域中一种半定制电路,FPGA的发展不但解决了定制电路不足,并且能够克服可编程器件门电路数有限

2013-08-20 16:50:48

4*4矩阵键盘输入一个两位数,显示在一个两位数码管上。程序如下:现在的问题是我接一位的数码管能正常显示数,接两位的就像图片中乱码了?这是为什么呢?#includeunsigned char code

2017-02-24 21:26:00

第2位和第3位,跟下面的第0位和第1位什么区别?看他的字面意思好像是一个硬件状态指示,就是说第0,1位配置为什么,这两位就相应的变为什么吗?

2019-01-16 01:56:22

我在用c语言编写lcd显示的简易计算器,现在遇到一个问题,除法运算时怎样编写可以实现结果保留两位小数呢?给个大概思路就好

2019-04-17 03:16:29

所以先求出原码再计算的,符号位存在别的变量中,每个轴的分量计算 :*39/100 扩大了100位实际是保留两位小数起初校验值 是0x10,-0x03,-0x03,但是X轴的输出范围有些大,便改为0x00

2019-04-16 03:06:21

全球领先的中文互联网搜索引擎提供商百度正在采用赛灵思FPGA加速其中国数据中心的机器学习应用。两家公司正合作进一步扩大FPGA加速平台的部署规模。新兴应用的快速发展正日渐加重计算工作的负载,数据中心

2016-12-15 17:15:52

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-03-04 11:13:54

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-03-11 11:07:39

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-03-18 11:16:02

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-03-25 11:34:03

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-04-01 10:53:42

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-04-11 14:45:24

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-04-18 14:12:57

产品编号:1501013高性能FPGA计算加速卡( B-PCIE-SFPP )数据手册( Data Sheet )Version 1.0 清华大学设备仪器厂智能计算研发中心Copyright

2016-04-27 11:51:14

资深玩家教您看笔记本键盘

笔记本电脑中键盘是成本比较低的部件,就大批量采购成本而言,相比起cpu动辄200美金以上的身价,最

2010-01-19 11:43:16 684

684 看似简单的几个问题,Andrew却回答的井井有条,小编已经没有办法有什么其他词语去形容了。本文Andrew不仅仅对FPGA入门学习流程做了详细的分享,更是对FPGA开发工作的要求分成大公司和小公司两个层面来分析。你能想象曾经从一个疏忽学业的人成为一名资深FAE的嘛?

2014-08-21 10:11:47 31136

31136 SuperVessel将包括赛灵思SDAccel开发环境,支持用C、C++和OpenCL实现FPGA加速 All Programmable 技术和器件的全球领先企业赛灵思公司与IBM公司今天联合宣布

2017-02-08 16:06:08 228

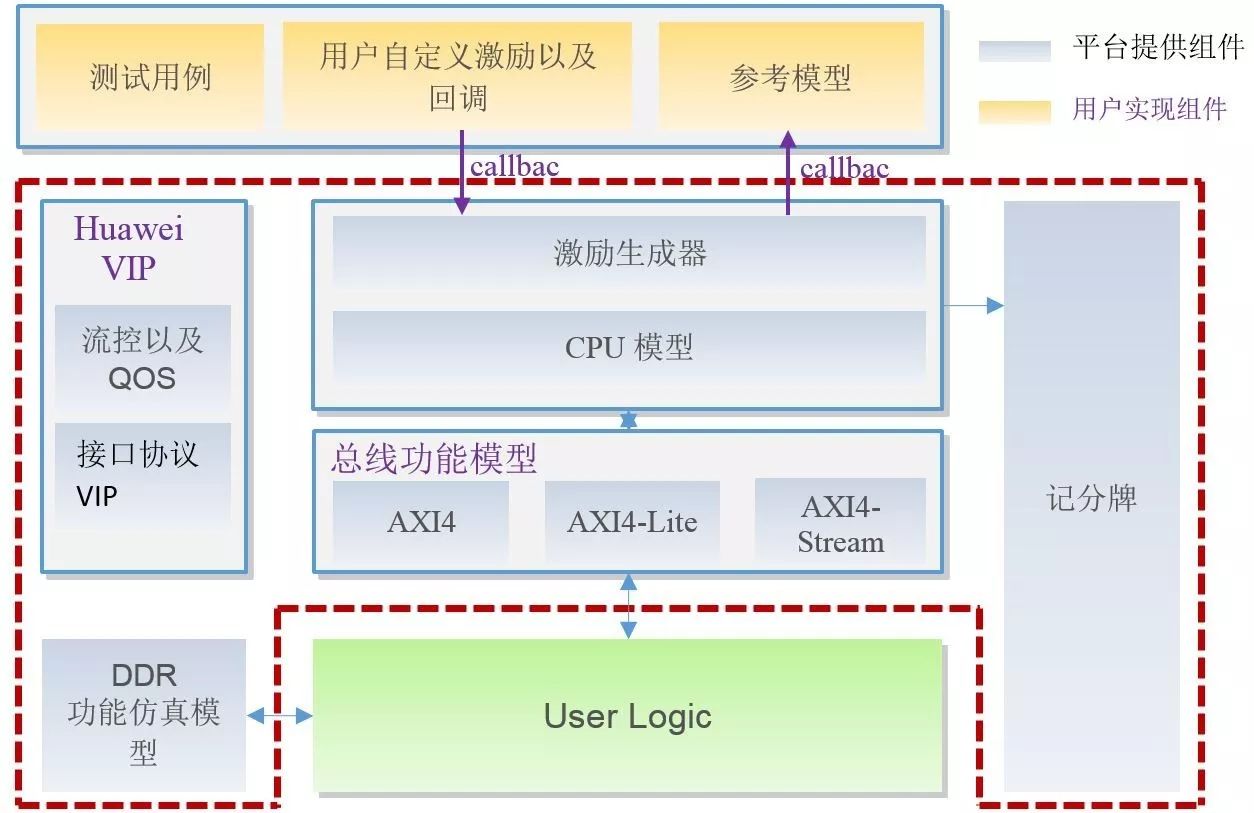

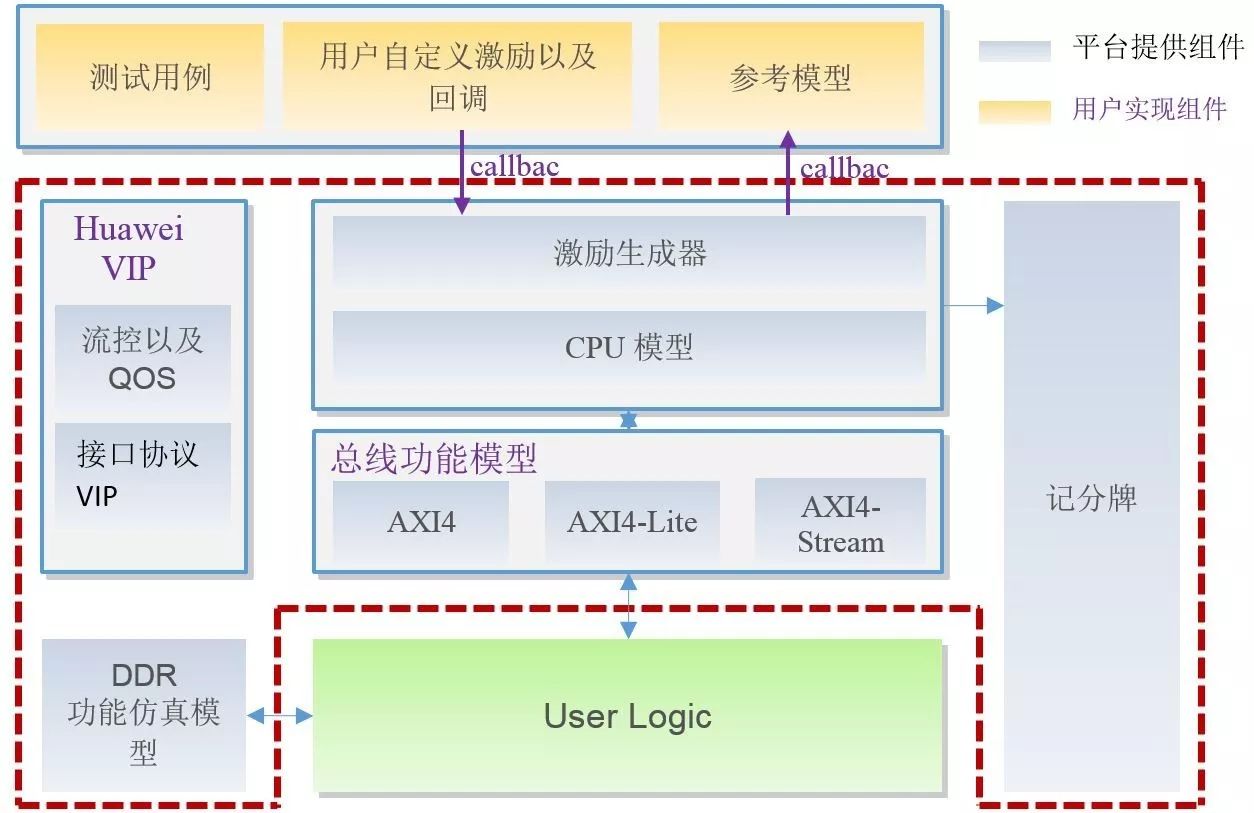

228 在数据中心引入 FPGA 并实现云化加速业务成为必然趋势。随着华为云 FPGA 加速服务的推出,打破原有 FPGA 开发、测试和应用存在的较高门槛,开启了一个颠覆 FPGA 开发的新时代!

2017-10-10 10:49:17 4798

4798

据称,本次三家联合发布的解决方案是业界首个在电信云中采用FPGA完成商用级vBRAS数据面调度加速的端到端方案。该联合方案硬件部分是联想的交换机和服务器,其中包括英特尔的CPU和PAC;软件部分由联想的VIM、赛特斯的VNFM、还有中国电信北京研究院的NFVO组成。

2018-07-06 08:30:00 1120

1120 随着IT和人工智能技术快速发展,寻找高能效比的数据中心加速方案至关重要。华为在赛灵思开发者论坛上与赛灵思联合发布了FX系列FPGA加速卡,为基因测序、视频编码、图片处理、数据压缩等业务提供了高能效比的加速解决方案

2018-11-07 09:29:33 9845

9845 近日,基于现场可编程门阵列(FPGA)的数据加速器件和高性能嵌入式FPGA(eFPGA)半导体知识产权(IP)领导性企业Achronix半导体公司,与Molex旗下的一家领先企业级FPGA加速器产品供应商BittWare今日联合宣布:推出一类全新的、面向高性能计算和数据加速应用的FPGA加速卡。

2019-10-31 15:11:33 737

737 Achronix半导体公司与Mo-lex旗下FPGA加速器产品供应商BittWare联合推出全新的、面向高性能计算和数据加速应用的FPGA加速卡,可实现云计算与边缘计算加速,助力高带宽应用。

2019-11-08 15:07:23 562

562 近日,FPGA的数据加速器件和高性能嵌入式FPGA半导体知识产权Achronix公司与Molex旗下的一家领先企业级FPGA加速器产品供应商BittWare在深圳联合举行了新产品的媒体发布会

2019-11-08 15:11:59 1050

1050 华硕ROG玩家国度与NVIDIA联合打造ROG Swift 360Hz,这是一款拥有360Hz超高刷新率的,24.5英寸专业竞赛屏。

2020-01-07 13:53:13 2167

2167 近日,元脑生态伙伴深维科技与浪潮联合发布业内首个基于FPGA的HEIF图像处理加速方案。

2020-10-23 11:16:53 2200

2200

“创悦智行”联合加速计划由现代汽车集团创新中心(北京)(Hyundai CRADLE Beijing)协同腾讯智慧出行、现代摩比斯(Hyundai Mobis)、Vπ张江孵化器联合发起,旨在依托孵化加速、战略协同、战略投资这一完整创新链路,赋能智能汽车领域的初创企业。

2021-05-24 10:34:40 1271

1271 在去年电子创新网举办的2019FPGA应用创新论坛上,一家低调的FPGA新玩家引发了大家极大的兴趣,它就是EFINIX公司,为何全球FPGA领头羊赛灵思会投资这家公司?它的创始人团队有多牛?他们捣鼓出来的FPGA新架构到底有什么独特性?本文为你详细介绍。

2022-02-09 11:29:32 1

1 正值当前硬件加速器依托异构计算异军突起之际,高性能FPGA和嵌入式FPGA(eFPGA)半导体知识产权(IP)领域的领导性企业Achronix半导体公司近期先后宣布:任命台积电(TSMC)资深

2022-04-06 20:10:05 3169

3169

新技术星期二:加速 FPGA 计算的 2 张卡

2022-12-30 09:40:20 539

539 引言Preface随着芯片设计规模的增加,传统基于单颗FPGA的设计调试方法已经不能满足对大型设计的调试需求,因此多FPGA联合调试技术应运而生。本次国微思尔芯白皮书《先进多FPGA联合深度调试方法

2022-06-16 10:16:48 627

627

电子发烧友网站提供《基于FPGA的加速基础知识.pdf》资料免费下载

2023-09-18 10:12:20 0

0

电子发烧友App

电子发烧友App

评论