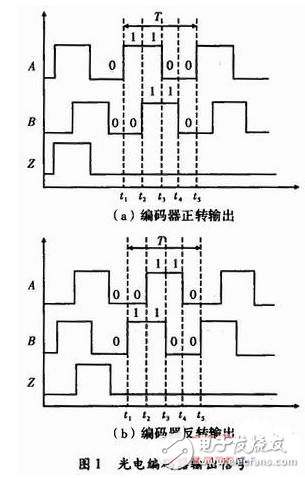

本文主要介绍了增量式编码器接口电路的设计与实现。一个基于FPGA的简单且精度高的接口电路,其结构简单、性能可靠。具有滤波、硬件辨向、4倍频计数和数据锁存等功能。计数结果以并口输出,可与PC机、ARM

2018-03-04 14:18:17 18615

18615

类和MiniBatchSparsePCA类算法原理一样,都是把降维问题用转换为回归问题,并在优化参数时增加了正则化项(L1惩罚项),不同点是MiniBatchSparsePCA使用部分样本特征并迭代设置的次数进行PCA降维 。

2019-04-17 09:57:59 12403

12403

在前两篇关于 Python 切片的文章中,我们学习了切片的基础用法、高级用法、使用误区,以及自定义对象如何实现切片用法(相关链接见文末)。本文是切片系列的第三篇,主要内容是迭代器切片。 迭代

2020-11-29 10:11:00 564

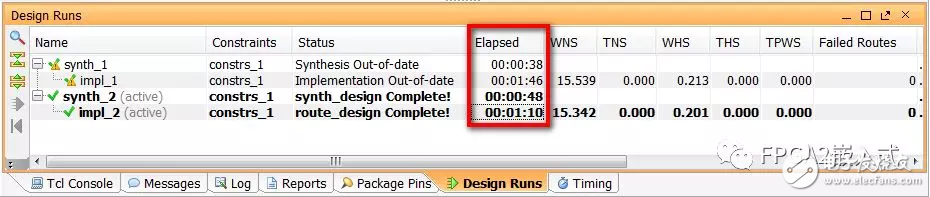

564 增量编译:使用增量编译满足最后时刻 HDL 变动需求,仅针对已变动逻辑进行布局布线,从而可节省时间。

2020-12-13 10:14:00 4563

4563 在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果

2024-01-02 14:13:53 434

434

FPGA编译出错,求解

2019-04-01 01:47:43

我刚刚接触NI采集设备,想要编译一个FPGA程序,但是连接本地编译器一直出错,无法编译。我用的是labview2016 32位中文版,驱动都装了,xilinx编译器也是对应的。大神们能否告诉我是为什么?如下图:

2017-09-13 15:33:56

,到底是哪个出错了,是比较难定位的,这就是FPGA的难点之一。(2)设计思维风格选择——4大建议2个推荐软件设计思维和硬件设计的思维风格区别明显,在选择之前先通过表3了解两种风格的优缺点。表3 软硬件

2020-12-21 16:44:36

刚刚学习fpga方面的知识,fpga如何测量一个增量式编码器,消除抖动的话是否也是在上升沿和下降沿都进行计数处理,这样的话怎样设定可以保障计数器可以同时在两个always 下进行计数,可以给一下大概的例程最好

2016-01-11 18:27:47

FPGA设计经验的技巧,用数学思维来简化设计逻辑!

2021-03-17 06:45:25

朋友们,xinlinx有没有增量编译的技术,最近做个工程占用了快80%,用了比较多的ip核,每次改一个参数就要重新综合半天,这样调试效率实在太低,我用的是ise13.2,和工具有关系么?

2014-06-14 22:43:59

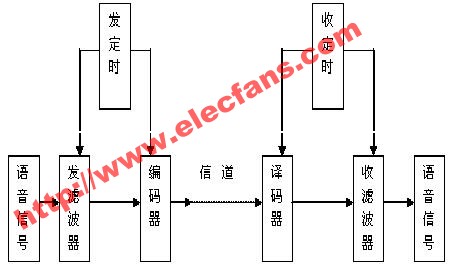

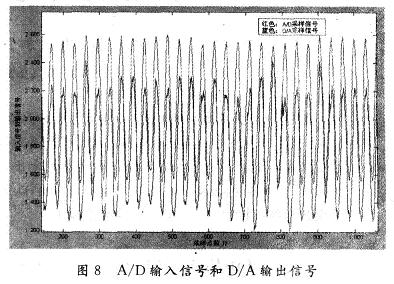

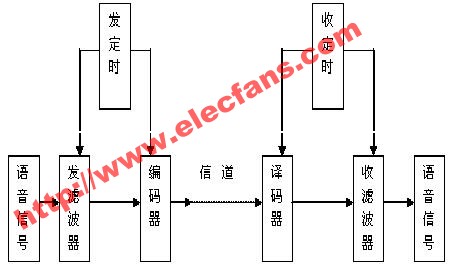

增量调制(ΔM)编译码实验一、实验目的 1、了解语音信号的ΔM编码过程; 2

2009-10-11 08:58:46

迭代不同WIFI连接的正确方法?

2023-05-04 06:46:12

X(n+1)=a/(b+Xn),其中a,b为正的常数迭代的终止条件为|Xn+1-Xn|

2016-06-06 02:02:53

用MC33035搭配AD5621驱动直流无刷电机,采用增量式PID速度闭环控制,为什么电机高速(600rpm以上)运行误差小,低速(600rmp以下)误差大?

2021-01-19 15:21:08

使用高云®半导体 GW1NRF 系列 FPGA 产品做电路板设计时需遵循一系列规则。本文档详细描述了 GW1NRF 系列 FPGA 产品相关的一些器件特性和特殊用法,并给出校对表用于指导原理图

2022-09-28 08:53:49

器重复判断(集合中还有未被访问的元素)获取下一个元素的访问方法读写下一个元素(也可能是删除这个元素)结束上述范式展示了迭代器的用法,通过迭代器,遍历元素变得简单直接(将遍历算法封装在迭代器中),不用每次

2022-09-05 11:38:47

范式是:初始化迭代器重复判断(集合中还有未被访问的元素)获取下一个元素的访问方法读写下一个元素(也可能是删除这个元素)结束上述范式展示了迭代器的用法,通过迭代器,遍历元素变得简单直接(将遍历算法封装

2022-08-30 10:31:43

labview fpga编译一直出错。在别人建的项目里新建vi代码可编译,自己建的里面打同样代码就不行。里面用了Dma-fifio,fxp的数据类型,labview2015+2015SP1Xilinx14_7进行编译。截图如下:

2016-08-05 19:25:34

python迭代器1. 可迭代对象可以利用 for 循环的对象,都叫可迭代对象。列表、元组、字典、字符串等都是可迭代对象。# 以列表为例>>> alist = [0, 1, 2

2022-02-24 15:42:43

这里写目录标题volatile 用法struct 用法enum 用法预处理器与预处理指令文件包含#includevolatile 用法volatile原意是“易变的”,在嵌入式环境中用

2022-01-24 07:12:06

压一压就好了! Altera不能真的压缩时间,但我们能改变“速度”!从数年前的版本开始,Quartus2软件中就整合了一种新技术,或者说一种新的设计流程:增量式编译(Incremental Compilation)。它是ALTERA为解决大容量FPGA设计编译时间太长的问题给出的一个新式工具!您,了解它吗?

2019-09-19 08:22:03

在众多的语音编译码调制中,连续可变斜率增量调制(CVSD)作为许多增量调制中的一种,只需编一位码,在发送端与接收端之间不需要码型同步,量阶△的大小能自动地跟踪信号变化,因而具有强抗误码能力,在

2019-08-07 07:04:27

什么是模型思维?怎样确定一个模型?

2021-09-18 06:41:30

增量实现由哪几个流程构成?增量实现流程有哪几种模式?怎么证明增量编译后,原始设计成功锁定了呢?

2022-02-16 07:54:31

本手册主要介绍基于HYCON8-bitOTPMCU的C编译器用法;以C语言为基础,介绍HYCONCIDE的用法及编程;本手册适合有C语言基础的开发人员,同样也适用无C语言基础的开发人员;第二章介绍

2022-01-25 07:17:30

的、可以非常有效地相辅相成。从教育视角而观之,如何让我们的两种学生:机器学生与人类学生,两者携手共舞、一起创新,成为最新潮的创新教育思维。 再从逻辑思维视角而观之,人类与生俱来的三项逻辑思维

2021-01-04 10:16:36

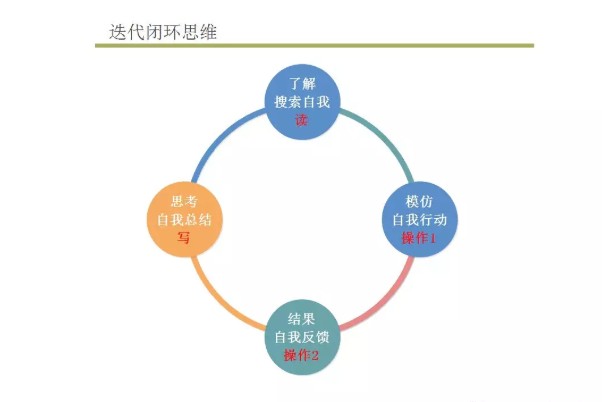

),然后再模仿着写,最后不看书也能写出来。编译完代码,就打开RTL图,看一下综合出来是什么样的电路。HDL是硬件描述语言,突出硬件这一特点,所以要用数电的思维去思考HDL,而不是用C语言或者其它高级语言

2020-10-21 15:07:39

描述TIDA-01370 是一款具有以下用途的 TI 设计:在存在通过光学旋转增量编码器获取的闭环反馈的情况下,在由 DRV8880 驱动的步进电机中进行失速检测。该参考设计显示如何使用闭环算法

2018-07-13 07:30:11

将函数的迭代过程图示出来,但是是多个初值,每个初值迭代的过程的数值结果都有,显示在一张图上。类似这种图。求大神给个思路,用什么函数

2014-08-18 10:45:38

,即使对源代码做微小改动也会对编译器生成的代码效率产生重大影响。本文将讲述在编写代码时需要注意的事项,但我们首先应明确一点,我们没有必要尽量减少代码量,因为即使在一个表达式中使用 ?:- 表达式、后增量

2021-11-21 08:00:00

,即使对源代码做微小改动也会对编译器生成的代码效率产生重大影响。本文将讲述在编写代码时需要注意的事项,但我们首先应明确一点,我们没有必要尽量减少代码量,因为即使在一个表达式中使用 ?:- 表达式、后增量

2022-04-11 10:17:09

电路设计思维常见的误区有哪些?

2021-06-18 09:53:58

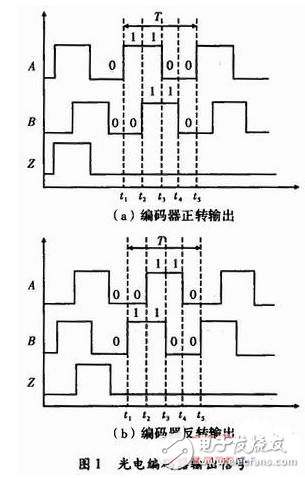

直流电机增量式PID闭环控制原理是什么?如何从编码器A相和B相输出的方波例区分我们所认定的正反的呢?

2021-06-30 06:27:24

PID:智能小车入门(位置式和增量式)PID的公式今年大二,以一个新人的角度来说一下PID及其用法,新人第一次写,有不对的请各位指正。手动狗头

2022-01-14 06:03:54

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2018-08-15 07:53:48

,被广泛应用于电机伺服控制系统中。编码器按信号输出形式分为绝对式编码器和增量式编码器。绝对式光电编码器具有输出数字量可与PC机、ARM或FPGA等器件直接接口,无累积误差等优点,但价格高、制造工艺复杂

2019-06-10 05:00:08

上EasyGo FPGA Solver中的FPGA Coder解算软件,可以将用户灵活搭建的模型直接下载至FPGA中运行,而不需要进行FPGA的编译,最

2022-05-19 09:16:05

。EasyGo FPGA Solver 的优点在于,能够将Simulink的图形化模型利用解算器软件转化成FPGA执行的代码,而不需要进行FPGA的编译

2022-05-19 09:21:43

增量调制(ΔM)编译码实验

一、实验目的

1、 了解语音信号的ΔM编码过程;

2008-10-21 13:24:20 8277

8277

IP验证增量仿真技术的运用

验证涉及每个阶段的迭代循环:仿真、检查结果,改变激励或设计或调试设置,重新仿真并不断重复。在系统调

2009-01-27 17:58:24 834

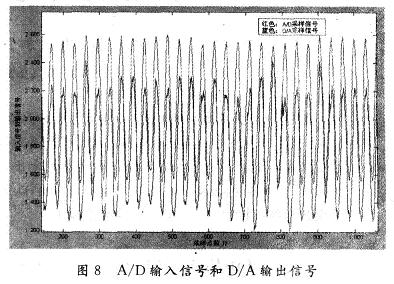

834 CVSD算法分析及其在FPGA中的实现

概 述在众多的语音编译码调制中,连续可变斜率增量调制(CVSD)作为许多增量调制中的一种,只需编一位码,在发送端与接收端之

2010-04-01 16:26:54 2120

2120

分析了光电编码器4倍频原理,提出了一种基于可编程逻辑器件FPGA对光电增量式编码器输出信号4倍频、鉴相、计数的具体方法,它对提高编码器分辨率与实现高精度、高稳定性的信号检测

2011-11-03 15:13:16 75

75 本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45 增量式编译(Incremental Compilation)是ALTERA为解决大容量FPGA设计编译时间太长的问题给出的一个新式工具!在本文中我们将阐述QIC在缩短编译时间方面的作用。

2012-12-25 11:26:53 4439

4439 状态机原理及用法状态机原理及用法状态机原理及用法

2016-03-15 15:25:49 0

0 基于FPGA的3B4B编译码电路

2017-02-07 14:58:18 11

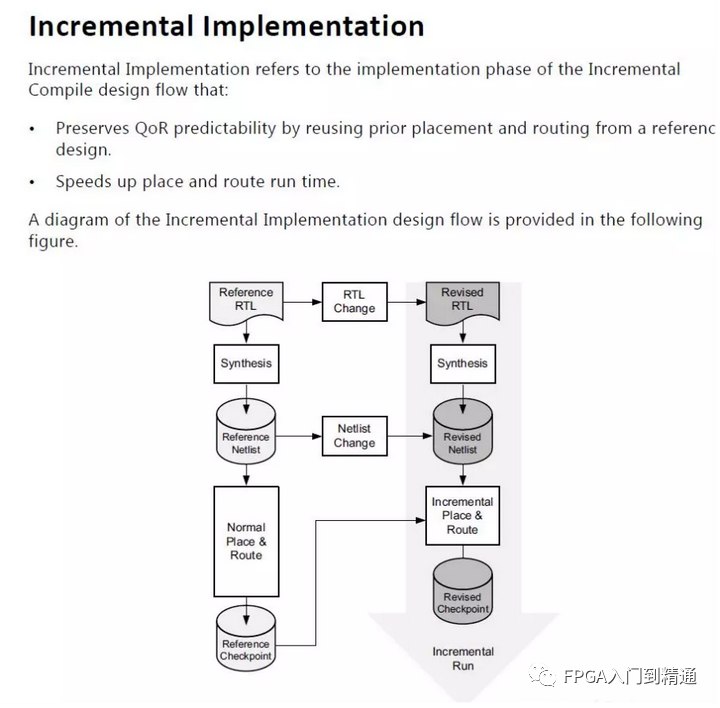

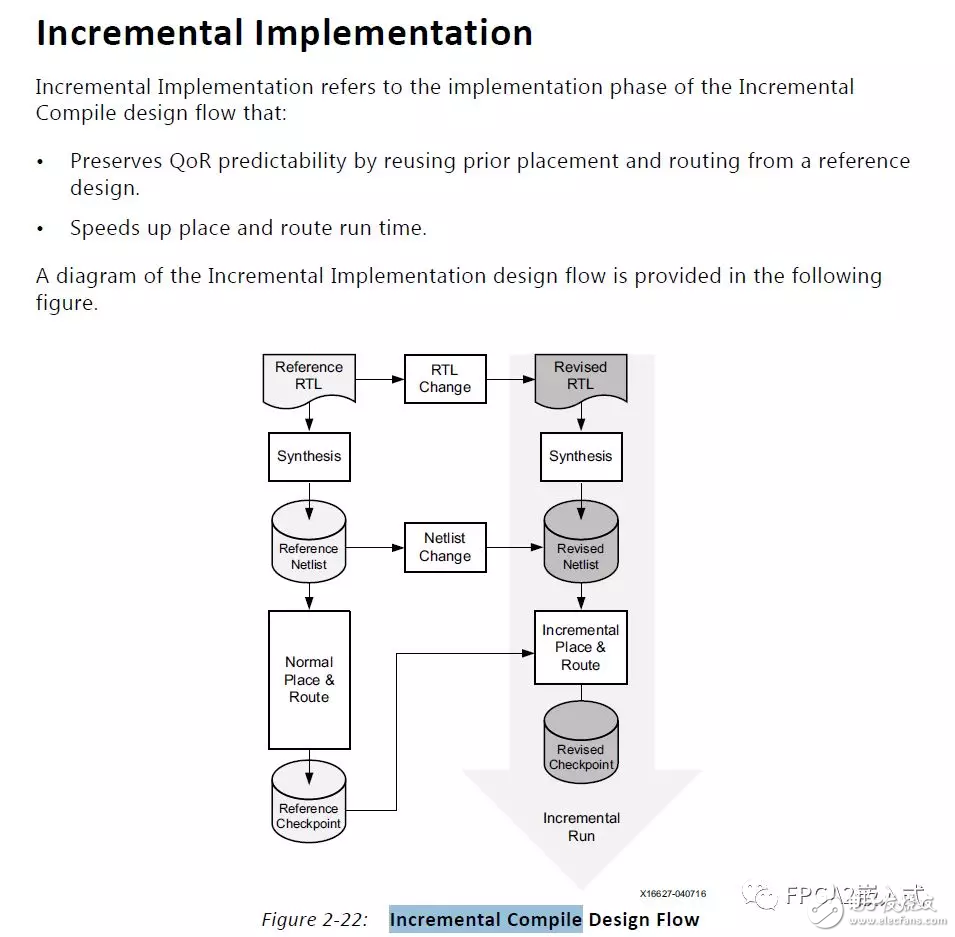

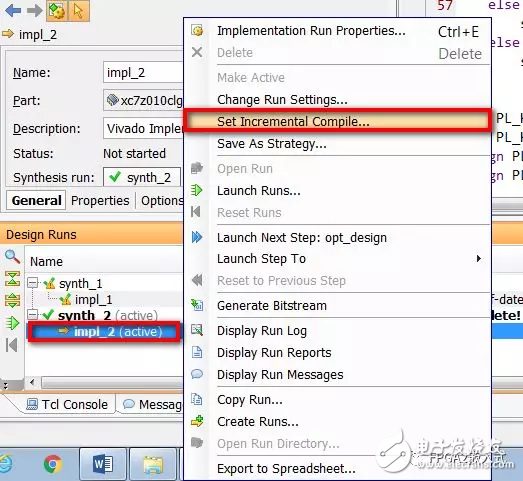

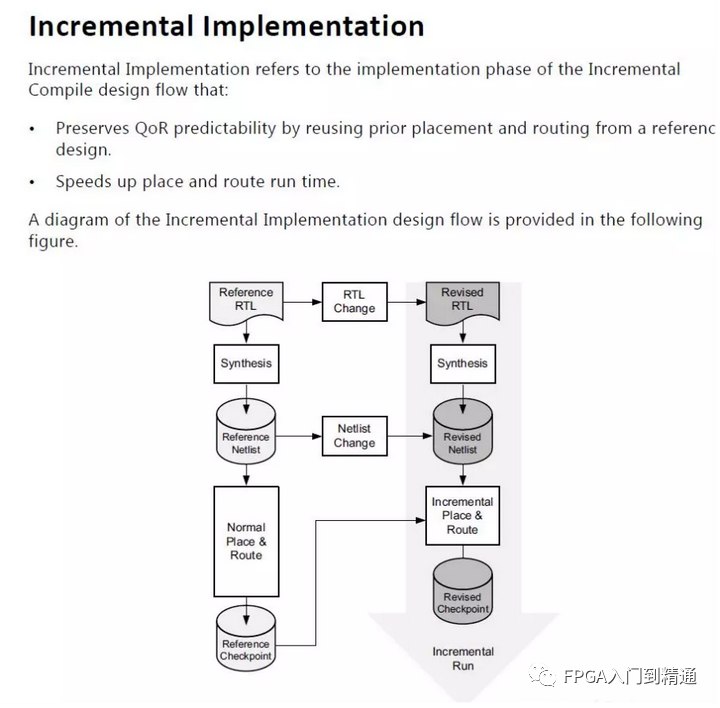

11 Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

2018-07-05 06:06:00 10327

10327 通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解

2017-11-18 12:23:09 2377

2377

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 3928

3928

在演讲中,尤瓦尔·赫拉利谈到了人类的DNA数据是举足轻重的宝贵资产,人类的身体、大脑、思维也比工厂、车辆、武器更重要 ,是21世纪重要经济产物。未来,掌握数据,尤其是人类基因数据,就控制了未来、生命的未来。或许,过一两百年未来人类将利用这些数据改造人体、大脑和思维,现在的我们也将成为最后一代智人。

2018-07-04 08:25:00 394

394 ,融合其分类结果得到组合分类器;增量学习中用权值刻画样本的空间分布特性,对样本进行迭代加权,利用遗忘因子实现新增样本的选择及历史样本的淘汰;采用基于HBase的控制器组件用以调度迭代过程,持久化中间结果并减小MapReduce原有框架迭代过程中的带宽压力。多

2017-12-09 11:34:37 0

0 本文针对线性大工业过程的稳态递阶优化控制,当系统存在初始状态漂移时,研究了基于脉冲型信号的加权闭环PD-型迭代学习控制算法,并在Lebesgue-p范数意义下利用推广的Young卷积不等式分析了算法

2017-12-19 10:58:01 0

0 GCC是由理查德·马修·斯托曼在1985年开始的。他首先扩增一个旧有的编译器,使它能编译C,这个编译器一开始是以Pastel语言所写的。Pastel是一个不可移植的Pascal语言特殊版,这个编译器也只能编译Pastel语言。

2018-03-13 15:08:27 5397

5397 这些年,这些概念火爆过、恐惧过,也逐渐深入到每一个互联网人的血液中。这些思维,过时了吗?并没有。只是……在这一轮AI浪潮中,不适用了。在移动互联网之后,是一个AI技术赋能万物的时代,是一个软硬件结合

2018-04-08 09:49:00 1140

1140

FPGA到最后自然是规模越来越大,编译时间越来越长。解决问题的方法通常来说应该从工具和设计入手。

2018-08-04 09:16:18 6130

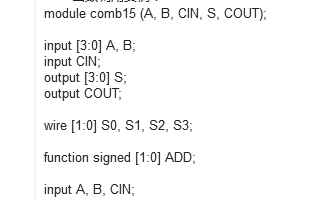

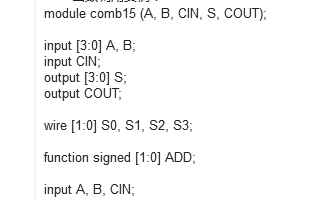

6130 大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA verilog中的function用法与例子。 函数的功能和任务的功能类似,但二者还存在很大的不同。在 Verilog HDL 语法中也存在

2018-08-10 13:42:16 18695

18695

关键词:FPGA , PLD 讲过了独立按键检测,理所当然应该讲讲FPGA中矩阵键盘的应用了。这个思维和电路在FPGA中有所不同,在此,在此做详细解释,Bingo用自己设计的成熟的代码作为案例,希望

2018-09-26 07:54:02 225

225 到Bluespec的编译器。这个P4FPGA的工作发表在会议第一天的NetPL workshop上,P4语言与FPGA的结合引起了工业界的重视。因此,本文将分享搭建P4C与P4FPGA联合编译环境的经验

2018-10-02 09:00:01 492

492 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:56:00 2512

2512 了解使用Vivado 2016.1中引入的增量编译流程进行调试的好处,以及在使用增量编译实现时添加/删除/修改ILA内核所需的步骤。

2018-11-30 06:19:00 2755

2755

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-29 06:32:00 3336

3336 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-30 19:24:00 4251

4251 当RTL代码修改较少时,使用增量编译功能可以提高工程的编译速度,Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

2019-01-22 17:27:48 9325

9325

这是国外一个著名的捣鼓硬件的老外反编译国产掌机代代星的内核并运行在自制的FPGA上的视频,这老外还提供了一份技术文档。

2019-12-26 07:03:00 2045

2045 随着互联网技术架构的快速普及,企业对于NoSQL的需求也越来越大,在云计算的潮流下,如何将云服务的思维和技术纳入到数据库创新,成为摆在云服务厂商面前的一道难题。

2019-06-14 16:07:54 443

443 万幸的是,当今FPGA工具(比如Xilinx的 Vivado)都有很多开关和设置选项来帮助时序收敛。InTime的方法,就是通过调整FPGA工具的编译过程来解决用户的时序问题和其他性能问题。

2019-07-26 15:56:23 3187

3187

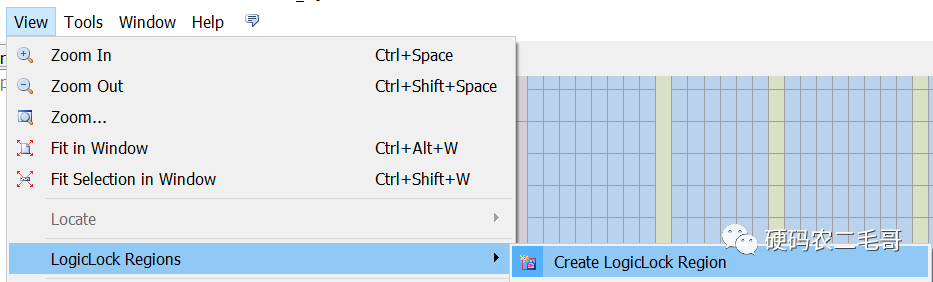

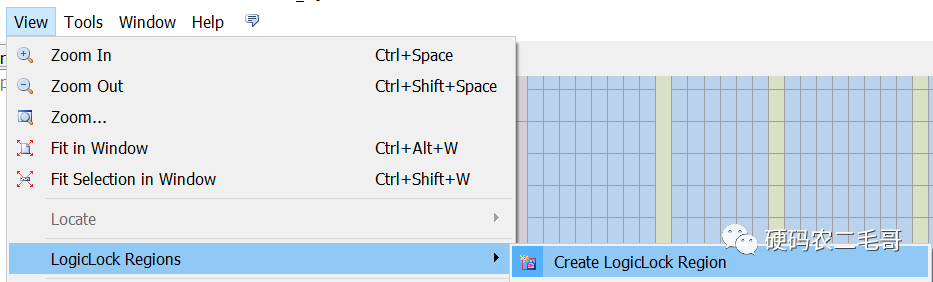

本文针对Vivado中实现的逻辑锁定和增量编译进行的工程实例介绍,文中有对应工程的下载地址。友情提示:(1)增量编译只允许修改当前工程不超过5%的时候才有效,一般应用于较大工程添加修改

2019-07-06 10:32:42 6745

6745

本手册主要介绍基于HYCON 8-bit OTP MCU的C 编译器用法;以C语言为基础,介绍HYCON C IDE的用法及编程;本手册适合有C语言基础的开发人员,同样也适用无C语言基础的开发人员;

2020-10-15 08:00:00 0

0 人工智能在市场营销领域取得的成功,揭示了人类的一些思维和行为模式,这些模式可以转化为其他应用程序。

2020-11-06 11:38:05 3389

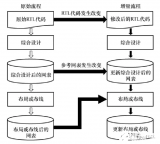

3389 所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线。

2021-04-14 12:01:56 2456

2456

电子发烧友网为你提供FPGA设计经验技巧,用数学思维来简化设计逻辑!资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-01 08:55:07 22

22 现场可编程逻辑阵列(FPGA)资源丰富,结构灵活,近年来发展迅猛。针对其特点,本文设计了基于FPGA的增量式光电编码器的接口电路,实现了对增量式编码器脉冲信号的倍频、鉴相及计数等功能。

2021-04-27 13:57:50 3885

3885

很多优秀的代码,都会借用预编译指令来完善代码,今天就来讲讲关于预编译指令的内容。 常见的预处理指令如下: #指令,无任何效果 #include含一个源代码文件 #define义宏 #undef消已定

2021-06-23 17:30:32 1363

1363

转,但是可能你自己还有点舍不得。 总之,确定了在这一行,靠的就是思维与技巧结合,注重实践方法,方能在其中有一席之地。 从裸机思维开始 嵌入式系统是一个面向应用高度裁减的专用计算机系统,嵌入式软硬件也可以这样定义 软件:

2021-09-02 11:10:17 2876

2876 关于增量编译所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线...

2021-12-20 19:11:57 6

6 PID:智能小车入门(位置式和增量式)PID的公式今年大二,以一个新人的角度来说一下PID及其用法,新人第一次写,有不对的请各位指正。手动狗头

2022-01-14 11:22:54 17

17 2021年1-11月,奇瑞累计销售汽车85万辆,同比增长38.3%,高于4.5%的行业增幅。在奇瑞集团董事长尹同跃看来,奇瑞市场表现“稍好一点”的原因,是在“新四化”背景下,为企业装上了“两个翅膀”:用户思维的和互联网思维。

2022-03-16 11:18:59 1261

1261 电化学与其他的科学有其特殊性。它不像机械一样是可见的,也不是如同电子学是可以凭借抽象思维的,而电化学需要抽象思维和试验相结合。 例如,在国际上铅酸蓄电池的第一位生效原因是硫化,但是,这就

2022-05-22 18:17:48 267

267 增量实现由两个流程构成:原始流程和增量流程,如图所示。其中,原始流程提供网表。

2022-10-10 14:16:04 1120

1120 下对高精度的要求,芯明天专门设计、研发了XYZ65N81E26压电螺钉运动平台,该平台配备了增量式编码器,对运动行程、精度等可进行精确控制,且精度可达1.5μm。 芯明天XYZ65N81E26压电螺钉运动平台 特点 XYZ三维运动 配有闭环增量式编码器 行程

2023-02-09 10:17:06 417

417 逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。 增量编译功能,可以使设计更快速时序收敛,加快编译速度。

2023-05-25 11:22:11 800

800

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项。

2023-05-25 18:25:34 2890

2890

伴随着算法的高速发展,FPGA由于其高吞吐量的特点,在算法实现的领域大放异彩,戴姆勒、百度等厂商都纷纷推出了基于FPGA、MPSOC的智能驾驶部署方案。

由于汽车行业存在设计周期短的显著特点,为适应市场规律,各大FPGA厂商均推出了不同的解决方案,力图降低FPGA的开发难度,缩短设计的迭代周期。

2021-07-26 11:18:06 593

593

`ifndef是SystemVerilog/Verilog中的一种条件编译命令,可以认为其是"if not defined"的缩写,其用法与`ifdef相反,他们主要用来根据其后

2023-06-25 15:59:54 1669

1669

Kevin一直认为学习FPGA的朋友的逻辑思维能力应该是比其他人要强很多的。在很多求职网站上都可以看到FPGA相关行业的招聘信息可能会有这样的一条工作职责:负责项目的逻辑设计。

2023-08-28 09:50:59 503

503 增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。

2023-09-01 09:36:49 362

362

增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。它解决了实现阶段针对快速迭代的需求,显著节省了编译时间,还能确保所得结果和性能的可预测性。 以下图表显示了在一整套困难的设计上采用增量实现流程后,所节省的编译时间的变化趋势。

2023-09-04 10:07:01 372

372

增量综合的工作方式与增量实现流程相似,但仅适用于综合阶段,并且不会对紧随其后的实现阶段给予引导。

2023-09-08 11:01:37 276

276

电子发烧友App

电子发烧友App

评论