AMD今年推出了Radeon VII显卡,尽管Vega架构及不支持光追让这款显卡备受争议,但这款显卡在制程工艺上创造了记录——因为它首发了消费级7nm GPU,AMD今年年中还会有更多的7nm显卡

2019-03-01 09:48:46 974

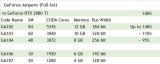

974 为Ampere的Turing GPU架构的继任者将是图形行业的一项重大交易,它将在总体性能和效率上实现比预期更大的性能飞跃。该报告再次指出Ampere采用了7nm工艺节点。 NVIDIA首席

2020-01-06 01:56:00 4825

4825 随着今年迈入 NVIDIA 两年一度的 GPU 升级周期,若没有太多意外, NVIDIA 应该会在今年公布全新的 GPU 架构,也就是先前传出代号 Ampere 的 GPU 架构,而现在最有可能公布

2020-01-14 10:56:58 5293

5293 芯片的7nm工艺我们经常能听到,但是7nm是否真的意味着芯片的尺寸只有7nm呢?让我们一起来看看吧!

2023-12-07 11:45:31 1603

1603

3nm工艺,外媒的报道显示,台积电是计划每平方毫米集成2.5亿个晶体管。 作为参考,采用台积电7nmEUV工艺的麒麟9905G尺寸113.31mm2,晶体管密度103亿,平均下来是0.9亿/mm2,3nm工艺晶体管密度是7nm的3.6倍。这个密度形象化比喻一下,就是将奔腾4处理器缩小到

2020-04-20 11:27:49 4113

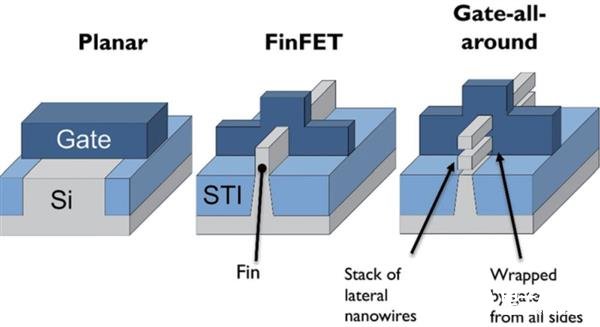

4113 很多晶体管组成的。芯片制程是指在芯片中,晶体管的栅极宽度。因为在整个芯片中,晶体管的栅极是整个电路中最窄的线条。如果栅极宽度为10nm,则称其为10nm制程。纳米数越小,比如从10nm到 7nm,就可以

2019-12-10 14:38:41

GPU和CPU产品依旧在使用五年前的14nm工艺或者其改进版本。新的10nm、7nm工艺虽然已经上市,但是综合频率、功耗、晶体管密度等因素来看,其表现依旧不能令人满意。进入2020年,也就是21世纪20

2020-07-07 11:38:14

:7nm智能座舱芯片行业生产模式

图 55:7nm智能座舱芯片行业销售模式分析

▲资料来源:辰宇信息咨询整理,更多资料请参考辰宇信息咨询发布的《2024-2030全球及中国7nm智能座舱芯片行业研究及十四五规划分析报告》

2024-03-16 14:52:46

描述dcreg12v3a mj2955 lm78122955 MJ晶体管的作用是作为电流放大器,使输出电流达到安培单位,通常如果没有晶体管这个电路只能达到毫安单位。出于电源的目的,晶体管必须不断地

2022-09-05 06:18:39

其实早在2002年Intel即发现了这一技术,一直处于试验演示阶段,现在终于把它变成了现实,Intel打算把它融入到22nm的“Ivy Bridge”芯片,Ivy Bridge晶体管的数量将达到10亿。

2020-04-07 09:01:21

。 8050晶体管及其等效的8550晶体管设计用于低功耗推挽放大器应用中的互补晶体管对。通常,8050晶体管是2瓦放大器,最大集电极-发射极电流为1.5安培,最大集电极-发射极电压为25伏。 基本晶体管

2023-02-16 18:22:30

7nm新工艺的加持:RX 5500 XT可轻轻松松突破2GHz

2021-06-26 07:05:34

这边是NVIDIA HR Allen, 我们目前在上海招聘GPU高性能计算架构师(功能验证)的岗位,有意向的朋友欢迎发送简历到 allelin@nvidia

2017-09-01 17:22:28

及制造工艺分类 晶体管按其结构及制造工艺可分为扩散型晶体管、合金型晶体管和平面型晶体管。 按电流容量分类 晶体管按电流容量可分为小功率晶体管、中功率晶体管和大功率晶体管按工作频率分类 晶体管按

2010-08-12 13:59:33

时,先将hFE/ICEO选择开关置于ICEO档,选择晶体管的极性,将被测晶体管的三个引脚插个测试孔,然后按下ICEO键,从表中读出反向击穿电流值即可。2.放大能力的检测 晶体管的放大能力可以用万用表

2012-04-26 17:06:32

等同hFE,甚至相差很大,所以不要将其混淆。β和hFE大小除了与晶体管结构和工艺等有关外,还与管子的工作电流(直流偏置)有关,工作电流IC在正常情况下改变时,β和hFE也会有所变化;若工作电流变得过小或

2018-06-13 09:12:21

晶体管的主要参数有哪些?晶体管的开关电路是怎样的?

2021-06-07 06:25:09

本文为大家介绍“Si晶体管”(之所以前面加个Si,是因为还有其他的晶体管,例如SiC)。 虽然统称为“Si晶体管”,但根据制造工艺和结构,还可分为“双极”、“MOSFET”等种类。另外,还可根据处理

2020-06-09 07:34:33

本篇开始将为大家介绍“Si晶体管”。虽然统称为“Si晶体管”,不过根据制造工艺和结构,还可分为“双极”、“MOSFET”等种类。另外,还可根据处理的电流、电压和应用进行分类。下面以“功率元器件”为主

2018-11-28 14:29:28

是自来水的阀门,发射极是配管,集电极是水龙头。用自来水的构造来举例说明晶体管的作用。把晶体管的3个引脚-基极、集电极和发射极分别视作自来水的阀门、水龙头和配管。通过微小之力(即基极的输入信号)来控制

2019-05-05 00:52:40

1.晶体管的结构晶体管内部由两PN结构成,其三个电极分别为集电极(用字母C或c表示),基极(用字母B或b表示)和发射极(用字母E或e表示)。如图5-4所示,晶体管的两个PN结分别称为集电结(C、B极

2013-08-17 14:24:32

晶体管管芯的工艺流程?光刻的工艺流程?pcb制版工艺流程?薄膜制备工艺流程?求大佬解答

2019-05-26 21:16:27

国内的通富微电成为AMD 7nm芯片的封测厂商之一

2020-12-30 07:48:47

技(Synopsys, Inc., 纳斯达克股票市场代码: SNPS)近日宣布,在设计人员的推动下,Fusion Design Platform™已实现重大7nm工艺里程碑,第一年流片数突破100,不仅

2020-10-22 09:40:08

XX nm制造工艺是什么概念?为什么说7nm是物理极限?

2021-10-20 07:15:43

工作电压的极性而可分为NPN型或PNP型。双极结型晶体管 双极结型晶体管(Bipolar Junction Transistor—BJT)又称为半导体三极管,它是通过一定的工艺将两个PN结结

2010-08-13 11:36:51

multisim仿真中高频晶体管BFG35能用哪个晶体管来代替,MFR151管子能用哪个来代替?或是谁有这两个高频管子的原件库?求大神指教

2016-10-26 11:51:18

NAND产品已实现商用并出货。“英特尔遵循摩尔定律,持续向前推进制程工艺,每一代都会带来更强的功能和性能、更高的能效、更低的晶体管成本,”英特尔公司执行副总裁兼制造、运营与销售集团总裁Stacy

2017-09-22 11:08:53

的晶体管制程从14nm缩减到了1nm。那么,为何说7nm就是硅材料芯片的物理极限,碳纳米管复合材料又是怎么一回事呢?面对美国的技术突破,中国应该怎么做呢?XX nm制造工艺是什么概念?芯片的制造...

2021-07-28 07:55:25

互补晶体管的匹配

2019-10-30 09:02:03

调制和振荡器。晶体管可以独立封装,也可以封装在非常小的区域内,容纳1亿个或更多晶体管集成电路的一部分。(英特尔 3D 晶体管技术)严格来说,晶体管是指基于半导体材料的所有单一元件,包括由各种半导体材料

2023-02-03 09:36:05

相当高的总电流增益。输出晶体管的最大集电极电流决定了输出晶体管对的最大集电极电流,可以是 100 安培或更高。需要的物理空间更少,因为晶体管通常封装在一个器件中。另一个优点是整个电路可以具有非常高

2023-02-16 18:19:11

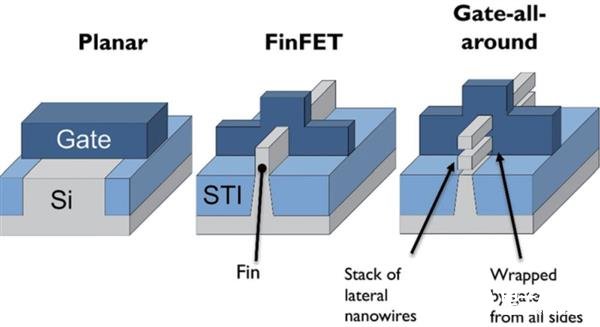

场效应管的演变 鳍式场效应晶体管的未来发展前景 FinFET在5nm之后将不再有用,因为它没有足够的静电控制,需要晶体管的新架构。然而,随着技术节点的进步,一些公司可能会出于经济原因决定在同一节点上

2023-02-24 15:25:29

450 万个门、包含数十亿个晶体管的时钟电路上;跟踪需要 4.5 小时,仿真总共需要 12 小时,在 250 个 CPU 上运行。总结设计 7nm 和更小工艺节点的 SoC 是一项艰巨的任务,需要专业的时钟分析知识以确保首次通过硅片成功。原作者:EETOP编译整理

2022-11-04 11:08:00

从7nm到5nm,半导体制程芯片的制造工艺常常用XXnm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工艺。所谓的XXnm指的是集成电路的MOSFET晶体管栅极

2021-07-29 07:19:33

来源:wikichip) 尽管EUV光刻机相当之贵,接近1.2亿美元一台,但半导体厂商还是愿意去投入,因为7nm以及以上的工艺的确需要EUV光刻机,几时同样的7nm工艺,使用EUV光刻技术之后晶体管

2020-07-07 14:22:55

nm晶圆厂进入生产状态。台积电的5nm制程分为N5及N5P两个版本。N5相较于当前的7nm制程N7版本在性能方面提升了15%、功耗降低了30%,晶体管密度提升了80%。N5P版本性能较N5提升7

2020-03-09 10:13:54

各位高手,小弟正在学习单结晶体管,按照网上的电路图做的关于单结晶体管的仿真,大多数都不成功,请问谁有成功的单结晶体管的仿真仿真啊,可以分享下吗。

2016-03-04 09:15:06

。对于NPN,它是灌电流。 达林顿晶体管开关 这涉及使用多个开关晶体管,因为有时单个双极晶体管的直流增益太低而无法切换负载电压或电流。在配置中,一个小输入双极结型晶体管(BJT)晶体管参与打开和关闭

2023-02-20 16:35:09

来至网友的提问:如何选择分立晶体管?

2023-11-24 08:16:54

10月7日,沉寂已久的计算技术界迎来了一个大新闻。劳伦斯伯克利国家实验室的一个团队打破了物理极限,将现有最精尖的晶体管制程从14nm缩减到了1nm。晶体管的制程大小一直是计算技术进步的硬指标。晶体管

2016-10-08 09:25:15

晶体管的代表形状晶体管分类图:按照该分类,掌握其种类1. 按结构分类根据工作原理不同分类,分为双极晶体管和单极晶体管。双极晶体管双是指Bi(2个)、极是指Polar(极性)。双极晶体管,即流经构成

2019-05-05 01:31:57

求一份tsmc 7nm standard cell library求一份28nm或者40nm 的数字库

2021-06-25 06:39:25

我正在寻找零件号“PCAL6408ABSHP”中有关工艺节点和晶体管数量的信息。NXP 网站上是否有一个位置可以找到 NXP 部件号的此类信息?

2023-04-19 09:27:44

反对。TSMC以前曾有些模棱两可,推进了16 nm finFET半节点计划。而影响最大的是,NVIDIA CEO Jen-Hsun Huang公开质疑整个20 nm节点的经济可行性,他认为,每个晶体管

2014-09-01 17:26:49

10nm、7nm等到底是指什么?芯片工艺从目前的7nm升级到3nm后,到底有多大提升呢?

2021-06-18 06:43:04

如今随着芯片制程的不断提升,芯片中可以有100多亿个晶体管,如此之多的晶体管,究竟是如何安上去的呢? 这是一个Top-down View 的SEM照片,可以非常清晰的看见CPU内部的层状结构

2020-07-07 11:36:10

本帖最后由 eehome 于 2013-1-5 10:10 编辑

高清图详解英特尔最新22nm 3D晶体管

2012-08-05 21:48:28

高清图详解英特尔最新22nm_3D晶体管

2012-08-02 23:58:43

目前的GS464V升级到LA664,因此单核性能有较大提升,达到市场上主流设计。至于未来的工艺,龙芯表示目前公司针对7nm的工艺制程对不同厂家的工艺平台做评估,不过他们没有透露什么时候跟进7nm工艺

2023-03-13 09:52:27

北京时间3月22日晚间消息,Nvidia今日发布了首款基于下一代 Kepler图形架构的GPU(图形处理器)NVIDIA GeForce GTX 680(以下简称“GTX 680”)。

2012-03-23 08:29:03 793

793 为什么说7nm是物理极限?缩短晶体管栅极的长度可以使CPU集成更多的晶体管或者有效减少晶体管的面积和功耗,并削减CPU的硅片成本。不过这种做法也会使电子移动的距离缩短,容易导致晶体管内部电子自发通过

2016-10-10 16:49:39 5833

5833 其基于7nm工艺(图中的芯片面积很小)、集成新架构GPU核心(Ampere?),同时深度学习浮点运算性能继续爆发。

2018-04-12 13:19:00 2486

2486 ,第46届Cowen技术大会上,AMD技术总监Mark Papermaster再一次向外公布朝向7nm工艺技术的发展,他表示7nm技术将会在晶体管密度和功耗上提升巨大,他还透露称目前研发的7nm产品有三款,之后的产品都会应用7nm,下半年将会正式采样。 本文引用地址: AMD现阶段的12nm工艺

2018-07-06 10:33:00 826

826 在日前举行的Computex 2018发布会上,AMD有些出人意料地进行了高规格的产品发布,公开的产品包括下一代使用7nm工艺的VEGA GPU,以及使用7nm的Zen 2处理器。目前,7nm

2018-06-29 16:17:24 3902

3902 AMD Zen架构取得了空前成功,今年还优化为Zen+增强版,并有同样优化的12nm工艺辅助,而现在我们终于迎来了全新的第二代Zen 2架构,以及全新的7nm工艺加持。 AMD原计划采用

2018-11-29 15:35:02 186

186 AMD日前发布了全球首款采用7nm工艺核心的游戏卡Radeon VII,定位直指RTX 2080,将在2月7日解禁发售。该显卡制程工艺领先一代,晶体管密度提升100%,相同功耗下性能提升25%;同样频率下功耗降低50%。

2019-02-11 11:53:23 2862

2862 通过使用三星7nm EUV工艺代替台积电的7nm工艺,Nvidia可能能够获得更多供应。

2019-06-10 09:06:12 6225

6225 随着AMD发布7nm Navi架构的RX 5700系列显卡,NVIDIA今年也要面临Intel一样的竞争压力了,那就是AMD在游戏卡、数据中心市场上有抢市场的资本了。

2019-06-13 15:44:15 852

852 7nm工艺计划2021年推出,相比10nm工艺晶体管密度翻倍,每瓦性能提升20%,设计复杂度降低了4倍。

2019-07-19 10:49:36 2832

2832 从16nm Pascal到12nm Turing,NVIDIA最近两代的GPU一直停留在16/12nm节点上,对最新的7nm工艺似乎没啥兴趣,反正友商从14nm到7nm工艺的显卡都打不过NVIDIA显卡,老黄确实不着急。

2019-11-09 10:06:50 2490

2490 在SC 19超算大会上,Intel正式宣布了他们为高性能计算打造的Xe架构GPU——Ponte Vecchio(维琪奥桥),同时它也会首发Intel的7nm工艺,2021年会用于Intel花了50亿美元给美国国防部建造的Aurora极光超算上。

2019-11-21 09:48:42 3017

3017 尽管AMD已经推出了7nm工艺、RDNA架构的新一代Navi家族显卡,但是NVIDIA在高端GPU市场上的地位依然无可动摇,12nm工艺的图灵Turing显卡在性能及能效上还是占据上风。

2019-12-10 10:44:13 1863

1863 目前全球最先进的半导体工艺已经进入 7nm,下一步还要进入 5nm、3nm 节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。

2019-12-10 15:40:49 7155

7155 随着AMD的全新7nm制程工艺的RDNA架构推出,代表着AMD在未来的GPU市场上将有一番大作为,在过去的几代中,AMD的GPU已经利用了很久的基于GCN架构的计算单元。

2019-12-10 17:06:40 2957

2957 2020年的NVIDIA GTC大会将在3月22到26日举行,届时NVIDIA发布新一代Ampere安培架构的GPU应该没跑了,要知道GTC大会上已经有两三年没发布真正的新一代GPU了,等的黄花菜都凉了。

2020-01-04 10:13:24 2955

2955 本次CES展会上,NVIDIA除了推出360Hz超高刷新率的电竞显示器之外就非常低调了,并没有什么重磅新品发布或者技术展示,7nm安培GPU估计要留给自家的GTC大会了。

2020-01-08 09:37:27 2241

2241 根据消息,英伟达将在2020年3月的GTC大会期间宣布其安培显卡,目前所有证据都表明安培显卡将采用7nm工艺生产。

2020-01-13 15:01:25 2432

2432 NVIDIA的下一代GPU“安培”(Ampere)大概是近年来保密性最好的了,迄今为止实锤爆料都不多,就连发布时间都不确定,3月份GTC大会上即便正式宣布,也可能只是面向数据中心的GA100大核心。

2020-02-28 17:20:05 2761

2761

在工艺制程方面,台积电的进度明显要快于英特尔。其实在2017年的时候,英特尔就指出台积电7nm并非真实的7nm。而且英特尔呼吁行业应该统一命名标准,防止命名混乱。英特尔更希望以晶体管密度作为衡量标准。

2020-03-01 08:13:00 3014

3014 Intel之前已经宣布在2021年推出7nm工艺,首发产品是数据中心使用的Ponte Vecchio加速卡。7nm之后的5nm工艺更加重要了,因为Intel在这个节点会放弃FinFET晶体管转向GAA晶体管。

2020-03-11 09:51:09 5687

5687

3月底的GTC大会上已经改成只发新闻稿了,最大的悬念就是会不会有7nm安培(Ampere)GPU了。

2020-03-12 11:44:07 1776

1776

根据外媒WCCFTECH的报道,爆料消息称英伟达的下一代GPU架构将基于三星10nm制程,而不是之前报道的台积电7nm工艺,据称使用的10nm制程更接近于三星提供的8LPP技术,另外新的Tegra芯片也将使用相同的制程。

2020-03-12 16:28:46 2670

2670 如果没有疫情危机肆虐,再过几天我们可能就要看到NVIDIA正式宣布下一代GPU“安培”(ampere)了,结果GTC大会从线下大会改成线上发布,再到发新闻,最后又叫停新闻发布了。

2020-03-19 10:42:33 1530

1530 随着GTC 2020大会事实上的取消,NVIDIA今年3月份发布下一代安培“Ampere”显卡的可能性基本没了。在这个问题上,NVIDIA倒也不着急,高级副总Jeff Fisher表示他们的GPU架构领先对手2年多。

2020-03-26 08:55:42 746

746 随着GTC 2020大会事实上的取消,NVIDIA今年3月份发布下一代安培“Ampere”显卡的可能性基本没了。在这个问题上,NVIDIA倒也不着急,高级副总Jeff Fisher表示他们的GPU架构领先对手2年多。

2020-03-26 14:58:13 2406

2406 随着GTC 2020大会事实上的取消,NVIDIA今年3月份发布下一代安培“Ampere”显卡的可能性基本没了。在这个问题上,NVIDIA倒也不着急,高级副总Jeff Fisher表示他们的GPU架构领先对手2年多。

2020-03-26 15:54:59 2001

2001 据国外媒体报道,图形处理器厂商英伟达周四推出了他们首款基于安培架构的GPU英伟达A100,采用7nm工艺制造,集成超过540亿个晶体管。

2020-05-15 10:33:42 1698

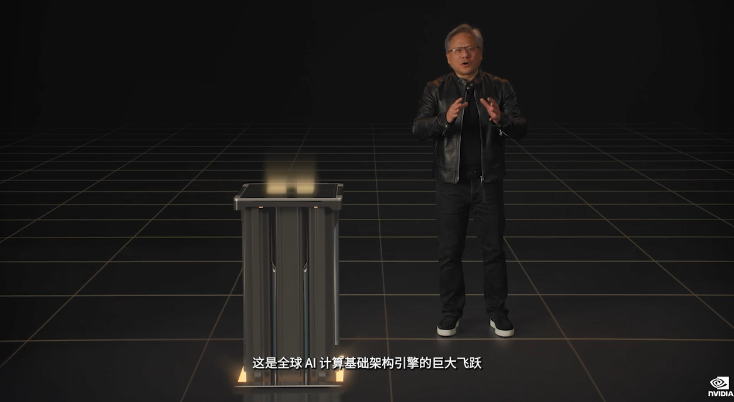

1698 突如其来的新冠肺炎大流行打乱了众多公司的产品发布计划,比如本该在今年3月英伟达(NVIDIA)GTC 2020上发布的安培(Ampere)架构曝光多次却一直未发布。今天,英伟达CEO黄仁勋发布了英伟

2020-05-15 14:48:00 7763

7763 在5月14日的GTC演讲中,NVIDIA CEO黄仁勋正式宣布了新一代GPU——Ampere安培,它使用了7nm工艺,号称性能是上代Voltra的20倍。日前NVIDIA CFO Colette Kress表示这是他们三年来的杰作,是NVDIA有史以来最强大的GPU。

2020-06-05 11:42:19 3058

3058 去年AMD推出了7nm Zen2架构的锐龙、霄龙处理器,这是首款7nm工艺的x86处理器。不过严格来说它是7nm+14nm混合,现在AMD要加速甩掉14nm工艺了,IO核心也有望使用台积电7nm工艺。

2020-09-24 10:12:58 1765

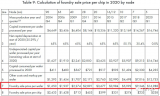

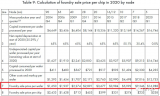

1765 与Nvidia P100 GPU(610m㎡,907亿个晶体管,强度为148.2 MTr/m㎡)相当。 从上表可以看到,5nm晶圆单片的代工销售价约是16988美元,对比7nm,涨幅超80%。而对于使用16nm

2020-10-10 17:57:07 3618

3618

NVIDIA Ampere安培家族首次使用了两种制造工艺,面向数据中心、深度学习的A100是台积电7nm,面向游戏的RTX 30系列则是三星8nm。

2020-11-06 09:35:59 1217

1217 了。 NVIDIA今年3月份发布了安培架构的A100加速卡(名字中没有Tesla了),升级了7nm工艺和Ampere安培架构,集成542亿晶体管,826mm2核心面积,使用了40GB HBM2显存,带宽1.6TB

2020-11-17 10:15:41 2041

2041 3月份发布了安培架构的A100加速卡(名字中没有Tesla了),升级了7nm工艺和Ampere安培架构,集成542亿晶体管,826mm2核心面积,使用了40GB HBM2显存,带宽1.6TB

2020-11-17 15:38:58 1740

1740 图灵(Turing)和安培(Ampere)之后,很早就有爆料NVIDIA的下一代GPU将以“Hopper(赫柏)”知名,Hopper被誉为编译之母,是伟大的女性程序员。

2020-12-22 10:33:48 1461

1461 NVIDIA发布新一代产品—NVIDIA H100,H100是一款超大的芯片,采用TSMC 4N工艺,具有800亿个晶体管,也是首款采用HBM3标准的GPU。

2022-03-23 17:21:42 2476

2476

5月24日,在全球科技盛会“Computex 2022”期间,NVIDIA正式推出A100 80GB PCIe液冷式GPU。作为NVIDIA的重要合作伙伴,紫光股份旗下新华三集团H3C

2022-05-25 10:34:58 1344

1344 全球首颗2nm芯片已经被IBM研制出来了,在这一颗指甲盖大小面积的芯片上可以容纳500亿颗晶体管,芯片制程工艺的进步必将让半导体行业的发展越来越快。接下来我们详细了解下这款2nm芯片的特性、功耗等,跟7nm芯片做个对比,看下2nm芯片与7nm芯片之间有何差距。

2022-06-22 09:52:43 4352

4352 有多大呢?是2nm吗? 其实芯片前面的数字代表的是这款芯片所采用的制程工艺,2nm即为2nm制程工艺,而制程工艺又特指芯片内部晶体管的栅极最小长度,栅极是晶体管内用于控制电流的结构,因此2nm即代表着芯片内部晶体管最小栅极长度为2nm,并不是代表整

2022-07-04 09:15:36 3936

3936 在芯片设计和制造中,纳米表示的是芯片中晶体管与晶体管之间的距离,在体积相同大小的情况下,7nm工艺的芯片容纳的晶体管的数量,几乎是14nm工艺芯片的2倍。

2022-07-06 16:53:46 21550

21550 半导体芯情了解到,A100是英伟达最新推出的一款高性能计算芯片,采用了全新的Ampere架构,Ampere架构是NVIDIA于 GTC 2020发布的GPU架构,NVIDIA Ampere 由540亿晶体管组成,是7nm芯片。

2023-11-14 16:30:16 561

561

电子发烧友App

电子发烧友App

评论