语音识别技术的发展 与机器进行语音交流,让它听明白你在说什么。语音识别技术将人类这一曾经的梦想变成了现实。语音识别就好比机器的听觉系统,该技术让机器通过识别和理解,把语音信号转变为相应的文本或命令

2018-01-06 07:48:00 20997

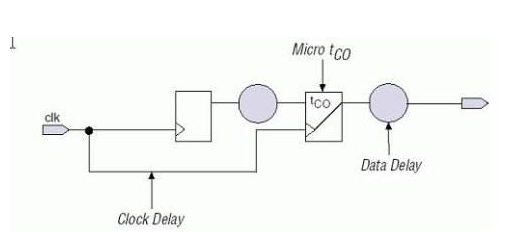

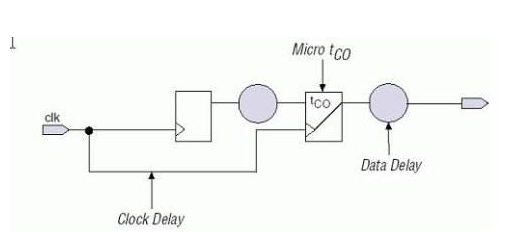

20997 时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6212

6212

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1229

1229 FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

2023-08-14 17:49:55 711

711

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

此版只讨论时序约束约束理论约束方法约束结果时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II

2013-05-16 18:51:50

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

vivado默认计算所有时钟之间的路径,通过set_clock_groups命令可禁止在所标识的时钟组之间以及一个时钟组内的时钟进行时序分析。 1.异步时钟组约束声明两时钟组之间为异步关系,之间不进行时序

2018-09-21 12:40:56

在进行数字电路系统的设计时,时序是否能够满足要求直接影响着电路的功能和性能。本文首先讲解了时序分析中重要的概念,并将这些概念同数字系统的性能联系起来,最后结合FPGA的设计指出时序约束的内容和时序

2020-08-16 07:25:02

好的时序是设计出来的,不是约束出来的时序就是一种关系,这种关系的基本概念有哪些?这种关系需要约束吗?各自的详细情况有哪些?约束的方法有哪些?这些约束可分为几大类?这种关系仅仅通过约束来维持吗?1

2018-08-01 16:45:40

爆款资料推荐ADI《模拟对话》技术期刊,第1期至第50期都在这里了https://ezchina.analog.com/thread/14417ADI系统方案精选合集(2016)https

2016-10-28 18:04:57

DAYU200资料需求集中讨论贴,有需要什么资料都在这里提~我们会统计,并整理输出给到大家~

2022-03-04 12:32:03

电子发烧友网ETD第14期SDR源同步接口时序约束方法-会前交流电子发烧友网ETD第14期SDR源同步接口时序约束方法-演讲电子发烧友网ETD第14期SDR源同步接口时序约束方法-提问

2015-01-17 16:27:32

Incremental Compilation。这是造成上述两种方法容易混淆的原因。5. 核心频率约束+时序例外约束+I/O约束+寄存器布局约束 寄存器布局约束是精确到寄存器或LE一级的细粒度布局约束。设计者

2017-12-27 09:15:17

控。从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下:0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括

2016-06-02 15:54:04

的方法一般有四个步骤:时序分析→时序约束→时序报告→时序收敛。

为什么要进行时序分析?

信号在系统中传输时由于经过一些逻辑器件和PCB上的走线会造成一定的逻辑延时和路径延时,如果系统要求信号

2011-09-23 10:26:01

,FPGA产生的数据data_out和时钟clk_out的理想波形是时钟上升沿锁存到稳定可靠的数据。(特权同学,版权所有)图8.26 源同步接口寄存器和时序波形关系下面我们来探讨如何对这个设计进行约束。首先

2015-07-30 22:07:42

的工程师朋友们...在互动环节工程师们积极提问并获得电子发烧友赠送的技术书籍最后来一张全家福大合照,在这里没有新老工程师之分,大家都是FPGA的爱好者,也都是爱学习爱充电的人士,最后祝贺我们本次沙龙圆满结束

2014-12-31 14:25:41

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-09-21 07:45:57

,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约束以满足设计要求。因为时钟周期是预先知道的,而触发器之间的延时是未知的(两个触发器之间的延时等于一个时钟周期),所以得通过约束来控制触发器之间的延时。当延时小于一个时钟周期的时候,设计的逻辑才能稳定工作,反之,代码会跑飞。

2018-08-29 09:34:47

有没有哪位大神对ISE的时序约束比较熟悉,尤其是多周期约束这一块。在Quartus中使用比较简单,而且相关资料也比较多,但是ISE中的资料好像不是那么多,而且也没有针对具体例子进行分析。官网上给出

2015-04-30 09:52:05

正在进行着一种经营,一种为合作伙伴创造利益的经营。因为在这里,您得到的是第一手信息,也许您此刻正在结合这些信息,运筹您的宏图伟业。那就请您登陆我们的网站,我们会以最快的速度,在最短的时间内把您所需要的无限商机送给您。

2009-06-14 22:37:08

请教大牛,在用quartus II 9.1时进行时序约束时一按闹钟按钮打开time quest界面时程序就卡死了,不知道哪里出问题了,请教大牛应该怎莫办才好

2019-03-06 06:35:15

进行时序分析,例如:1.如何检查输入或输出的时间?2.如何检查源时钟和目标时钟的某些路径是否为特定时钟?如果有人可以在这里发布你总是使用的常用命令,或者推荐一些教程,那就太棒了。提前致谢。以上

2019-03-11 13:41:27

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

控。 下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下: 0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括FalsePath

2017-10-20 13:26:35

求助啊!!!我在这里下的好的文件都有损坏的现象,无论是zip还是pdf,都打不开,而且一般都显示文件很小,只有1M多?这是为什么?

2012-03-30 22:39:23

求助啊!!!我在这里下的好的文件都有损坏的现象,无论是zip还是pdf,都打不开,而且一般都显示文件很小,只有1M多?这是为什么?

2012-03-30 22:42:23

你们想要的全景影像系统开发资料,都在这里啦![hide][/hide]

2017-03-17 14:08:17

`你要的自供电技术都在这里扫一扫吧[qq]1098104553[/qq]`

2016-12-08 17:52:15

最高频露。下面说一下在ise环境下进行时序约束的方法。 通过约束编辑器的文本编辑窗口,可以采用以下两种方式的UCF语句来做时钟约束。 (1)period_item PERIOD=period{HIGH

2015-02-03 14:13:04

系统设计教程》(第三版)。在这一阶段,你要做到的是:给你一个指标要求或者时序图,你能用HDL设计电路去实现它。这里你需要一块开发板,可以选Altera的cyclone IV系列,或者Xilinx

2020-10-21 15:07:39

关于电容的一些基础知识都在这里

2021-04-23 07:12:10

关于高速ADC的选择与应用你想要的都在这里

2021-05-25 06:57:38

逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(Tskew)、建立时间(Tsu)、保持时间(Th)等

2018-04-03 11:19:08

学习中遇到问题可以在这里发帖请教吗?会不会有及时准确的答案?因为有的问题还比较难描述,不方便用百度搜索。大家遇到问题怎么处理?

2014-09-25 20:57:47

问一下啊,在写时序约束的时候,如何根据设计的要求进行时序上的约束啊,看了好多网上的资料,说的都是有关约束的一些原理。有没有那位大侠给个设计实例啊!

2023-04-23 11:42:16

本帖最后由 亿道集团 于 2019-4-24 12:54 编辑

小伙伴,教你如何合并License,赶紧收藏哦!

2016-12-28 15:56:21

本帖最后由 仪商城客服 于 2017-12-6 11:07 编辑

仪商导读:谐波干扰是电源运行过程中常见的现象,工程师往往需要不断的升级PFC电路来改进自家的电源产品,那么,怎样定位电源运行时

2017-12-06 11:04:03

清华出品:最易懂的AI芯片报告!人才技术趋势都在这里 https://mp.weixin.qq.com/s/kDZFtvYYLLqJSED_0V1RZA 2010 年以来, 由于大数据产业的发展

2021-07-23 09:19:56

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

大家好,这个电感在这里是滤波吗?如果是,那么可以放在7805后面滤波吗

2019-03-05 20:13:46

难得看到一篇好的PCB布局文章,赶紧收藏

2015-04-03 18:27:39

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 Xilinx时序约束设计,有需要的下来看看

2016-05-10 11:24:33 18

18 每次iOS系统更新前都会有一大推发烧友爆料新系统的特点,在这里将 iOS 10.3可能出现的新功能进行了汇总:

2017-02-06 14:04:47 2441

2441 偏移约束。 这里先说一下周期约束:周期约束是为了达到同步组件的时序要求。如果相邻同步原件相位相反,那么延迟就会是时钟约束值的一半,一般不要同时使用上升沿和下降沿。注意:在实际工程中,附加的约束时间为期望值的

2017-02-09 02:56:06 605

605 三星Galaxy S8/S8+国行版将于今晚8点整在北京正式发布,三星S8发布会直播进行时,现在有二十万人在看同步直播。你想知道的配置、价格、真机,都在这里!

2017-05-18 20:29:18 907

907 关于新能源汽车与自动驾驶,你想知道的都在这里。

2017-08-02 09:57:33 2444

2444 作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此

2017-11-17 05:23:01 2416

2416

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

详细讲解了xilinx的时序约束实现方法和意义。包括:初级时钟,衍生时钟,异步时终域,多时终周期的讲解

2018-01-25 09:53:12 6

6 最详细的电气基础知识都在这里。

2018-03-28 16:03:20 27344

27344

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 14208

14208

好的时序是设计出来的,不是约束出来的 时序就是一种关系,这种关系的基本概念有哪些? 这种关系需要约束吗? 各自的详细情况有哪些? 约束的方法有哪些? 这些约束可分为几大类? 这种关系仅仅通过约束

2018-08-06 15:08:02 400

400 从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下:

2018-08-07 14:14:00 13907

13907

了解时序约束向导如何用于“完全”约束您的设计。

该向导遵循UltraFast设计方法,定义您的时钟,时钟交互,最后是您的输入和输出约束。

2018-11-29 06:47:00 2698

2698

,这让我真真感觉是捡到宝了!独乐乐不如众乐乐,我觉得有必要和大家推广一下,让大家也享受一下能躺在家里赚钱的快感!今天的主角:聚游公社!顾名思义,这是一个汇集了很多游戏的一站式体验社区!在这里,你能玩到你能想象

2018-12-20 17:58:00 228

228 MLCC缺货,能用钽电容替代吗?最靠谱儿的回答在这里~

2019-07-02 11:40:48 3698

3698 浦东新区将建成一批新一代人工智能产业创新应用“试验场”,更多人工智能创新产品、平台和服务将在这里先行先试。

2019-07-18 16:39:54 415

415 关于5G手机,你想知道的都在这里了,快收藏

2019-08-27 16:25:46 2315

2315 首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 3077

3077

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

2021-01-11 17:44:44 8

8 噪声可以是随机信号或重复信号,内部或外部产生,电压或电流形式带或宽带,高频或低频。(在这里,我们将噪声定义为任何在运放输出端的无用信号)

噪声通常包括器件的固有噪声和外部噪声,固有噪声包括:热噪声

2021-02-03 07:21:35 31

31 电子发烧友网为你提供详解直线电机,你要知道的都在这里资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-07 08:41:51 18

18 电子发烧友网为你提供一张思维导图介绍PCB散热,你需要了解的都在这里资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-29 08:41:04 33

33 时序冲突的概率变大以及电路的稳定性降低,为此必须进行时序、面积和负载等多方面的约束。

2021-06-15 11:24:05 2874

2874

7大主流单片机优缺点分析,一文打尽赶紧收藏!

2021-11-15 13:21:03 13

13 上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

很多读者对于怎么进行约束,约束的步骤过程有哪些等,不是很清楚。明德扬根据以往项目的经验,把时序约束的步骤,概括分成四大步

2022-07-02 10:56:45 4974

4974

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息

2022-12-28 15:18:38 1891

1891 本章节主要介绍一些简单的时序约束的概念。

2023-03-31 16:37:57 928

928

很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间

2023-05-29 10:06:56 372

372

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 1260

1260

您对于储能连接器的生产流程了解多少,下面我们一同来认识一下储能连接器生产流程。“储能连接器生产流程都在这里了”由仁昊连接器为您整理,采购连接器,上仁昊。

2022-01-06 14:02:42 1221

1221

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

很多小伙伴开始学习时序约束的时候第一个疑惑就是标题,有的人可能会疑惑很久。不明白时序约束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 828

828

本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 692

692 本小节对时序约束做最终的总结

2023-07-11 17:18:57 351

351

本文继续讲解时序约束的第四大步骤——时序例外

2023-07-11 17:17:37 417

417

一、概述在上一篇杂谈文章《[HPM杂谈]你想要了解的先楫hpm_sdk开发都在这里系列(一)》,大概分析了先楫通用单片机开发与其他国产单片机的开发差异,以及开发优劣势。刚好在这个月底,先楫官方发布

2023-10-12 08:18:09 826

826

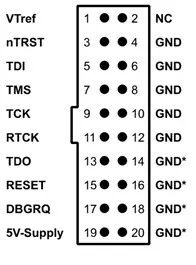

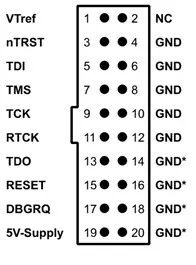

J-Link 中的JTAG 接口:正确使用需要了解的注意事项,在这里!

2023-12-01 16:01:57 560

560

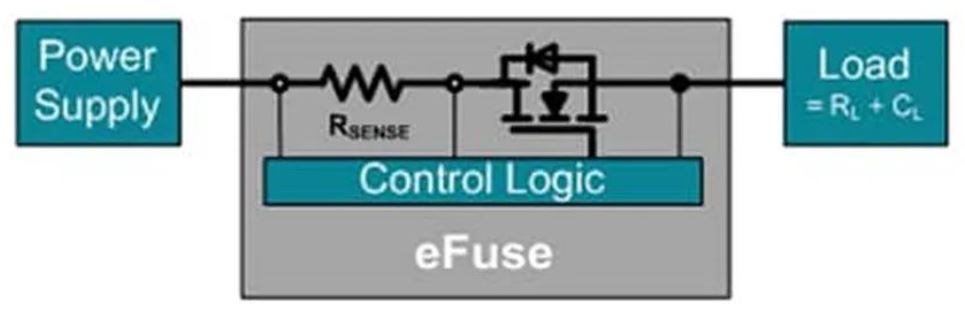

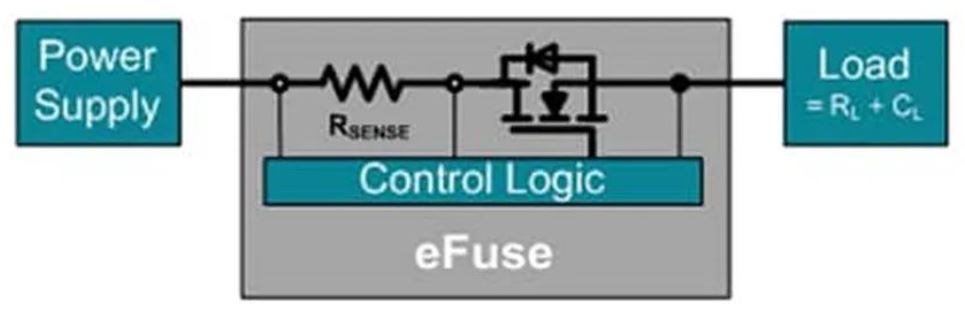

有关eFuse电子保险丝,你应该了解的技术干货,都在这里!

2023-12-04 10:20:13 639

639

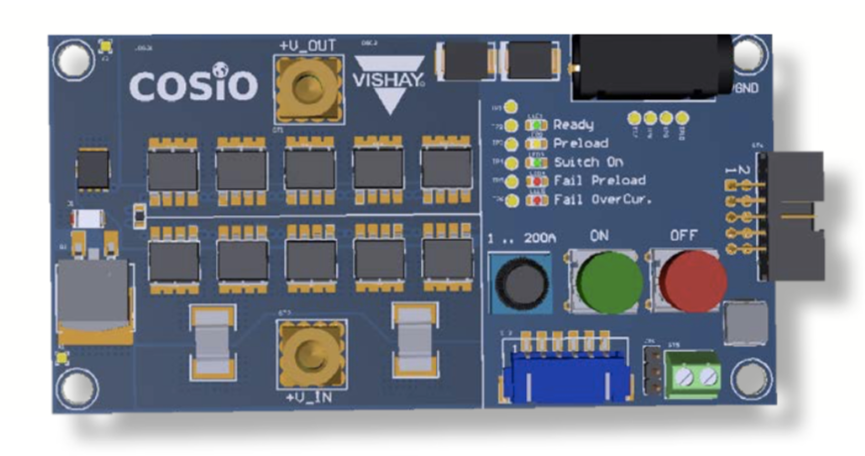

48V电源系统可恢复eFuse的设计秘诀,在这里!

2023-12-05 10:09:25 317

317

电子发烧友App

电子发烧友App

评论