。 Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。 本部分的学习

2020-12-25 14:11:50 6843

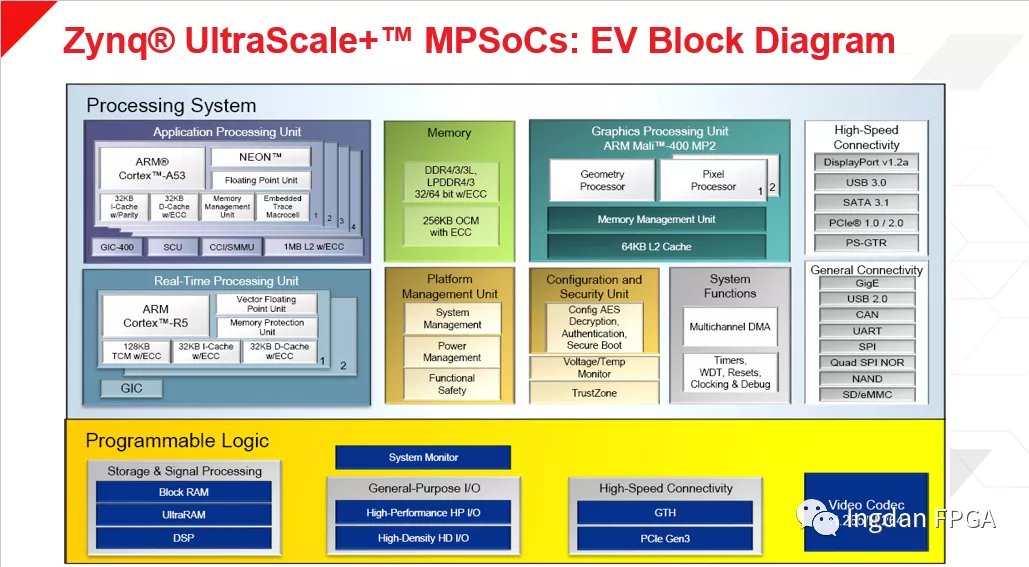

6843 本篇主要介绍ZU+系列MPSoC的外围接口,针对每个接口进行概述性介绍,后续会针对个别接口进行详细介绍原理图设计和PCB设计。 ZU+系列MPSoC的外围接口主要包括两部分:PL部分和PS部分。PL

2020-12-26 10:04:38 4310

4310

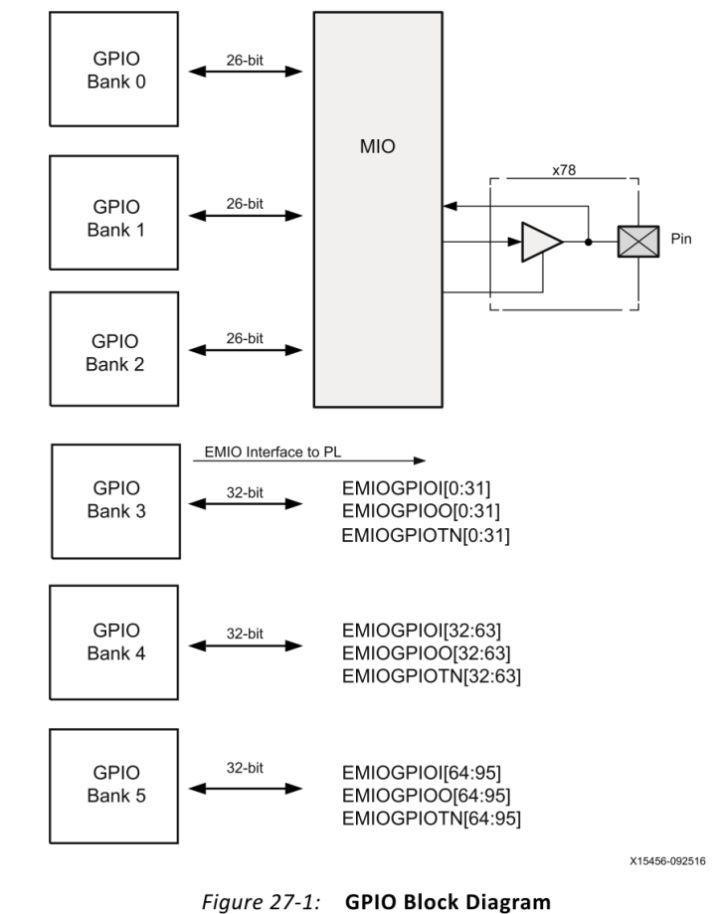

;AXI_GPIO是封装好的IP核,PS通过M_AXI_GPIO接口控制PL部分实现IO,使用时消耗管脚资源和逻辑资源。 使用的板子是zc702。 1.MIO方式 Zynq7000 系列芯片有 54

2020-12-26 10:12:57 3306

3306

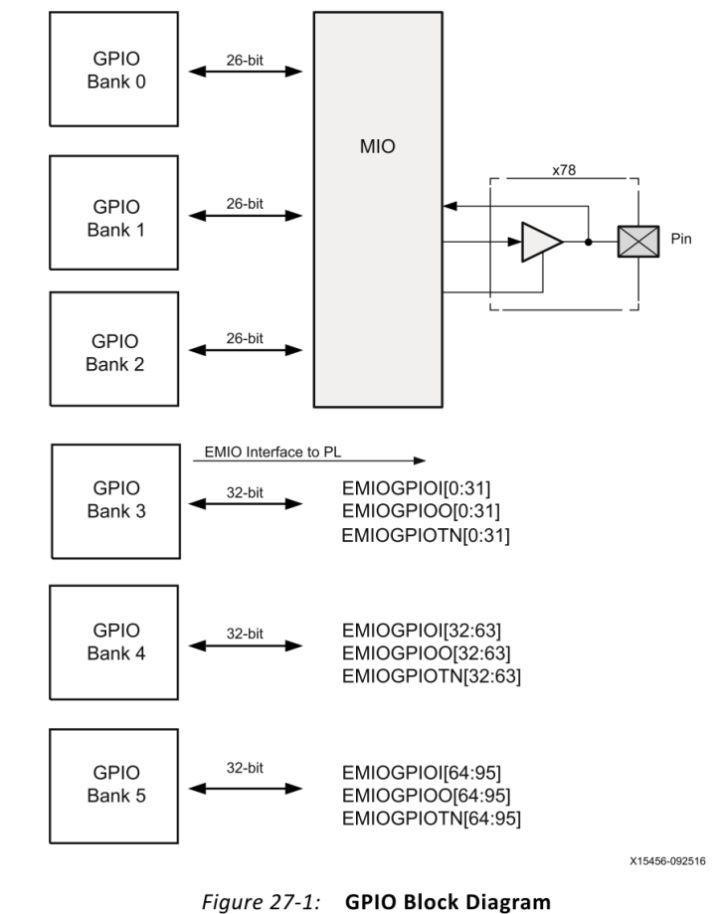

如果想用PS点亮PL的LED灯,该如何做呢?一是可以通过EMIO控制PL端LED灯,二是通过AXI GPIO的IP实现控制。本章介绍如何使用EMIO控制PL端LED灯的亮灭。同时也介绍了,利用EMIO连接PL端按键控制PL端LED灯。

2021-01-30 10:05:00 6730

6730

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00 12917

12917

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

2021-02-22 13:51:00 7359

7359

/p/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 13958

13958

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 2880

2880

xilinx mpsoc 平台中,PS 和 PL 进行交互时,PS 需要获取 PL 发出的中断信号。从 mpsoc 技术参考手册 ug1085 TRM 中可知,PL 给到 PS 的中断有两组

2023-08-24 16:06:22 560

560

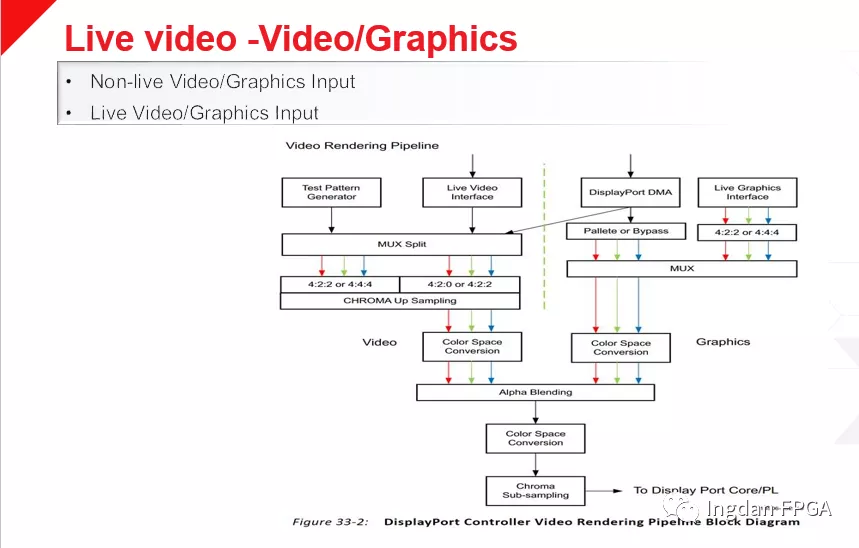

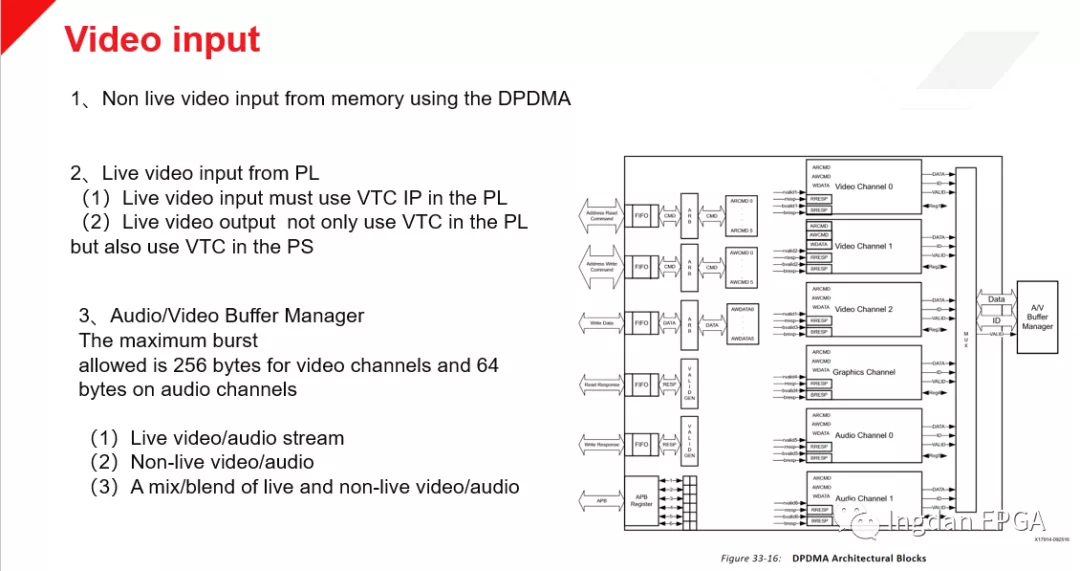

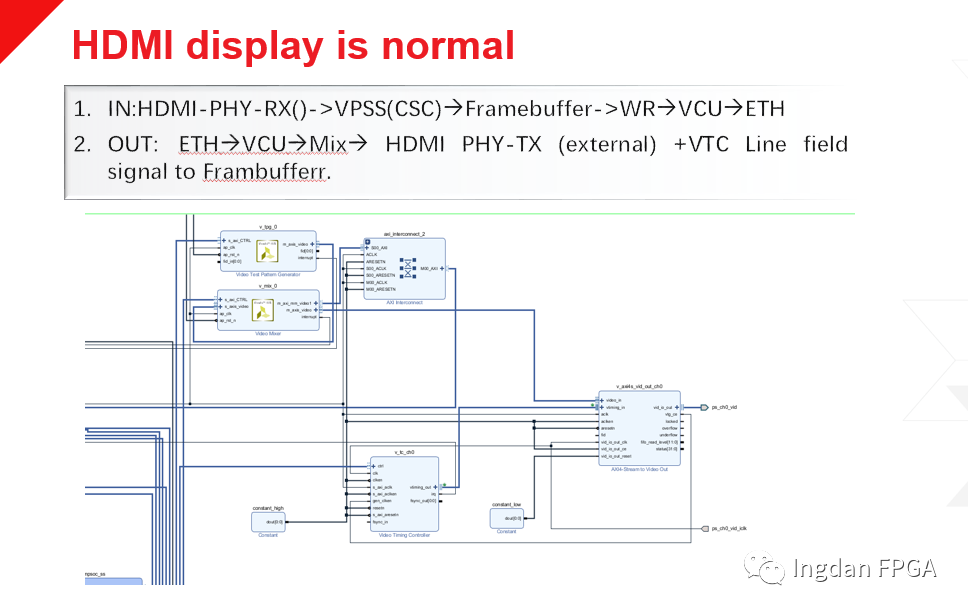

10-100-1000 Mbps Ethernet (RGMII) 网络接口PS端QSPI flash 存储PS端 SD卡,Emmc存储PL端64bit 2GB 容量DDR3 存储PL端扩展HDMI 输出实现视频显示

2021-07-09 17:14:21

PS176是一个显示端口 (DP)至HDMI 2.0视频接口转换器适用于需要视频协议转换的电缆适配器、电视接收器、监视器和其他应用。它将接受任何显示端口输入格式,包括DP 1.1a、dp

2022-05-18 10:31:07

ZYNQ进阶之路9--PS端实现FreeRTOS嵌入式系统导论FreeRTOS简介实现步骤导论在之前的章节中我们我们完成了PS端、PL端和PS+PL的一些工程,本章节我们插入一个小插曲,讲解

2021-12-22 08:29:20

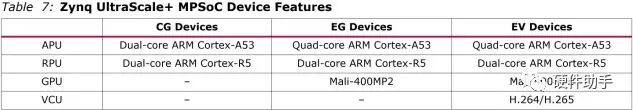

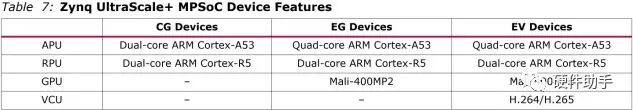

Cortex-A53 + 双核ARM Cortex-R5) + PL端UltraScale+架构可编程逻辑资源,支持4K@60fps H.264/H.265视频硬件编解码,并支持SATA大容量存储接口,评估板由

2023-06-21 15:38:10

,Video Format配置为Mono/Sensor,Pixels Per Clock配置为1,色彩数据位宽为8bit。4.2 AXI VDMA IP核本案例使用AXI VDMA IP核进行视频数据缓存

2021-05-24 11:12:40

到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。 PS与PL内部通信(用户自定义IP)先要自定义一个AXI-Lite

2018-01-08 15:44:39

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机

2021-05-28 14:28:28

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中

2020-12-23 17:06:35

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35

2021-01-08 16:44:20

;AXI-Stream 的转换,只不过是专门针对视频、图像等二维数据的。AXI-CDMA:这个是由 PL 完成的将数据从内存的一个位置搬移到另一个位置,无需 CPU 来插手。涉及到DMA主要包括AXI

2022-03-31 11:39:10

的存储器。

⑥ACP : PL端可以直接从PS的Cache中拿到CPU计算的结果,延时低

⑦DMA :DMA控制接口,用于控制高速数据传输的通道。

(3)AXI协议

AXI所采用的是一种READY

2023-11-03 10:51:39

使用XPS时,然后将.xmp导入planahead,生成一个比特流文件。我可以使用chipcope / impact进行配置,从PS-> PL运行获取FCLK还是我必须导出到sdk?我正在

2019-09-05 06:03:46

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

PS端QSPI flash 存储PS端 SD卡,Emmc存储PL端32bit 1GB 容量DDR3 存储PL端扩展HDMI 输出实现视频显示应用PL端扩展16路 I/O, 4个LED指示灯PL端扩展标准

2020-03-24 09:39:49

,硬件资源丰富。可通过PL端进行高速图像数据采集,并通过PS端进行业务逻辑控制,运用十分便捷。(2)视频接口丰富可拓展众多目标追踪场合常用的视频接口,如CameraLink、SDI、HDMI、PAL等

2021-05-19 17:10:50

FFT的核心算法,以及与PS部分的数据交换。

PS部分包含了以下的组件:

ARM Core:这是一个基于ARM架构的处理器核心,它运行着我在上一章节介绍的PYNQ系统。它可以通过AXI Lite接口

2023-10-02 22:03:13

由可编程逻辑中的HDMI IP控制。在官方的PYNQ框架中,HDMI IP连接到PS DRAM,视频数据流可以从HDMI传输到内存,也可以从内存流式传输到HDMI输出。可以使用Python对视频数据进行采集

2019-01-28 22:50:13

一直纠结于怎样给PL提供时钟,zynq开发不同于一般的FPGA开发。其中时钟和复位问题就是相当重要的问题,有两种方式可以为PL部分提供时钟和复位:1、PS部分可以产生四个毫无关系的输出时钟和复位信号

2015-06-08 17:29:32

本帖最后由 blackroot 于 2015-6-10 17:06 编辑

一直没搞懂PS怎样给PL提供复位和时钟,今天这个问题终于解决了~~~~~用一个简单的例子来说明一下,怎样使用PS输出

2015-06-10 16:59:53

个逻辑胶合者被PS指挥;当然上电和初始化顺序还是一样的,必须先启动配置完PS,才能初始化PL。首先我们在Vivado开发环境中建立RTL工程,并编写我们需要在PL中实现的功能代码HDL文件,把它做为

2015-06-01 11:54:12

总线的从接口,和AXI主接口实现互联,来对BRAM进行读写操作。针对不同的应用场合,该IP核支持单次传输和突发传输两种方式。14.2实验任务本章的实验任务是PS将串口接收到的数据写入BRAM,然后从

2020-09-04 11:08:46

CameraLink1接口输入的差分视频数据转化成并行视频数据。lvds_n_x_1to7_sdr_rx模块开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录

2021-04-19 15:26:53

道数据差分对为4组,需2个连接器。图 114.2lvds_n_x_1to7_sdr_rx模块本案例使用lvds_n_x_1to7_sdr_rx模块将CameraLink1接口输入的差分视频数据转化成

2021-04-22 09:14:50

道数据差分对为4组,需2个连接器。图 114.2lvds_n_x_1to7_sdr_rx模块本案例使用lvds_n_x_1to7_sdr_rx模块将CameraLink1接口输入的差分视频数据转化成并行

2021-04-27 09:40:41

XCZU7EV高性能处理器设计的高端异构多核SoC工业核心板,处理器集成PS端(四核ARM Cortex-A53 + 双核ARM Cortex-R5) + PL端UltraScale+架构可编程逻辑资源,支持

2023-06-21 15:27:45

1. 硬件介绍 由于开发板上只有DP可以显示,但却是PS端的,PL端没有HDMI的接口,因此我们采用AN9134的HDMI扩展模块实现HDMI显示。将24位RGB编码输出TMDS差分信

2021-01-15 16:49:10

和M_AXI_HPM0_LPD。 位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xilinx在Vivado开发环境里提供现成IP如AXI-DMA,AXI-GPIO

2021-01-07 17:11:26

LT8911 LT7211、普瑞PS8625、昆泰CH7511等方案,DP换LVDS转换主要是用在一些LVDS接口的液晶,将DP信号转出至LVDS屏输出,此时需要用DP TO LVDS这样一个转接板来实现屏显示

2021-08-02 20:00:42

错误。然后,我在SDK中编程PS端,led闪烁正确的频率!我的问题,当锁定Zynq PL时钟? PS程序之后?需要多长时间?是不是意味着,PL配置期间LED闪烁错误,在非易失性Flas Boot中编程PS期间(或之后)闪烁?谢谢的Berker

2020-08-27 15:09:19

我想给板子接上一个u***接口的键盘,不跑操作系统,只用ps部分接收键盘的数据然后传递给PL,不知道如何编写sdk的代码来跟u***的phy通信呢?有没可以参考的例程或者文档?

2015-12-16 17:12:38

(Processing System,PS)和可编程逻辑资源(Programmable Logic,PL)),提供了基于Zynq-7010/7020的多路千兆网口实现方案。1 硬件平台TLZ7x-EasyEVM-S

2021-10-22 09:43:10

FPGA 外围的数据传输带宽以及存储器带宽。但是在 FPGA 内部,可编程逻辑部分随着工艺提升而不断进步的同时,内外部数据交换性能的提升并没有那么明显,所以 FPGA 内部数据的交换越来越成为数据传输的瓶颈

2020-09-07 15:25:33

随着USB C接口的普及,越来越多的笔记本只保留了USB C接口来传输视频信号,而显示端依旧是HDMI的天下。因此,许多需要扩展显示的场景必须配备一个USB C to HDMI的适配器来实现。如会议

2019-09-23 09:05:04

实例的内容及目标1.实例的主要内容本实例通过Verilog编程实现在红色飓风II代Xilinx开发板上面实现对键盘、LCD、RS-232等接口或者器件进行控制,将有键盘输入的数据在LCD上面

2019-06-03 05:00:03

如何实现labview跟电脑的数据交换,不用硬件

2015-11-18 13:35:46

文件的PL,然后给每个人提供刺激来测试设计,PS将从PL回读一些输出,在结束我将结果数据发送回用户。换句话说,它是一种“设计测试”服务。(1)我有什么方法可以达到这个目标吗?似乎唯一的“cat

2020-05-21 07:07:50

我的设备是zedboard702,我知道如何在使用PS和PL时使用SDK生成启动映像和程序闪存。问题是我只是使用PL,现在如何编程flash?

2019-09-30 09:43:18

亲爱的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址转换(映射方案到DRAM-我的意思是哪个等级,库等)?

2019-10-16 08:35:37

百万组随机数据matlab和Verilog代码仿真比对;FFT模块详解缩放因子;提供各类定点模型及源代码;提供AD936X配置源码。配套近2000分钟视频教程详述稀疏校验矩阵存储及LDPC编码实现方式

2019-07-23 10:56:41

。ACP为64位AXI从接口,它提供了一个异步缓存相关接入点,实现了PS和PL端加速器之间的低延迟路径。AXI Timer IP核用于计数,可通过其寄存器来计算浮点矩阵乘法运算加速器IP核的运算时间。图

2021-11-11 16:02:09

为配置PL逻辑的控制器),也可以同时配置PS和PL逻辑,可见Zynq芯片可以灵活的搭建嵌入式平台实现不同的功能。这个通过模块图就可以看得更清楚了。http://www.xilinx

2016-10-05 14:05:31

大家好,我已经在PS中产生了一个100Mhz的时钟信号,并使其在外部被PL接收。我使用了原始的ODDR但没有成功我可以从引脚输出100 Mhz时钟。有什么建议么??以上来自于谷歌翻译以下为原文

2019-02-22 09:09:05

为什么一个简单的程序运行不了,请求帮忙看一下。做个LED流水灯,是想用PS部分生成100MHz的频率,然后用这个频率来实现PL部分三色led移位,但是好像PS部分有问题,不知道怎么配置了。这是PS

2016-01-02 21:35:38

对应的信号功能后,在PL的代码里面就不需要写任何的逻辑,甚至引脚分配都不需要(生成的PS系统会自动分配)。但是EMIO就要在PS的系统中引出,然后在PL顶层源码中申明端口类型,做引脚分配(因为EMIO用

2019-10-12 17:35:16

变量表来表达。MCU与Gateway之间的所有交换信息都在这个变量表的表达范围之内。超出变量表的信息,Gateway将水予受理。2.3 PS2000与MCU接口MCU应用系统一般都是以单片机为核心的一个

2018-12-05 10:39:22

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

的Linux的xdevcfg设备来编程PL部件。有趣的解决方案是通过在同一芯片的PS部分运行的XVC远程调试基于Zynq的设计。假设我将XAPP1251中描述的AXI-JTAG控制器添加到我的设计中,是否

2020-07-30 13:51:19

基于PS/2鼠标接口单片机输入设备的实现:详细介绍了PS/2鼠标/键盘接口的工作原理.提出了基于PS/2接口的三键鼠标作为单片机输入设备的方法.该方案占用系统资源少,软硬件

2009-10-27 18:30:48 81

81 什么是ps2接口 ps2接口是什么意思?

PS/2接口是目前最常见的鼠标接口,最初是IBM公司的专利,俗称“小口”。这是一种鼠标和键

2009-05-03 22:07:26 24776

24776

什么是PS/2接口

很多老式的品牌机上采用PS/2口来

2010-01-22 12:21:57 2085

2085 一步一步学ZedBoard:使用PL做流水灯:目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx PlanAhead工具的使用方法。(本资料是其相应的完整工程文件下载)

2012-12-05 13:52:39 185

185 本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 53204

53204

文中详细介绍了PS/2接口协议的内容、电气特性和标准键盘的第二套键 盘扫描码集。给出了基于嵌入式系统的PS/2接口的软、硬件实现方法,并介绍了工控PC外接双键盘的解决方案。

2016-03-25 15:25:53 17

17 分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、PL端接口为FIFO接口; PS到PL的数据传输流程: PS

2017-02-08 01:00:11 1431

1431

因为MicroZed是个低成本的开发套件,所以在板子上除了给PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。

2017-02-09 14:16:11 4135

4135

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 956

956

我们先来了解一下上节中介绍的Zynq SoC PS/PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41 469

469

《一步一步学ZedBoard & Zynq》系列第二篇,目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 3749

3749 构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 视频通过HDMI接口进来,然后经Video Input模块做格式变换,送入VDMA,该VDMA的作用是把数据送入在DDR3中所开辟的帧存中去。另一种是通过摄像头等设备获取视频源,经PS/PL将数据

2017-11-17 10:05:44 7058

7058 zedboard可以将逻辑资源和软件分别映射到PS和PL中,这样可以实现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻辑。以及二者之间的互联特性。这篇笔记主要记录zedboard的大体架构。

2018-06-26 06:24:00 6394

6394 Zynq在PS和PL之间有9个AXI接口。

2018-12-30 09:45:00 6907

6907 Zynq-7000系列基于Xilinx SoC架构。这些产品在单个设备中集成了功能丰富的双核或单核ARM Cortex™-A9处理系统(PS)和28 nm Xilinx可编程逻辑(PL)。ARM Cortex-A9 CPU是PS的核心,还包括片上存储器、外部存储器接口和一组丰富的外围连接接口。

2019-02-23 11:52:33 62

62 MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对实现PS/PL之间的数据交互感到头疼。

2020-09-15 09:27:00 11208

11208

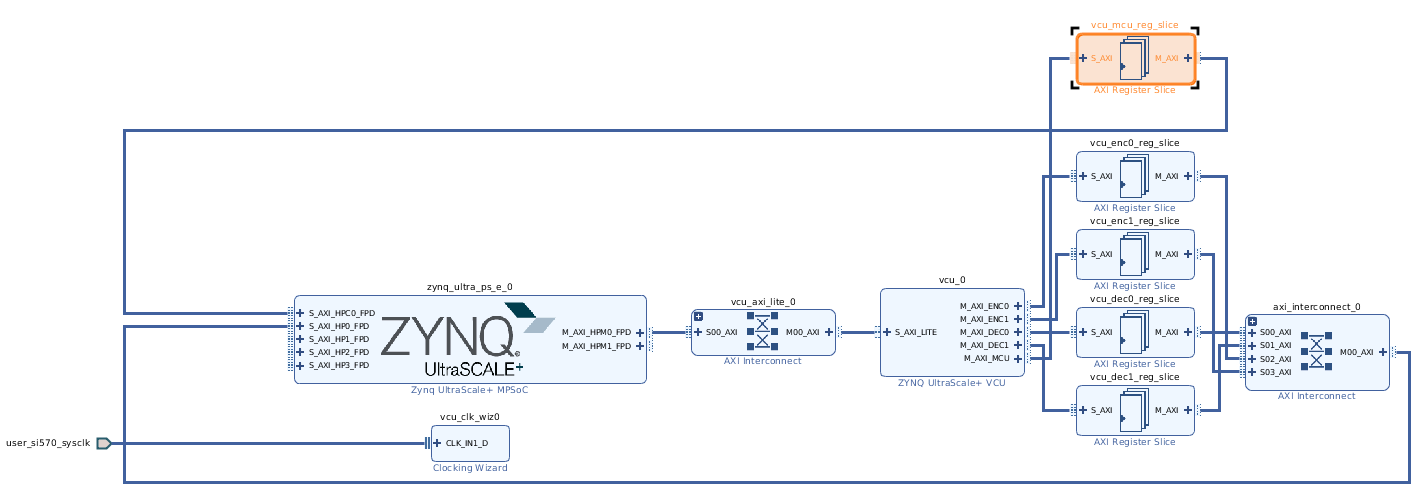

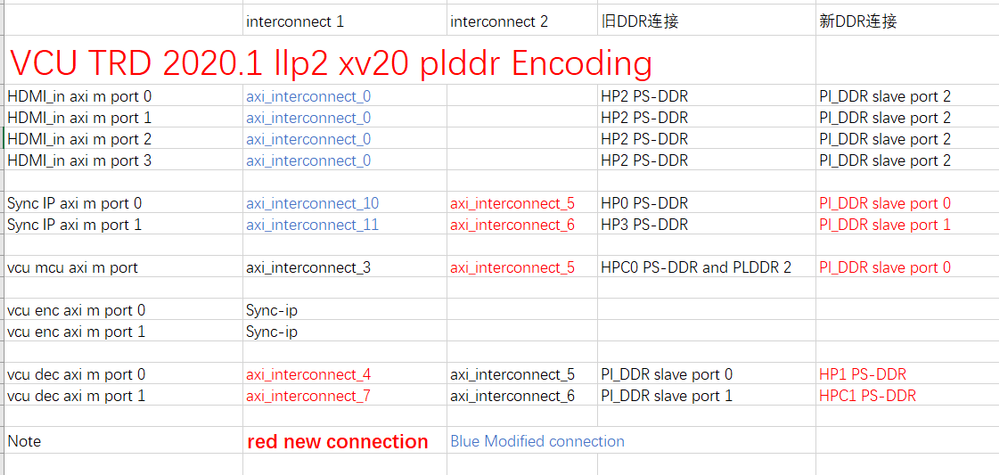

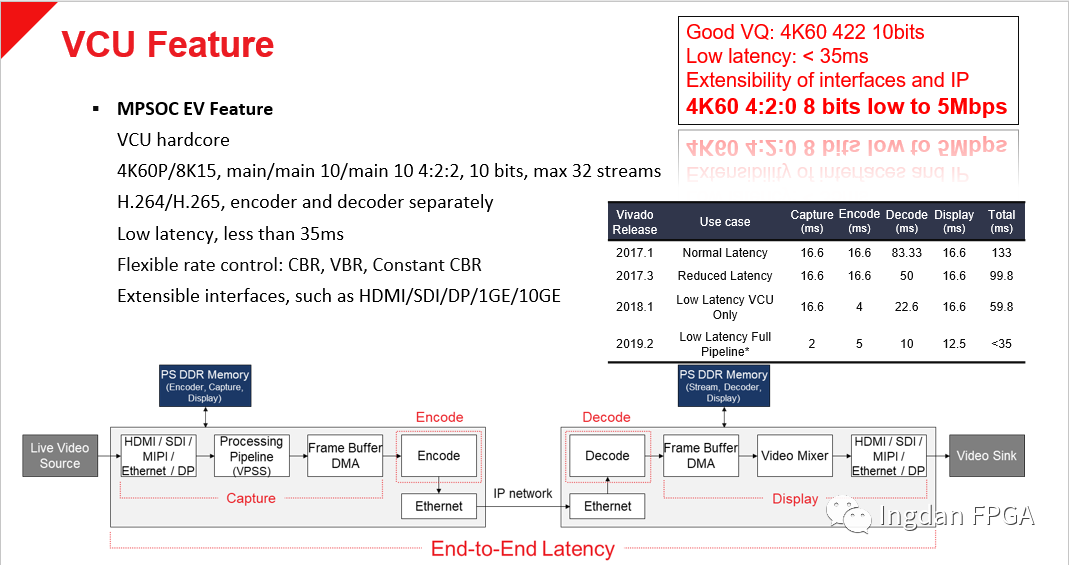

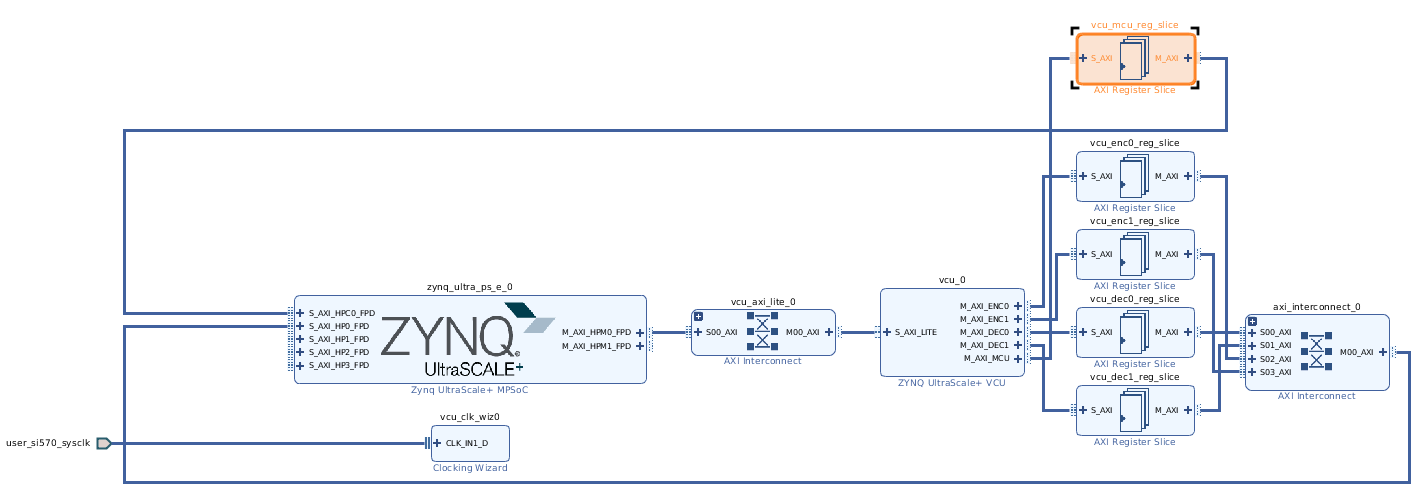

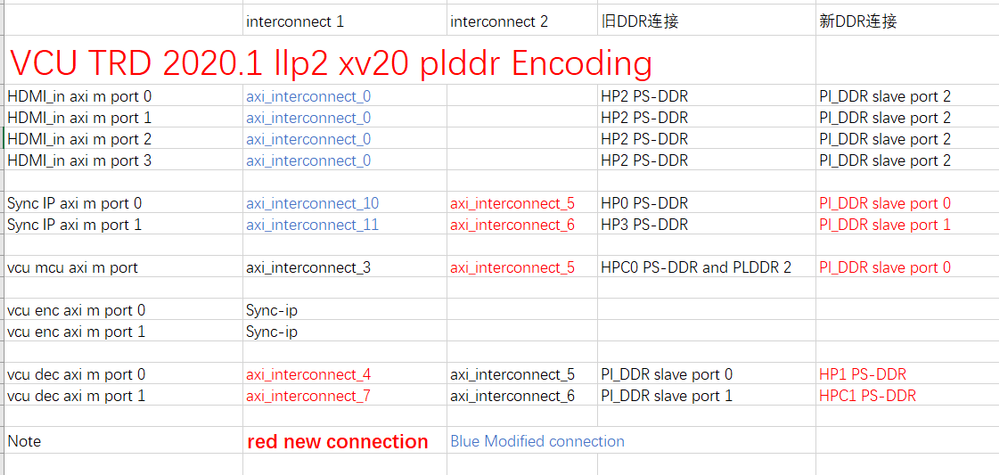

VCU 模块在PL侧,一共有五个AXI接口,它们分别是两个 Encoder AXI,两个 Decoder AXI, 和一个 MCU AXI。

2020-11-30 14:18:23 3835

3835

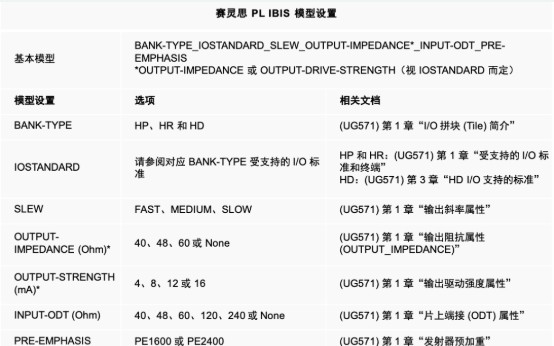

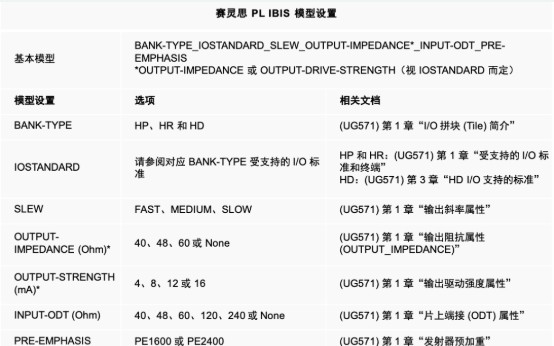

。 本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。 本文主要分 3 个部分: PL I/O 标准 PS MIO

2020-10-15 18:29:15 2147

2147

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2021-01-23 06:32:33 10

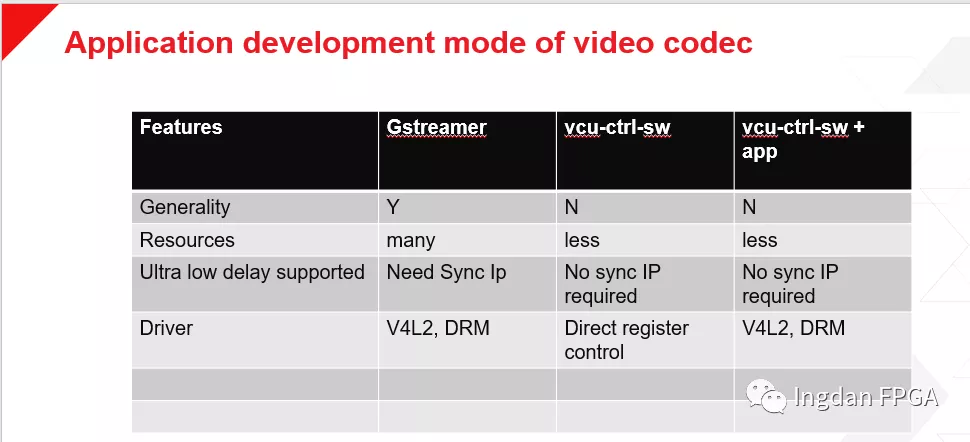

10 Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency XV20 提供了详细命令。 缺省情况下,编码使用的是PS

2021-05-07 15:30:13 6222

6222

刚学ZYNQ的时候,看到里面反复提到PS和PL,还以为PS是PhotoShop的意思,PL是哪种型号的简称。 稍微了解之后才知道,ZYNQ是ARM和FPGA的组合,PS是programming

2021-06-18 16:09:46 8666

8666 PS176是一个显示端口™ (DP)至HDMI™ 2.0视频接口转换器适用于需要视频协议转换的电缆适配器、电视接收器、监视器和其他应用。它将接受任何显示端口输入格式,包括DP 1.1a、dp

2021-12-29 15:03:46 6532

6532

的协议,可用于寄存器式控制/状态接口。例如,Zynq XADC 使用 AXI4-Lite 接口连接到 Zynq PS。

2022-05-10 09:52:12 1949

1949 MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线

2022-08-02 09:45:03 676

676 Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency XV20 提供了详细命令。缺省情况下,编码使用的是PS DDR

2022-08-02 09:12:42 535

535

本应用笔记描述了使用可编程逻辑(PL)中的高速串行收发器通过扩展多路复用I/O(EMIO)接口和1000BASE‑X或SGMII物理接口使用基于处理系统(PS)的千兆以太网MAC(GEM) 。

2022-09-09 10:36:03 1319

1319 电子发烧友网站提供《将Zynq PS和PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29 2

2 S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53 1708

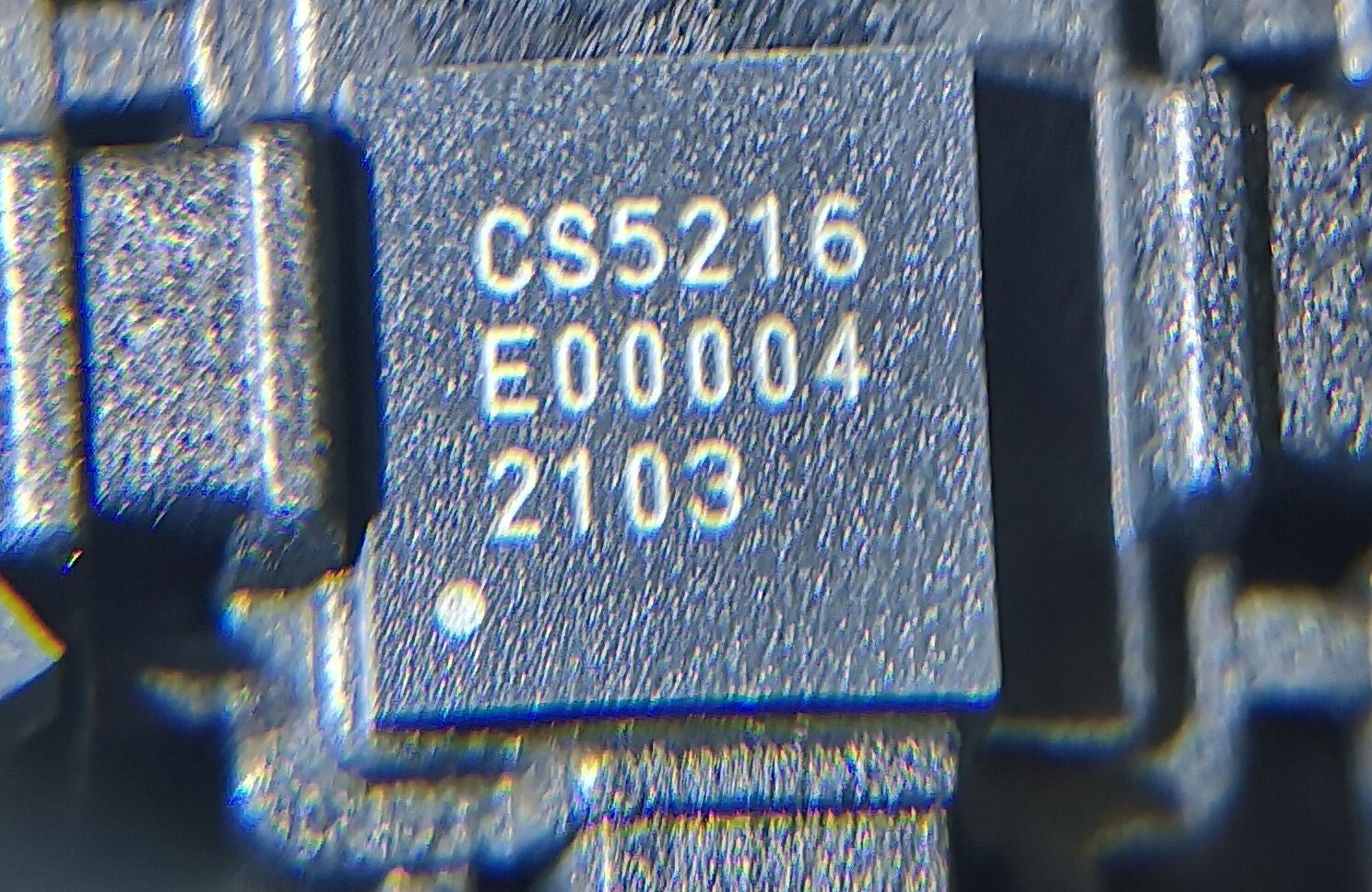

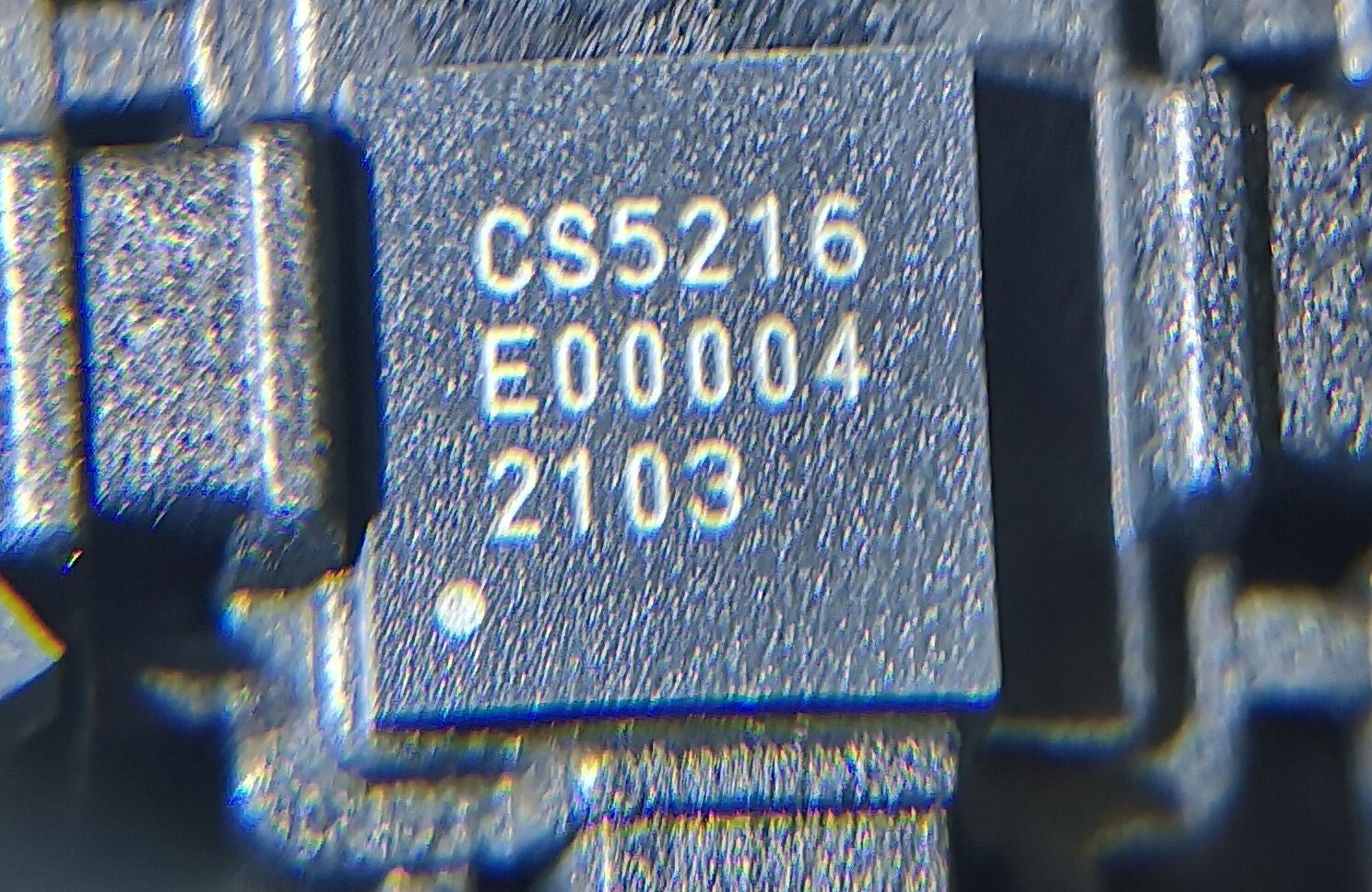

1708 CS5216 DP转HDMI Pin to Pin替代PS8402A方案|PS8402A替代方案|替代PS8402A

2022-03-23 16:16:09 560

560

PS176替代方案|PS176 DP++ to HDMI(4K@30Hz)替代方案|CS5218替代PS176

2022-03-23 18:27:07 974

974

电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案应用笔记.pdf》资料免费下载

2023-09-15 10:29:25 1

1 电子发烧友网站提供《基于PS和PL的1G/10G以太网解决方案.pdf》资料免费下载

2023-09-15 10:05:18 0

0 骊微电子供应PL3368CPL3369C10-12W电源方案,可以直接兼容替换DP2525,更多产品手册、应用料资请向骊微电子申请。>>

2021-12-10 15:18:06 4

4 资料\Demo\All-Programmable-SoC-demos\”目录下。案例包含PL端Vivado工程,主要使用Xilinx提供的标准IP核配置PL端资源实现接口扩展,同时包含PS端裸机/Linu

2023-01-03 15:50:37 18

18

正在加载...

电子发烧友App

电子发烧友App

评论