linear.com.cn/altera 查阅。凌力尔特的解决方案满足了 Arria 10 FPGA开发套件及其支持性系统构件的关键功率要求。例如: LTC3877 VID 控制器和 LTC3874 相位扩展器 DC/DC 稳压器可采用一个 12V 输入为内核电源轨在 0.95V 提供 105A。

2015-08-28 14:58:15 2314

2314

今日,三星电子正式宣布已经开始大规模生产基于10nm FinFET技术的SoC,这是业界内首家提供10nm工艺代工厂商。新工艺下的SoC性能可以提供27%,功耗将降低40%。

2016-10-17 14:07:01 873

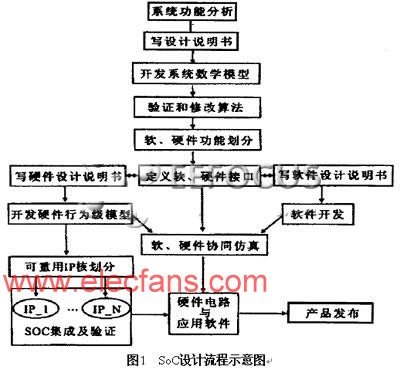

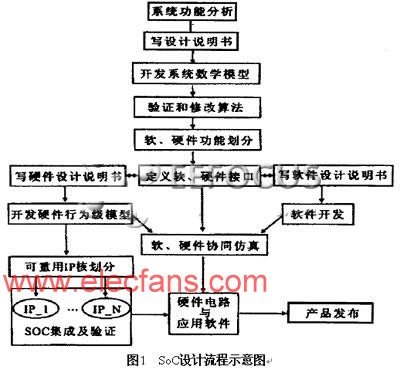

873 片上系统(soc)正日益成为一种网络,您可以在其中添加单独的知识产权(IP)模块。SoC IP模块包括处理器、内存控制器、专用子系统和 I/O——这些模块可以从互连IP中分离开来,并放入日益复杂的SoC分区。

2020-05-04 11:31:00 1136

1136 各种考虑因素在设计过程中发挥了特殊作用:指定 FPGA 的 I/O 接口、识别不同的时钟域、定义基本设计功能的框图、集成 IP 块、制定功能的验证/测试计划整个团队(可制造性设计)。

2022-08-15 11:23:40 213

213 在系统芯片(SoC)设计中, DDR模块是一种重要的组成部分。它不仅在提高系统性能方面起着关键作用,还对于优化系统功耗管理具有重要意义。

2023-09-13 09:47:54 1544

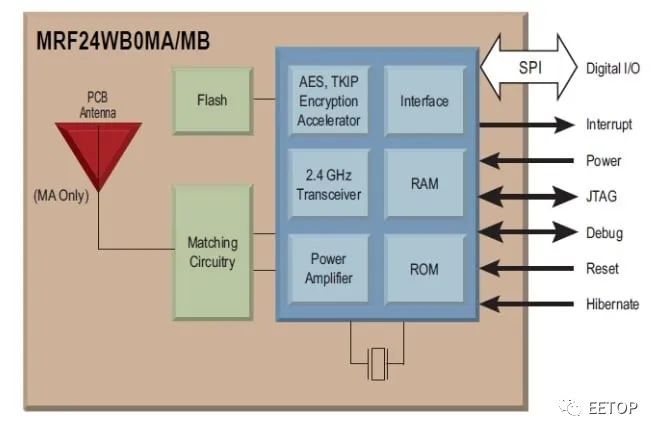

1544 在设计物联网 (IoT) 设备时,是使用无线模块还是片上系统 (SoC) 可能是一个关键且具有挑战性的决定。

2023-12-01 13:42:50 655

655

BOARD BATTERY FOR SOC'S

2023-03-29 19:51:22

为什么现在原来越多的模块封装成SOC

2023-11-02 06:47:31

随着SOC越来越复杂,包含的IP越来越多,单个SOC上实现了CPU、射频模块、DDR控制模块、外设等等功能。各种功能,多种IP也带来了多档电源的需求。同时为了满足低功耗的要求,SOC通常被分为多个

2021-10-28 09:45:05

拥有成本,从而带来可持续的长期盈利能力。美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本优化的封装

2019-06-24 07:29:33

倾向将SoC定义为将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常是客户定制的,或是面向特定用途的标准产品。SoC定义的基本内容主要在两方面:其一是它的构成,其二

2016-05-24 19:18:54

描述This power supply design is used as the main power converter for the Altera Arria GX II FPGA.The

2018-09-06 09:17:06

FPGA 供电时所需的所有电源轨。为提供正确的电源定序,此设计采用 UCD90120A 电源序列发生器和监视器,并可通过 I2C 对它们进行控制。主要特色提供为 Altera Arria V FPGA

2018-09-12 09:08:24

描述PMP9449 参考设计提供为 Altera 的 Arria® V GX 系列 FPGA 供电时所需的所有电源轨。它使用 TPS38600 监控输入电流并提供上电定序。此设计采用低成本、小尺寸

2018-12-04 11:33:24

描述Power Solution Reference Design for Arria V FPGA from Altera.This solution uses integrated

2018-12-21 11:44:05

DK-SOC-10AS066S-A

2023-03-28 13:19:47

DEV KIT ARRIA 10 SX SOC

2024-03-14 20:40:18

使用DS5连接arria 10 soc的hps,出现unable to connect to TCP:localhost失败,请问有熟悉的能解释是啥原因吗

2017-08-23 13:54:47

,RF和蓝牙。它还提供了一堆可配置的GPIO,这些GPIO被配置为数字外设,用于不同的应用和控制用途。DT-BL10 WiFi模块使用BL602作为Wi-Fi和BLE共存SOC芯片。DT-BL10 WiFi模块集

2022-02-10 07:57:45

刚刚入手fpga,要求设计一个简单的soc,带有基本的模块CPU,RAM,串口通信模块,支持与外部的SPI Flash进行通信,求设计思路,学习步骤等,时间比较紧迫

2015-04-19 17:26:18

描述A 4 phase buck regulator design fully complaint to power the core rail of Intel Arria 10 GX FPGAs

2018-12-06 11:44:20

因客户退单,有900颗 Intel Arria10芯片,料号:10AX066N2F40I2LG有意请联系 QQ/邮箱:22101076

2019-03-13 23:10:30

了3款足够“有料”的FPGA及SoC系列:Arria 10、Stratix 10以及MAX 10,它们都是Altera在创新大潮中重磅推出的“第10代”(Generation 10)产品,也为

2019-07-01 08:14:44

我最近尝试用arria 10 soc实现与ad9680之间的jesd204B协议,看了很多资料,却依然感觉无从下手,不知道哪位大神设计过此协议,希望可以请教一番,在此先谢过。

2017-12-13 12:47:27

从ALtera官网下载了一个参考设计,其基于stratix V,但我的开发板型号为Arria 10 SOC,做相应修改后,编译出现以下,不知道有人遇到过没有,求帮助。Error (14566

2018-01-07 21:16:13

。根据设计只要时钟输入正确,加载程序后就能通过光口发送数据。该程序在开发板上能够正常输出数据,在设计板上没有任何反应。问题:1、两种芯片都是Arria10 系列,程序移植是否存在问题?程序编译没报错

2019-08-15 16:21:31

基于DSP核控制的SoC系统是由哪些部分组成的?基于DSP核控制的SoC系统该如何去设计?

2021-06-18 09:42:47

SoC芯片结构及物理实现流程介绍SoC芯片时序约束设计的关键在于功耗管理控制模块的时序约束时钟树设计的内容有哪些?

2021-04-13 06:45:17

NCV-RSL10是通过蓝牙5认证并符合车规的系统单芯片(SoC),具有极高的安全性和可靠性,用于汽车无匙进入、信息娱乐控制、主动安全和自动驾驶等应用,为汽车行业带来行业最低功耗。

2021-01-27 07:17:41

工业系统通常由微控制器和FPGA器件等组成,美高森美(Microsemi® )基于 SmartFusion®2 SoC FPGA的马达控制解决方案是使用高集成度器件为工业设计带来更多优势的一个范例。

2019-10-10 07:15:34

怎样去设计一种基于SoC的音频IP模块?

2021-06-07 06:25:00

关于altera arria GX260的flash是直接连到芯片上的还通过CPLD连上的,这个型号的最简单的配置芯片是那一个啊~~~~~~~~~~~~~~~跪求高手指教指教~~~~~~~~~~~~~~小弟感激涕零~~~~~~~~~~~~

2012-06-13 15:58:08

单个芯片上集成一个完整的系统,一般包括系统级芯片控制逻辑模块、微处理器/微控制器CPU内核模块、数字信号处理器DSP模块、嵌入的存储器模块、和外部进行通信的接口模块、含有ADC/DAC的模拟前端模块

2016-08-05 09:08:31

设计和实现方面的某些妥协。这一点在电源中最为明显,电源必须更精确,更灵活,更可控,更小,更高效,并且每次新一代FPGA都具有更多的故障感知能力。在本文中,我们将特别介绍Altera Arria 10 FPGA

2018-09-10 10:38:23

`描述及特性This power supply design is used as the main power converter for the Altera Arria GX II FPGA.

2015-04-20 14:41:27

内核供电,这有几个特点以配合 SoC 的节能方案: Arria 10 的 SmartVID 采用 DC/DC 稳压器的集成型 6 位并行 VID 接口,以控制 DC/DC 稳压器以及降低静态和动态状态

2018-10-29 17:01:56

电源调试时间。 一个很好的例子:给 Arria 10 FPGA 和 Arria 10 SoC 供电 系统开发人员可以使用 FPGA 开发工具评估 FPGA,而无须设计一个完整的系统。图 1 和图

2018-11-20 10:46:52

,因为这样可以节省电源调试时间。 一个很好的例子:给 Arria 10 FPGA 和 Arria 10 SoC 供电 系统开发人员可以使用 FPGA 开发工具评估 FPGA,而无须设计一个完整的系统

2018-10-15 10:30:31

提出了一种在HDTV SOC 系统中实现多模块共享存储单元的高效SDRAM 控制器。通过利用合理的请求仲裁、Full Page 读写、指令与数据分离、指令缓存和前后相关处理等机制,实现了高吞吐

2009-08-14 16:09:14 13

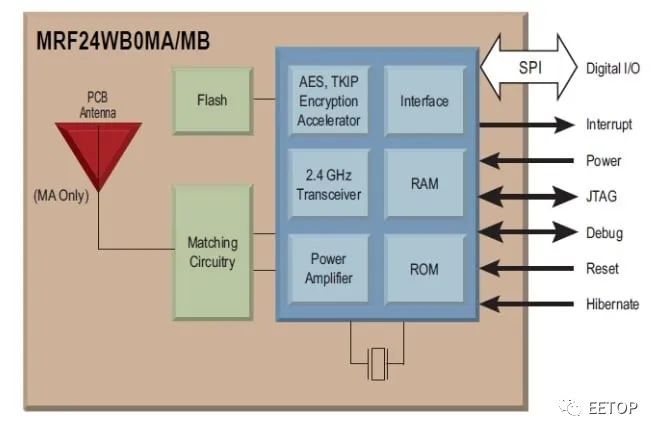

13 SOC 无线收发模块(内置MCU)

2023-10-08 16:37:54

基于DC/DC转换器,针对Altera Arria II G的高性能电源解决方案,电路如图:

2010-12-12 10:40:31 36

36 Altera宣布Altera 40-nm Arria II GX FPGA通过PCI-SIG的PCIe Express 2.0规范测试

Altera公司宣布,其40-nm Arria II GX FPGA符合

2009-07-30 08:13:09 610

610 基于SoC的音频IP模块设计

随着集成电路设计技术和深亚微米制造技术的发展,集成电路已进入了片上系统时代。由于SoC结构极其复杂,对于设计者而言,数百万门规模

2009-12-11 11:08:12 917

917 Altera 40-nm Arria II GX FPGA转入量产

Altera公司今天宣布,开始量产发售40-nm Arria® II GX FPGA系列的第一款器件。Arria II GX器件系列专门针对3-Gbps收发器应用,为用户提供了

2010-02-25 09:21:16 986

986 介绍了Arria II GX FPGA亮点,高速收发器特性,Arria II GX FPGA架构以及Arria II GX FPGA 开发套件主要特性,开发板方框图,详细的开发

2010-07-27 17:03:44 3196

3196

什么是soc芯片

SoC(System on Chip)。SoC是在一个芯片上由于广泛使用预定制模块IP而得以快速开发的集成电路。

2010-09-10 22:50:51 45585

45585

Altera公司(NASDAQ: ALTR)今天宣布,开始发售其28-nm Arria® V FPGA。Arria V器件是目前市场上支持10.3125-Gbps收发器技术、功耗最低的中端FPGA

2011-11-30 16:26:41 1229

1229 本文是基于Arria V和Cyclone V精度可调DSP模块的高性能DSP应用与实现(英文资料)

2012-09-05 14:18:43 35

35 Altera的Arria FPGA设计用于对成本和功耗敏感的收发器应用。Arria FPGA系列提供丰富的存储器、逻辑和数字信号处理(DSP)模块资源,结合10G收发器优异的信号完整性,帮助您集成更多的功能,

2012-09-06 19:53:53 4950

4950 Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行发布的包括高端Stratix10和中端Arria10系列。目标是替代传统的ASSP和ASIC。

2013-06-13 14:26:14 2150

2150 9月26号,北京——Altera公司(Nasdaq: ALTR)今天宣布,开始量售其Cyclone® V SoC芯片以及Arria® V SoC工程样片。随着处理器峰值时钟频率的提高——商用

2013-09-26 17:48:23 993

993 现在,您可以采用 Altera SoC 器件来设计定制器件,这是我们流行的28 nm Cyclone V 和 Arria V 系列中的型号。我们的 SoC 器件将帮助您满足多变的市场需求和接口标准。

2013-10-10 15:51:34 137

137 2013年12月3号,北京——Altera公司(Nasdaq: ALTR)今天发布了Arria 10版Quartus II软件,这是业界第一款支持20 nm FPGA和SoC的开发工具。基于TSMC

2013-12-03 10:48:47 1607

1607 2014年8月19号,北京——Altera公司(Nasdaq: ALTR)今天发布Quartus® II软件Arria® 10版v14.0——业界最先进的20 nm FPGA和SoC设计环境。

2014-08-19 15:53:24 2582

2582 2014年,12月16号,北京——Altera公司(Nasdaq: ALTR)今天发布其Quartus® II软件v14.1,扩展支持Arria® 10 FPGA和SoC——FPGA业界唯一具有硬核浮点DSP模块的器件,也是业界唯一集成了ARM处理器的20 nm SoC FPGA。

2014-12-16 13:48:53 1396

1396 基于AMBA与WISHBONE的SoC总线桥KBar控制器的设计_陈俊锐

2017-03-19 11:31:31 0

0 SoC中的六项隐性成本 在无线模块和无线SoC之间选择时的考虑因素

2017-09-05 15:12:50 1

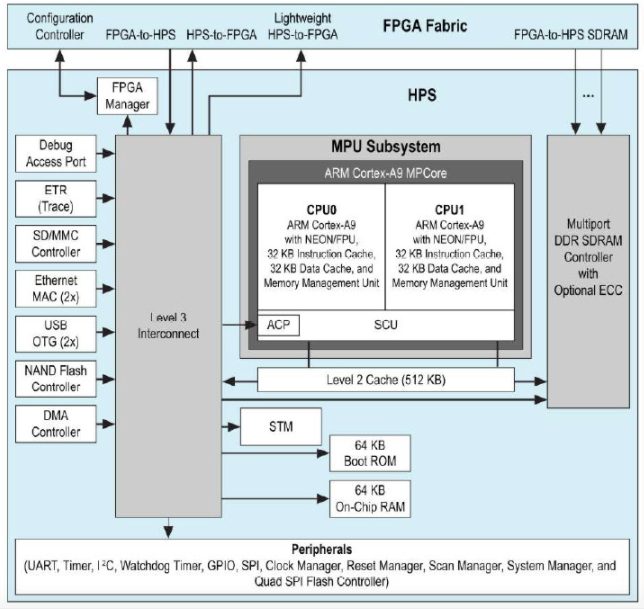

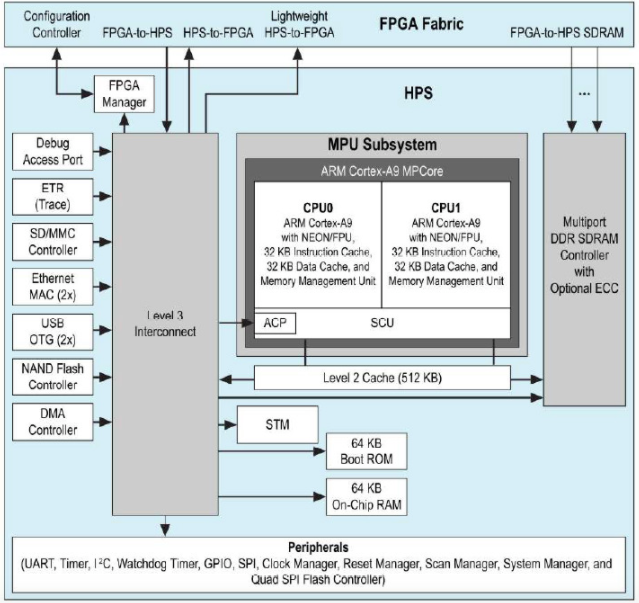

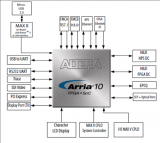

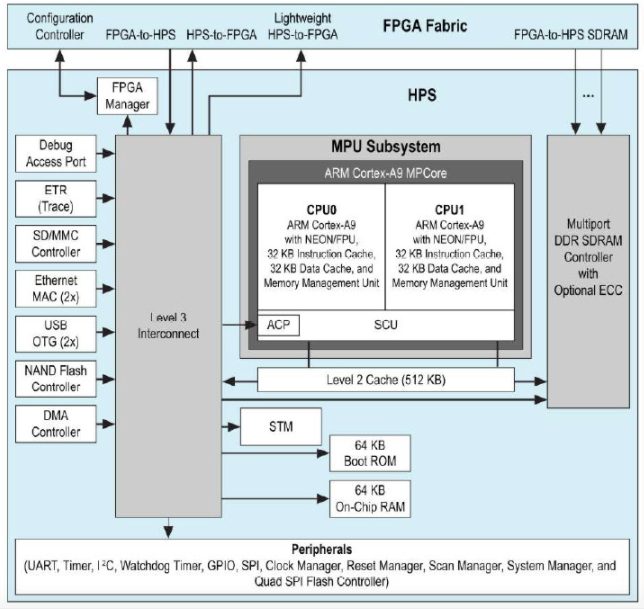

1 本文介绍了Arria 10 SoC FPGA主要特性,框图以及Arria 10 SoC开发板主要特性,电源分布网络图和电路图。

2018-06-16 06:31:00 9763

9763

您是否需要不断提供越来越多的设计功能,同时还要跟上新标准的变化,降低成本和功耗?请观看这一新的7分钟视频,看看在我们具有高端功能的低成本收发器FPGA——Arria II GX上实现各种协议。您将

2018-06-22 06:56:00 3278

3278 如何为 LVDS SERDES约束Arria 10 器件 IOPLL 位置

2018-06-22 08:47:00 5539

5539

使用厂商内存模型运行 Arria 10 RLDRAM3 示例设计仿真

2018-06-20 01:48:00 1865

1865

为 Arria 10 开发套件构建 RLDRAM3 EMIF 设计

2018-06-22 01:19:00 2941

2941

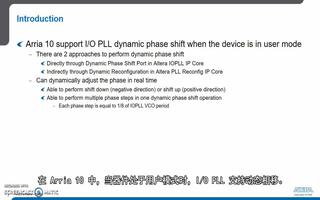

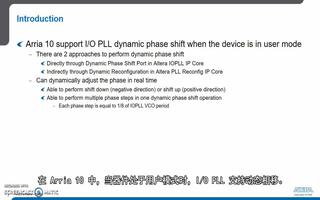

如何在 Arria 10 中实现 I/O 锁相环 (PLL) 动态相移

2018-06-20 04:56:00 3156

3156

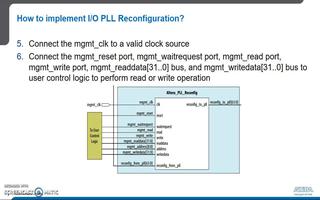

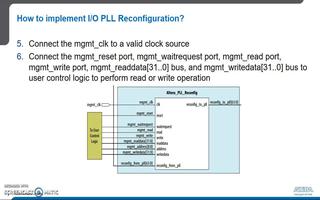

如何在 Arria 10 中实现 I/O 锁相环 (PLL) 重配置

2018-06-20 00:57:00 3438

3438

Arria 10混合存储器立方体控制器演示第二部分

2018-06-22 02:59:00 3195

3195

Arria 10 单工发送器和接收器

2018-06-20 01:01:00 3645

3645

Arria 10混合存储器立方体控制器演示第一部分

2018-06-22 01:02:00 3176

3176

Arria 10 早期功耗估算器

2018-06-20 00:05:00 3239

3239

Arria10接口的JESD204B与ADI9144的互操作性

2018-06-20 00:06:00 4052

4052

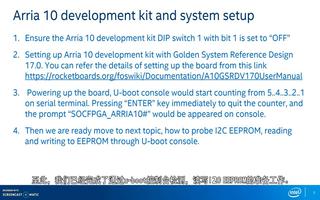

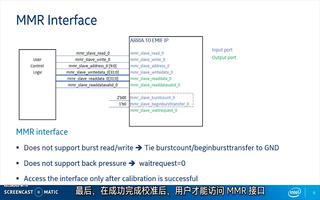

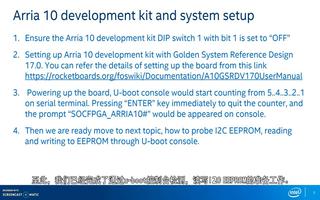

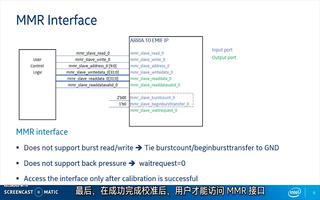

在 Arria 10 中设计 I2C EEPROM

2018-06-22 01:11:00 2915

2915

Arria® 10 用户控制刷新

2018-06-26 00:14:00 2496

2496

如何在Arria 10 PCI Express (PCIe)中更改串行(Serial)和PIPE仿真

2018-06-20 00:27:00 4869

4869 为Arria10自动生成预定义的signaltap II文件

2018-06-22 05:33:00 2855

2855 Arria 10外部存储器接口(EMIF)工具包

2018-06-11 17:10:20 1985

1985

了一片Arria 10 SoC和集成双核ARM Cortex-A9处理器,同时采用了Mobiveil的固态硬盘(SSD)控制器,以及NVMdurance的NAND优化软件。这一参考设计提高了NAND应用的性能和灵活性,同时延长了数据中心设备的使用寿命,从而降低了NAND阵列的成本。

2018-08-24 16:47:00 605

605 美高森美公司(Microsemi) 宣布提供带有模块化电机控制IP集和参考设计的SmartFusion2 SoC FPGA双轴电机控制套件。这款套件使用单一SoC FPGA器件来简化电机控制

2018-08-24 17:29:00 1129

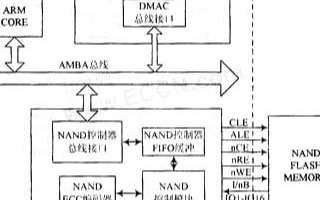

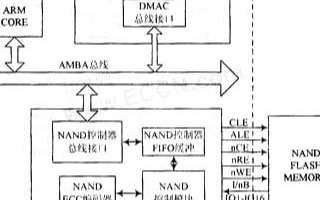

1129 本文所讨论的NAND FLASH控制器是针对一款基于ARM7TDMI的SoC芯片,该控制器在芯片中的位置如图1所示,作为AMBA总线上的一个从设备集成于AHB上。主要模块包括总线接口模块、FIFO缓冲模块、ECC编码模块以及逻辑控制模块。

2020-05-20 08:00:00 1734

1734

超声流量计SoC:精度提高10倍

2020-05-30 12:13:00 1570

1570 ADI Guneet Chadha探讨电源系统管理(PSM)如何确定Intel Arria ARM Cortex 20nm SoC FPGA上8个电源的时序或按照预定顺序开启各电源

2019-07-24 06:16:00 1618

1618 Intel正式宣布,以现在准备开始量产Xeon Scalable处理器——Xeon Gold 6138P,该处理器整合了Arria 10 FPGA,并开始向供应商发货了。

2019-08-15 17:46:30 862

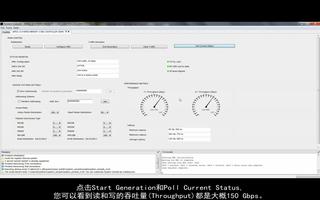

862 英特尔至强6138P包括一个Arria10 GX 1150 FPGA内核,和高达160Gbps的I/O吞吐量的带宽和高速缓存接口,可实现紧耦合加速。

2019-09-16 17:48:55 7167

7167 MLink-DO10 10路继电器输出模块是脉联公司针对设备控制与RS485总线监测的装置。MLink-DO10 10路继电器输出模块基于成熟的嵌入式软硬件平台,具有实时性强、可靠性高的特点,提供6组共用公共端继电器控制输出,3组独立公共端继电器控制输出,1组继电器通过模块自身逻辑判断输出。

2020-05-11 14:47:40 1014

1014 10 路继电器输出模块是脉联公司针对设备控制与 RS485 总线监测的装置。 MLink-DO10 10 路继电器输出模块基于成熟的嵌入式软硬件平台,具有实时性强、可靠性高的特点,提供 6 组共用公共端继电器控制输出, 3 组独立公共端继电器控制输出, 1 组继电器通过模块自身逻辑判断输出。

2020-05-11 16:45:31 973

973 英特尔的SoC开发套件提供了开发定制ARM快速和简单的方法*处理器的SoC设计。设计生产率是Arria 10 SoC架构的驱动理念之一。Arria 10 SoC提供与上一代SoC的完全软件兼容性

2020-05-20 14:05:56 1243

1243 Altera Arria V系列FPGA的电源解决方案

2021-04-29 08:58:06 9

9 DK-SOC-10AS06S-A设备原理图套件

2021-05-19 11:31:29 1

1 更改AN-710(AD6674/AD9234/AD9680/AD9690 Stratix5-Arria10)

2021-05-22 09:51:27 10

10 可提供中端市场中的最佳性能和能效。英特尔 Arria 10 FPGA 和 SoC 的高性能逻辑结构,结合了适用于芯片至芯片和芯片至模块接口、

2021-05-31 09:42:42 2704

2704 FPGA-SoC芯片中EDAC模块的设计与实现(深圳市宇衡源电源技术)-该文档为FPGA-SoC芯片中EDAC模块的设计与实现简介文档,是一份还算不错的参考文档,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 。------------------------------------------随着SOC越来越复杂,包含的IP越来越多,单个SOC上实现了CPU, 射频模块,相机模块,DDR控制模块,外设等等功能。多...

2022-01-11 15:43:49 7

7 开发具有强大架构的产品是确保系统设计满足现在和未来性能要求的关键。借助用于嵌入式系统的 SoC,设计立足于坚实的基础。用于中型应用的 FPGA 可显着节省空间并在功耗、成本和性能之间取得良好平衡。Arria 10 SoC就是这样一个典型代表。

2022-06-08 09:31:24 503

503 因此,英特尔 Arria 10 SoC 为嵌入式外设、硬核浮点 DSP 模块、嵌入式高速收发器、硬核存储器控制器和协议 (IP) 控制器提供了具有广泛功能范围的处理器。

2022-06-08 09:50:57 1047

1047

借助 Arria 10 SoC,您可以通过将 GHz 级处理器、FPGA 逻辑和数字信号处理 (DSP) 集成到单个可定制的片上系统中来减小电路板尺寸,同时提高性能。

2022-06-30 09:50:09 914

914 具有硬化浮点 DSP 模块的 FPGA 在中端 Arria 10 构建模块中提供 160 到 1,500 GFLOPS 的容量。这些峰值 GFLOPS 指标的计算基于 CPU、GPU 和 DSP 上使用的相同透明方法。

2022-08-15 11:34:28 831

831 SoC中的FPGA核,如Zynq MPSoC系列或Intel(原Altera)SoC,如Stratix SoC、Arria SoC等。

2022-09-15 09:17:42 975

975

正在加载...

电子发烧友App

电子发烧友App

评论