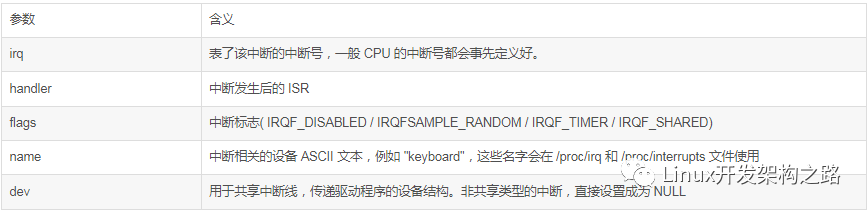

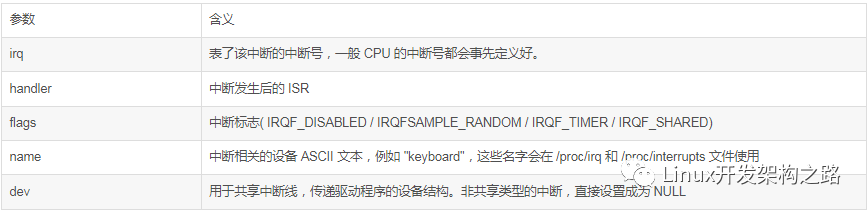

裸机编程中使用中断比较麻烦,需要配置寄存器、使能IRQ等等。而在Linux驱动编程中,内核提供了完善的终端框架,只需要申请中断,然后注册中断处理函数即可,使用非常方便。

2022-07-29 08:57:24 597

597 中断:是指CPU在运行过程中,出现了某种异常事件,需要CPU先暂停当前工作,转而去处理新产生的异常事件,处理完后再返回暂停的事件继续往下执行。就例如我们正在使用手机进行微信视频聊天,这时突然有人打电话过来,这时手机的处理方式是手机来来电铃声响起,通知用户电话来了。

2022-09-23 09:01:07 1231

1231

在聊中断机制之前,我想先和大家聊一聊中断机制出现的前因后果。最一开始计算机操作系统的设计是能够一次性的执行所有的计算任务的,这被称为顺序执行,也是批处理操作系统(Batch system)。

2023-08-07 09:18:28 843

843

ARM处理器是一种流行的处理器架构,用于许多现代移动设备和嵌入式系统中。中断和异常是ARM处理器中的两个重要概念,它们是处理器中断程序执行的关键机制。

2023-09-05 15:45:30 695

695

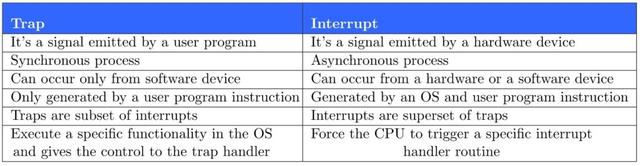

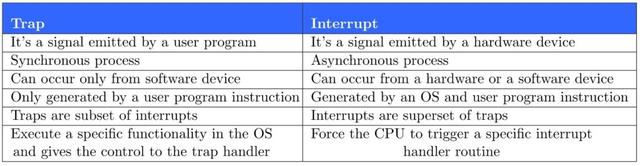

异常和中断会暂停程序以响应硬件或软件中的意外事件。中断是异步事件,异常是同步事件,但是中断和异常之间的区别也取决于具体情况。

2023-09-14 15:20:18 949

949

文章目录linux系统中出现并发与竞态相关概念:四种情形:linux内核解决竞态引起的异常的方法:即同步方法中断屏蔽概念特点中断屏蔽的编程步骤中断屏蔽相关宏函数应用实例自旋锁概念特点利用自旋锁同步

2021-07-28 06:15:51

中断处理程序的执行可以被具有更高优先级的异常抢占。可以执行多少个具有更高优先级的异常中断?产生了两个中断。这个数字是无限的吗?

2022-12-09 08:01:35

M0内核支持的资源Cortex-M0处理器最多支持32个外部中断(通常称作IRQ),还有一个被称作不可屏蔽中断的特殊中断。中断事件的异常处理通常被称作中断服务程序(ISR)。除此之外,M0处理器还

2021-12-21 06:50:48

stm32学习笔记(2)中断和异常的区别外中断——就是我们指的中断——是指由于外部设备事件所引起的中断,如通常的磁盘中断、打印机中断等;内中断——就是异常——是指由于 CPU 内部事件所引起的中断

2022-01-07 08:05:11

如何从异常中断返回?异常中断处理程序结构什么样?何为异常中断向量表?哪一种异常中断优先级最高?

2021-12-14 07:40:24

表:异常处理的大致流程主要针对中断进行讲解,其他的类似2. 中断异常当手机接到一个电话时,电话模块他会接到这个信号,电话和手机内部的CPU通过某个管脚相连,电话模块通过这个管教把信号发给CPU,CPU

2022-04-26 09:37:10

如下表:异常处理的大致流程主要针对中断进行讲解,其他的类似2. 中断异常当手机接到一个电话时,电话模块他会接到这个信号,电话和手机内部的CPU通过某个管脚相连,电话模块通过这个管教把信号发给CPU

2022-05-05 10:16:31

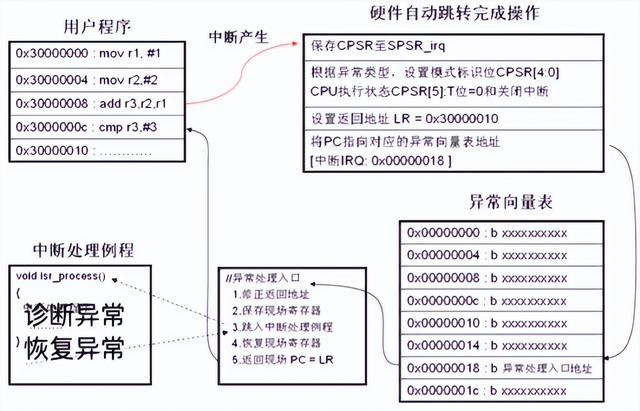

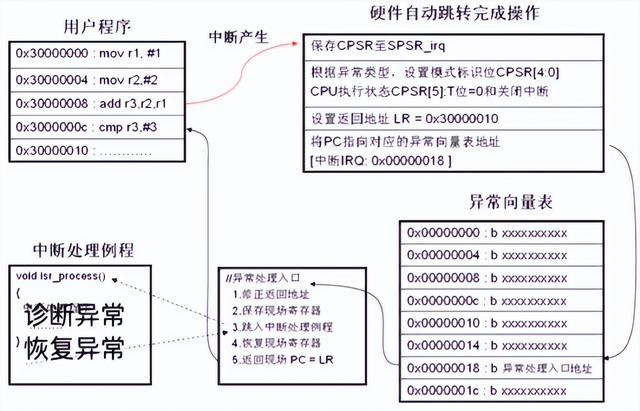

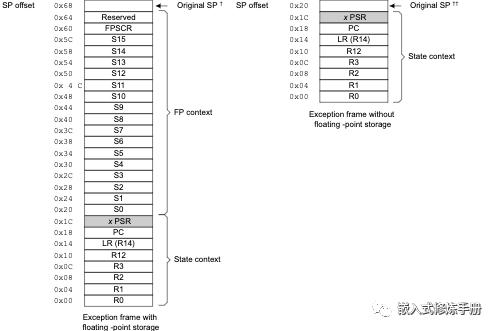

ARM处理器异常相应过程:1、保存处理器当前状态、中断屏蔽位以及各个条件标志位。将当前程序状态寄存器CPSR保存到对应的SPSR寄存器中实现。每个异常中断都有对应的物理SPSR寄存器。2、设置

2021-12-14 08:57:34

中断且查看是否允许中断,如果处理器产生了中断,这时PC的值已经更新,即PC指向了当前指令后第三条指令的位置(被中断指令地址加12),产生FIQ与RIQ异常后处理器将PC-4的值保存到了对应模式下的LR

2017-03-02 15:08:27

中断且查看是否允许中断,如果处理器产生了中断,这时PC的值已经更新,即PC指向了当前指令后第三条指令的位置(被中断指令地址加12),产生FIQ与RIQ异常后处理器将PC-4的值保存到了对应模式下的LR

2017-03-07 16:40:45

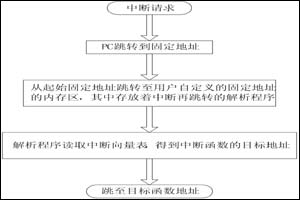

的中断号。 所以,当SWI指令触发了一次异常后进入异常处理的程序时,异常程序必须要从SWI指令中提取出来中断号,即提出出来SWI指令中低24位的值,从而得到用户请求的特定的SWI功能。 通常情况下

2017-01-10 15:09:37

异常和中断处理程序做出相应的处理,当处理完成后,要返回到被中止的指令,使被中止的指令能够继续正常执行下去。因此,确定异常和中断处理程序的返回地址是一个非常重要的问题。下面是中断异常入口、返回指令、返回

2013-05-24 10:30:42

异常和中断处理程序做出相应的处理,当处理完成后,要返回到被中止的指令,使被中止的指令能够继续正常执行下去。因此,确定异常和中断处理程序的返回地址是一个非常重要的问题。下面是中断异常入口、返回指令、返回

2013-08-09 16:15:24

异常就是正在执行的指令,由于各种软件或硬件故障被打断,比如,在读数据或指令时,访问存储器失败、产生了一个外部硬件中断等。当这些情况发生时,在ARM系统里,由异常和中断处理程序做出相应的处理,当处理

2013-04-08 10:53:07

在学习与开发ARM处理器的过程中,一个不能绕开的话题就是异常处理流程。它在ARM的体系架构中,占据着不可动摇的重要地位。此处就以Coterx-A系列的ARM处理器简单分析一下异常中断处理流程。说异常

2016-11-11 09:55:57

在学习与开发ARM处理器的过程中,一个不能绕开的话题就是异常处理流程。它在ARM的体系架构中,占据着不可动摇的重要地位。此处就以Coterx-A系列的ARM处理器简单分析一下异常中断处理流程。说异常

2016-10-14 16:15:42

异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。当异常中断处理程序执行完成后,程序返回到发生中断的指令的下一条指令处执行。在进入异常中断处理程序时,要保存被中断的程序的执行

2020-08-28 08:09:17

和 FIQ 异常中断处理的返回:指令地址对应于 PCAPC-8执行此指令完成后(!)查询 IRQ 及 FIQ,如果有中断请求则产生中断. A+4 PC-4A+8 PC;lr!(此时 PC 的值已经更新

2016-07-22 11:32:45

(A+8); lr = pc – 4(这时处理器决定的,无法更改!)即 A+4。由于这类异常返回后应执行下一条指令(A+4),所以返回时,pc = lr 即可。 2.IRQ 和 FIQ 异常中断处理的返回

2017-05-05 14:47:47

。 2.IRQ 和 FIQ 异常中断处理的返回:指令地址对应于 PCAPC-8执行此指令完成后(!)查询 IRQ 及 FIQ,如果有中断请求则产生中断. A+4 PC-4A+8 PC;lr!(此时 PC

2016-03-31 16:09:03

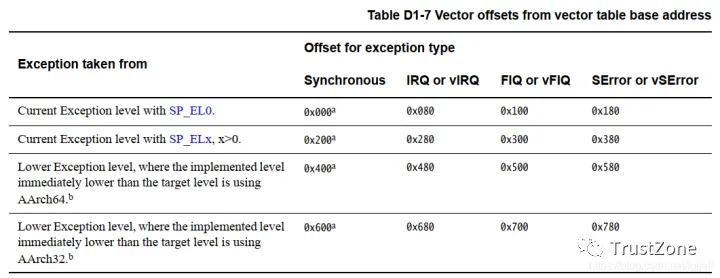

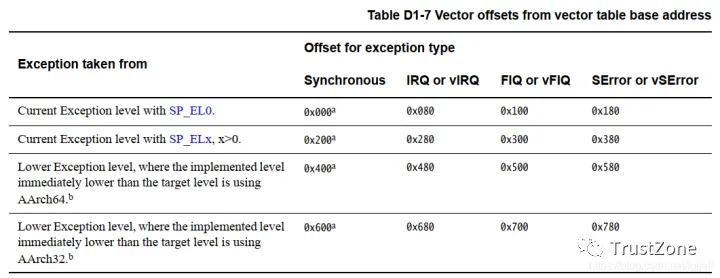

1、ARMV8-aarch64异常和中断处理概念(AArch64 Exception and Interrupt Handling)异常是指需要特权软件(an exception handler

2022-06-01 17:46:31

外部的硬件通常发出中断信号,但也有其他几种可能导致核心发生异常的事件,例如内部事件,如操作系统调用使用SVC指令。

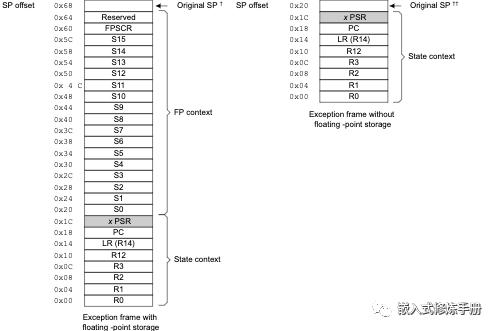

如果实现了ARMv8-M安全扩展,它将修改异常处理的某些方面。

2023-08-02 06:09:37

经典ARM微处理器包括7种异常:1、 复位异常2、 未定义指令异常3、 软件中断异常4、 预取指令异常5、 数据异常6、 IRQ(中断)7、 FIQ(快速中断)异常,单片机为中断,笼统来讲可以把异常

2021-07-16 07:04:57

CAN通信中,如果没有中断异常处理,会导致板子出现死机现象?或者通信不上?

2017-12-13 08:36:44

Mini Linux EMMC

2023-03-28 13:06:25

ARM异常处理:只要正常的程序流被暂时中止,处理器就进入异常模式。例如响应一个来自外设的中断。在处理异常之前,ARM内核保存当前的处理器状态,这样当处理程序结束是可以恢复执行原来的程序。注意:如果

2020-04-20 10:52:02

一、stm32的中断和异常 Cortex拥有强大的异常响应系统,它能够打断当前代码执行流程事件分为异常和中断,它们用一个表管理起来,编号为0~15为内核异常,16以上的为外部中断,这个表就是

2021-08-16 06:19:00

异常是能够引起程序流偏离正常流程的事件,当异常发生时,正在执行的程序就会被挂起,处理器转而执行一块与该事件相关的代码(异常处理)。事件可以是外部输入,也可以是内部产生的,外部产生的事件通常被称作中断

2021-10-11 10:15:51

一、ARM处理器之中断与异常CPU被中断的方式有指令不对、数据访问有问题、Reset信号等这称为异常,还有中断源:按键、定时器、网路数据等称为中断,中断处于一种异常体系,对于异常,首先需要我们保存

2022-05-30 09:46:26

纰漏,请给予指正,谢谢。 一.异常分类(1)复位异常 当CPU刚上电时或按下reset重启键之后进入该异常,该异常在管理模式下处理。(2)一般/快速中断请求 CPU和外部设备是分别独立的硬件执行单元

2018-05-10 10:58:33

1、AArch64异常和中断处理的定义异常是指需要特权软件(异常处理程序)执行某些操作以确保系统顺利运行的条件或系统事件。它们会导致执行流程中断。区分异常和中断的一种方法是:异常是一个事件(分支或

2022-05-23 15:51:36

中断异常(SWI)和未定义异常(Undefined interrupt),CPU内部只有这几个异常发生时其才会跳转到异常向量表(即中断向量)处执行特定的代码。 所有连接在中断处理器上的设备产生的中断

2022-05-30 09:23:57

关于异常处理,分为三部分:ARM异常和模式:core处理异常时的操作,几种模式介绍。Vector table:异常优先级lr偏移:几种异常如何返回异常和中断处理简介在嵌入式系统中异常处理是核心之一

2021-12-14 09:23:07

一、异常(Exception)异常是理解CPU运转最重要的一个知识点,几乎每种处理器都支持特定异常处理,中断是异常中的一种。有时候我们衡量一个操作系统的时候实时性就是看os最短响应中断时间以及单位

2022-08-18 15:26:04

CPSR。 (2)使用LR恢复PC(LR保存的是产生中断处的下一条指令地址) 2、FIQ,IRQ或Prefect Abort(预取异常)处理返回的办法为 SUBS PC, LR, #4 说明

2022-04-26 09:29:21

uCOS-III(15)中断管理异常与中断中断延迟中断延迟发步代码中断延迟发布任务初始化异常与中断异常是指任何打断处理器正常执行,并迫使处理器进入一个由有特权的特殊指令执行的事件。异常通常可以分为

2022-02-18 07:45:44

驱动-异常处理结构、中断处理结构

2012-10-26 21:25:20

本文在分析标准Linux 内核的软中断机制的演化以及实现原理的基础上,提出并实现了一个面前嵌入式Linux 系统的软中断技术。该技术为嵌入式系统开发提供一个统一的中断处理框架

2009-08-03 11:20:17 16

16 通过基于立宇泰S3C44B0X 开发板的BSP 移植调试,阐述了VxWorks 的异常中断处理机制,实现了VxWorks 基于S3C44B0X 处理器的中断处理,并以外部中断EINT4/5/6/7为例分析了中断的响应过程,

2009-09-03 11:25:12 17

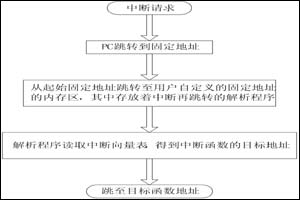

17 摘要:本文首先简要概述了ARM处理器的异常中断种类、响应和返回过程;然后重点讨论了中断解析程序的原理和实现,并分别给出了普通中断和向量中断的处理示例流程图和详细

2006-03-11 12:18:54 760

760

s3c2410中断程序在此要注意的是区别中断向量表和异常向量表。中断发生后总是从IRQ 或者FIQ 异常

2008-09-11 18:49:40 2188

2188 Linux 2.6 中断处理原理简介

中断描述符表(Interrupt Descriptor Table,IDT)是一个系统表,它与每一个中断或异常向量相联系,每一个向量在表中存放的是相应的中断或

2010-02-05 10:52:28 761

761 在C++中,无论何时在处理程序内捕获一个异常,关于该异常来源的信息都是不为人知的。异常的具体来源可以提供许多更好地处理该异常的重要信息,或者提供一些可以附加到

2010-07-15 09:44:53 1869

1869 一.ARM处理器异常及其对应的模式当一个异常发生时,ARM处理器总是切换到ARM状态(即非Thumb状态)。Thumb指令集没有包含进行异常处理时需要的一些指令

2011-04-18 08:34:05 2379

2379

1、中断的种类 由CPU外部产生的中断(interrupt) 由专设指令(如INT)产生的陷阱 (trap)由CPU本身在执行指令时产生的异常(exception) 2、X86 CPU对中断的硬件支持 引入了门(gate) 门的

2011-11-03 22:36:32 54

54 异常主要是从处理器被动接受的角度出发的一种描述,指意外操作引起的异常。而中断则带有向处理器主动申请的意味。但这两种情况具有一定的共性,都是请求处理器打断正常的程序

2011-12-06 16:45:46 49

49 WindowsCE异常和中断服务程序,中断和异常都是异步发生的事件,当该事件发生,系统将停止目前正在执行的代码转而执行事件响应的服务程序。

2012-01-04 15:37:34 1491

1491 微机原理--中断和异常

2016-12-12 22:07:22 0

0 ARM体系中的异常中断及其应用

2017-09-22 16:51:52 4

4 3.4 异常中断处理 异常或中断是用户程序中最基本的一种执行流程和形态。这部分主要对ARM架构下的异常中断做详细说明。 ARM有7种类型的异常,按优先级从高到低的排列如下:复位异常(Reset

2017-10-18 13:29:56 1

1 所示。 图11.63 SWI指令的编码格式 软中断指令SWI(Software Interrupt)用于使处理器产生软中断异常

2017-10-19 09:32:58 0

0 软中断指令产生软中断,处理器进入管理模式 BKPT断点中断指令处理器产生软件断点 9.5.1 软中断指令SWI 1.指令编码格式 软件中断指令SWI(Software Interrupt)用于产生软中断

2017-10-19 10:11:32 1

1 本文从Linux内核几种软中断机制相互关系和发展沿革入手,分析了这些机制的实现方法,给出了它们的基本用法。 软中断概况 软中断是利用硬件中断的概念,用软件方式进行模拟,实现宏观上的异步执行效果。很多

2017-11-02 11:01:58 0

0 所谓异常就是正常的用户程序被暂时中止,处理器就进入异常模式,例如响应一个来自外设的中断,或者当前程序非法访问内存地址都会进入相应异常模式。

2017-11-02 12:57:26 17727

17727

当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理处执行。当异常中断处理程序执行完成后,程序返回到发生中断指令的下一条指令处继续执行。在进入异常中断处理程序时,要保存被中断程序的执行线程。从中断处理程序退出时要恢复被中断程序的执行现场。

2017-12-16 08:57:03 4440

4440 本文介绍A了RM S3C4510B系统 的 异常中断 机制,包括异常中断的分类,响应与返回;中断处理程序的安装与调用;SWI,IRQ中断的实例与关键代码。随着人们对于电子产品的要求越来越高

2018-02-03 05:32:01 1561

1561

ARM中异常中断的类型问题分析总结 一、ARM中异常中断的类型: 异常中断名称 含义 复位(Reset) 当处理器复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位

2018-04-05 10:51:00 1148

1148 SH-3的中断处理方式与一般处理器不同,没有固定的中断向量表,比较灵括,用户可以在存储器中建立上述仅是对P09702的基本应用。通过该文介绍的方法,并结合SSDl303的指令集,读者将能够对P09702应用自如。一个处理异常事件(Exeeplaonevents)的程序结构,作为中断向量表。

2018-04-08 11:25:02 1095

1095

任何一种中断模式都可以通过手动的修改cpsr的值来进入。但是User和System模式是仅有的2个不能由相应中断进入的模式,换句话说,我们必须要通过手动修改cpsr才能进入。

2018-06-25 10:49:01 4413

4413

1. 在汇编中保存现场,然后调用C语言编写的中断处理程序,任务处理完成之后,再返回到汇编中恢复现场,并返回到断点。其中C语言编写的中断处理程序,通过switch语句对INTOFFSET进行判断,然后散转执行对应的服务函数。

2018-11-15 16:17:02 817

817 器核的接口紧密相连,可以实现低延迟的中断处理和有效处理地处理晚到的中断。嵌套向量中断控制器管理着包括核异常等中断。

2018-11-16 15:35:40 7627

7627

ARM体系结构中,存在7种异常处理。当异常发生时,处理器会把PC设置为一个特定的存储器地址。这一地址放在被称为向量表(vector table)的特定地址范围内。向量表的入口是一些跳转指令,跳转到专门处理某个异常或中断的子程序。

2019-03-20 10:25:32 7

7 中断是指在CPU正常运行期间,由于内外部事件或由程序预先安排的事件引起的CPU暂时停止正在运行的程序,转而为该内部或外部事件或预先安排的事件服务的程序中去,服务完毕后再返回去继续运行被暂时中断的程序。Linux中通常分为外部中断(又叫硬件中断)和内部中断(又叫异常)。

2019-05-05 15:30:38 564

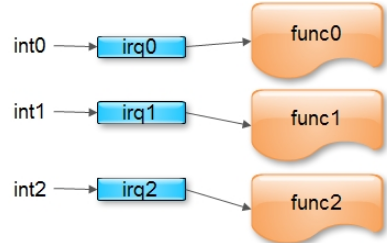

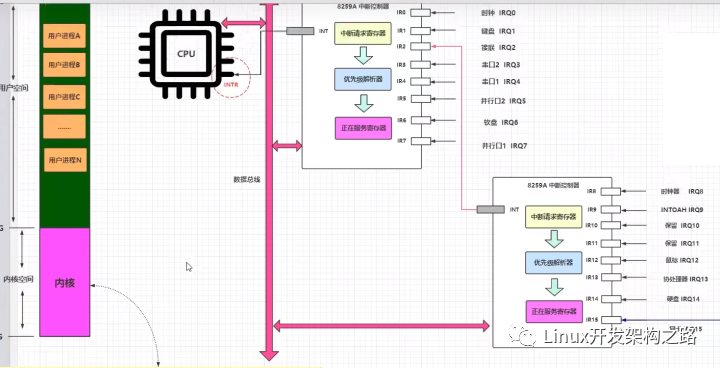

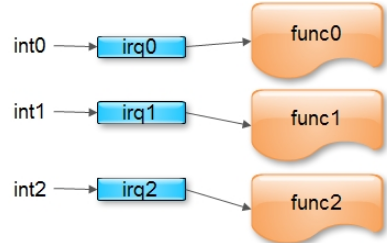

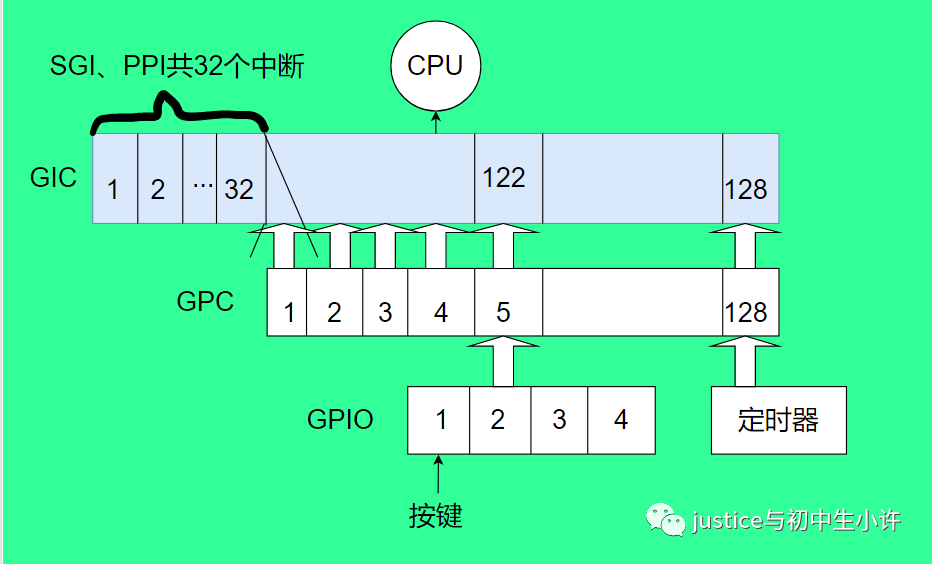

564 linux内核将所有的中断统一编号,使用一个irq_desc[NR_IRQS]的结构体数组来描述这些中断:每个数组项对应着一个中断源(可能是一个中断,也可能是一组中断),记录了中断的入口处理函数(不是用户注册的处理函数)、中断标记,并提供了中断的底层硬件访问函数(中断清除、屏蔽、使能)。

2019-05-07 11:13:56 875

875 在硬件上,中断源可以通过中断控制器向CPU提交中断,进而引发中断处理程序的执行,不过这种硬件中断体系每一种CPU都不一样,而Linux作为操作系统,需要同时支持这些中断体系,如此一来,Linux中就

2019-05-08 13:49:02 543

543 在Linux中断子系统(generic irq)出现之前,内核使用__do_IRQ处理所有的中断,这意味着__do_IRQ中要处理各种类型的中断,这会导致软件的复杂性增加,层次不分明,而且代码的可重用性也不好。

2019-05-10 10:56:09 1325

1325 在前一个专题里曾分析过所有IRQ中断处理流程,经过SAVE_ALL保存硬件环境后,都会进入do_IRQ()进行处理,今天接着分析do_IRQ()处理的相关东西.分为两部中断处理程序与软中断两个大的部份进行介绍.

2019-05-10 10:57:43 2274

2274 最简单的中断机制就是像芯片手册上讲的那样,在中断向量表中填入跳转到对应处理函数的指令,然后在处理函数中实现需要的功能。

2019-05-14 13:49:18 2139

2139

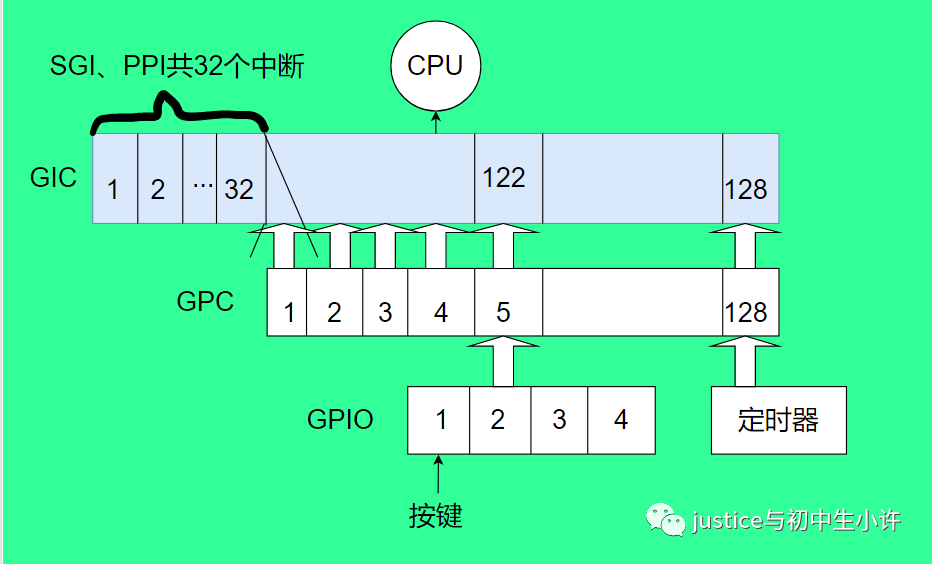

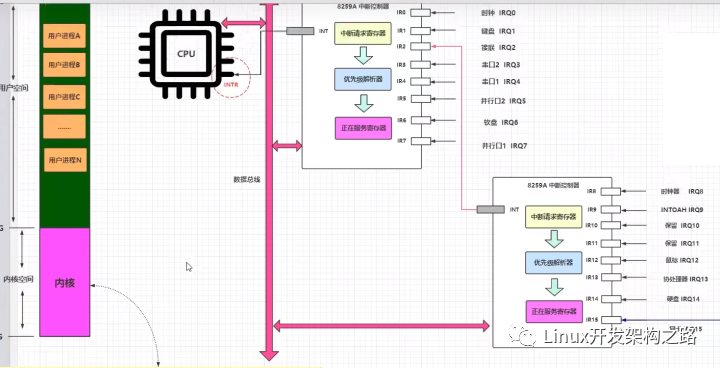

在linux内核中,每一个能够发出中断请求的硬件设备控制器都有一条名为IRQ的输出线。所有现在存在的IRQ线都与一个名为可编程中断控制器的硬件电路的输入引脚相连,上次讲到单片机的时候,我就讲到了单片机中断的一些概念。我们现在来看一幅图,更好说明一个问题

2019-05-14 18:10:00 0

0 当ARM异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。当异常中断处理程序执行完成后,程序返回到发生中断指令的下条指令处执 行。在进入异常中断处理程序时,要保存被中断程序的执行现场,从异常中断处理程序退出时,要恢复被中断程序的执行现场。

2020-06-17 10:05:12 7044

7044 外部中断请求(IRQ) 当处理器的外部中断请求引脚有效,而且CPSR的寄存器的I控制位被清除时,处理器产生外部中断请求异常中断。系统中个外设通过该异常中断请求处理服务。

2020-08-27 14:21:29 2354

2354 一、异常(Exception)异常是理解CPU运转最重要的一个知识点,几乎每种处理器都支持特定异常处理,中断是异常中的一种。有时候我们衡量一个操作系统的时候实时性就是看os最短响应中断时间以及单位时间内响应中断次数

2020-12-24 18:43:44 1094

1094 设置中断向量表 3.2 开启中断设置 3.3 初始化timer 3.4 开启中断 3.5 中断处理 4.测试及校验 5.总结 1.本文说明 任何时候,中断和异常的产生都是十分值得关注的,这些将破坏程序

2021-01-07 10:30:37 2354

2354 异常是能够引起程序流偏离正常流程的事件,当异常发生时,正在执行的程序就会被挂起,处理器转而执行一块与该事件相关的代码(异常处理)。事件可以是外部输入,也可以是内部产生的,外部产生的事件通常被称作中断

2021-10-12 17:14:18 4165

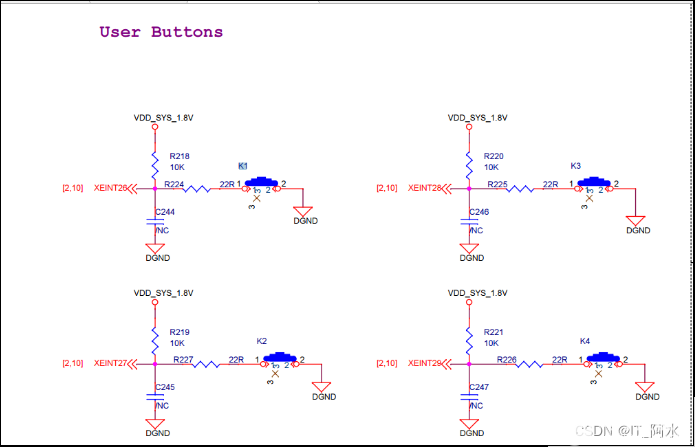

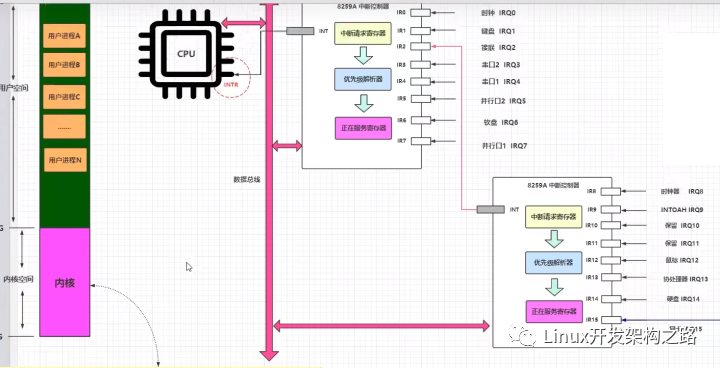

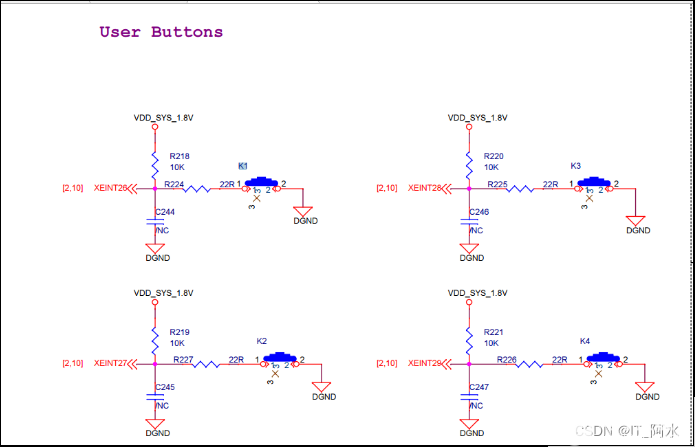

4165 用过STM32的大概都知道,基本每个GPIO管脚都支持中断模式,这样在检测外部插入一个硬件设备时,通过GPIO管脚电平中断就非常方便。那么AM3354的片子是否支持GPIO管脚电平中断呢?答案是肯定

2021-11-01 16:57:32 4

4 一、简介 PIC24EP64GP204的中断向量表包含7个不可屏蔽陷阱向量和多达246个中断源,每个中断源都有自己的中断向量,每个中断向量都包含一个24位宽的地址。每个中断向量单元中编程

2021-11-16 12:21:00 0

0 STM32中断应用中断知识介绍STM32 中断应用概览异常NVIC优先级定义中断知识介绍STM32 中断应用概览STM32 中断非常强大,每个外设都可以产生中断。异常F103 在内核水平上搭载

2021-12-04 17:21:05 9

9 在Cortex‐M0内核上搭载了一个异常响应系统,支持众多的系统异常和外部中断。其中,编号为1-15的对应系统异常,大于等于16的则全是外部中断,优先级的数值越小,则优先级越高。除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。

2022-06-01 14:41:41 3613

3613 在一个系统中,中断时常发生,而且线程调度也是由一个硬件定时器时时刻刻发出中断来支撑的。可以说中断就是linux系统的灵魂。

2023-06-23 14:22:00 331

331

如果异常的优先级高于当前执行优先级,则可以先发制人当前执行。 当一个异常优先于另一个异常时,这些异常被称为嵌套异常。

2023-07-24 09:57:38 1131

1131

正确处理,处理器可能会崩溃或数据损毁。ARM处理器有七种异常模式,即:重置模式、用户模式、FIQ模式、IRQ模式、监督模式、中断模式和异常模式。 1. 重置模式 当ARM处理器启动时,它将进入重置模式。在这种模式下,处理器处于其最初状态

2023-09-05 16:22:25 2036

2036 Cortex-M 内核中断/异常系统、中断优先级/嵌套 详解

2023-09-27 15:29:36 674

674

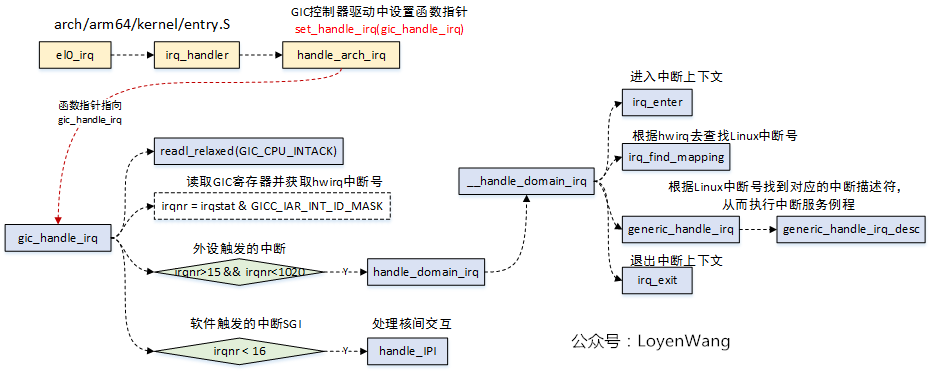

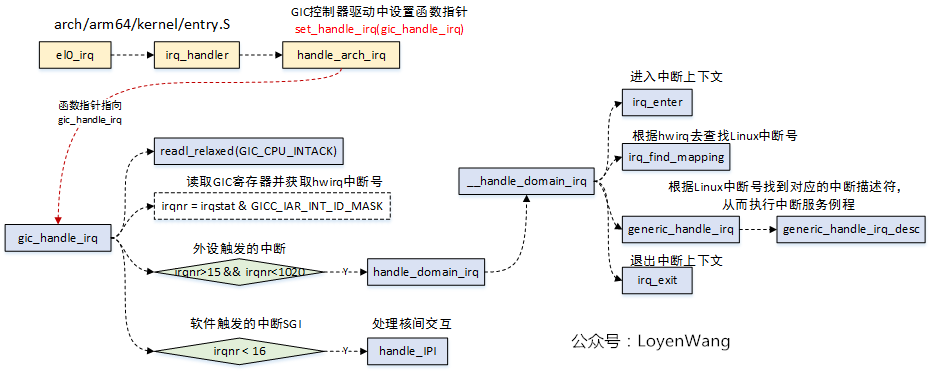

Arch-speicific代码分析 中断也是异常模式的一种,当外设触发中断时,处理器会切换到特定的异常模式进行处理,而这部分代码都是架构相关的;ARM64的代码位于 arch/arm64

2023-09-28 15:27:35 275

275

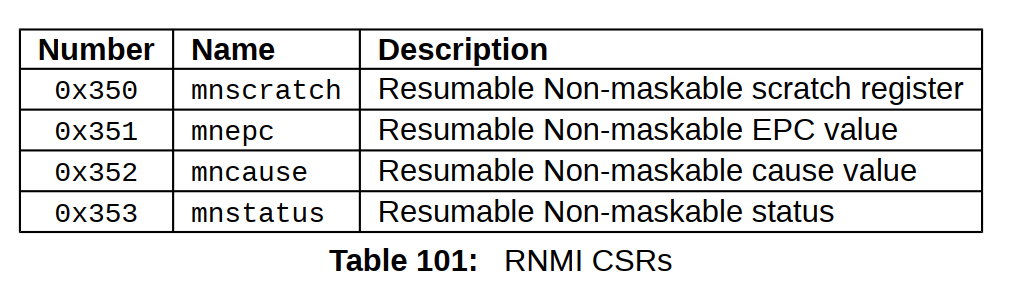

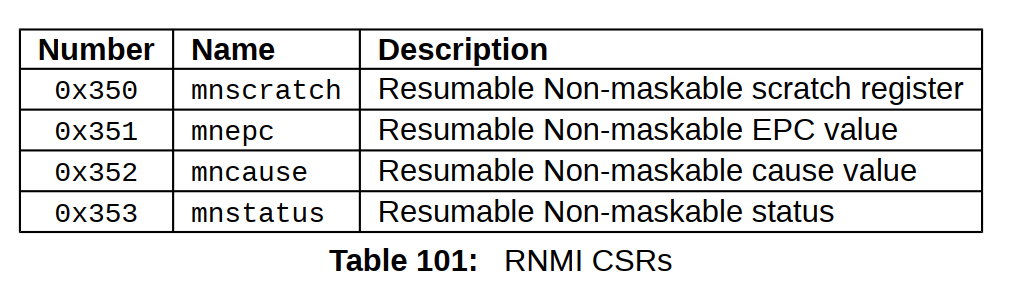

mstatus.mie 寄存器来禁用。 Handler Addresses NMI 有一个关联的异常陷阱处理程序地址。该地址由外部输入信号设置。 RNMI CSRs 这些 M 模式 CSR 启用可恢复非屏蔽

2023-10-08 10:05:30 415

415

当异常中断发生时,程序将当前执行指令的下一条指令的地址存入新的异常模式的链接寄存器LR中(R14_<mode>),以便程序在异常处理完后,能正确返回原程序。

2023-10-18 17:25:43 302

302 情况时及时响应。这些异常情况包括中断、陷阱、系统调用等。在本文中,我们将介绍ARM处理器的中断源以及对异常中断的响应过程。 一、ARM处理器的中断源 1.时钟中断 时钟中断是ARM处理器最基本的中断源之一。ARM处理器内置一个时钟,用来控制其内部的

2023-10-19 16:35:59 675

675 ARM中的异常中断是如何实现进入中断程序的?如何进入呢? 在计算机系统中,异常和中断是两个常见的概念。 在ARM中,异常和中断的主要目的是帮助处理器响应与系统操作相关的事件。 由于处理器必须同时执行

2023-10-19 16:36:11 481

481 中断处理需要软件和硬件配合完成,GICv3根据中断分组情况以及系统当前运行的异常等级确定中断是以IRQ还是FIQ触发。 CPU通过设置SCR_EL3.IRQ和SCR_EL3.FIQ确定IRQ和FIQ

2023-11-07 17:43:16 252

252

,也可能是其它的,但是肯定关于此时CPU状态的。)然后跳转到异常向量 表入口处执行中断处理流程 。 2-执行中断处理流程 fiq_aarch64 函数主要

2023-11-07 17:48:25 368

368 去继续运行被暂时中断的程序。Linux中通常分为外部中断(又叫硬件中断)和内部中断(又叫异常)。 软件对硬件进行配置后,软件期望等待硬件的某种状态(比如,收到了数据),这里有两种方式,一种是轮询(polling):CPU 不断的去读硬件状态。另一

2023-11-09 16:46:26 223

223

LInux 操作系统中断 什么是系统中断 这个没啥可说的,大家都知道; CPU 在执行任务途中接收到中断请求,需要保存现场后去处理中断请求!保存现场称为中断处理程序!处理中断请求也就是唤醒对应的任务

2023-11-10 11:29:49 227

227

LInux 操作系统中断 什么是系统中断 这个没啥可说的,大家都知道; CPU 在执行任务途中接收到中断请求,需要保存现场后去处理中断请求!保存现场称为中断处理程序!处理中断请求也就是唤醒对应的任务

2023-11-13 11:36:10 337

337

ARM中断的实现是通过中断控制器和异常模式实现的。ARM处理器通过中断控制器来接收和处理外部的中断信号,而异常模式用于处理内部的异常事件。本文将详细介绍ARM中断的原理和实现方式。 一、ARM中断

2024-01-05 15:18:11 206

206

正在加载...

电子发烧友App

电子发烧友App

评论