从本质上说,PLC其实就是一套已经做好的单片机(单片机范围很广的)系统。

2016-02-22 13:50:34 12486

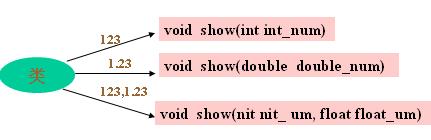

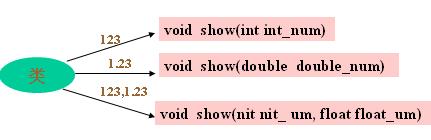

12486 直观的说,就是向不同的对象发送一个消息,不同的对象在接收消息以后有不同的行为;函数重载和运算符重载都是多态现象。

2022-10-25 17:32:59 317

317

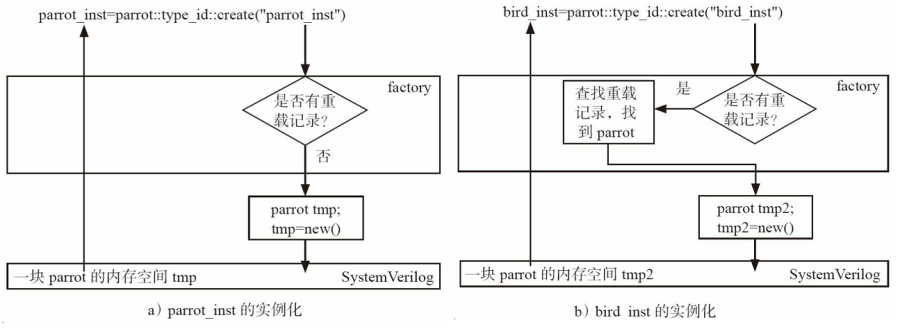

SystemVerilog中多态能够工作的前提是父类中的方法被声明为virtual的。

2022-11-28 11:12:42 466

466 SystemVerilog中可以将类属性声明为常量,即“只读”。目的就是希望,别人可以读但是不能修改它的值。

2022-11-29 10:25:42 1643

1643 在编程语言和类型论中,多态(英语:polymorphism)指为不同数据类型的实体提供统一的接口。多态类型(英语:polymorphic type)可以将自身所支持的操作套用到其它类型的值上。

2023-09-20 17:18:40 310

310 在 SystemVerilog 中,联合只是信号,可通过不同名称和纵横比来加以引用。

2023-10-08 15:45:14 593

593

SystemVerilog 的VMM 验证方法学教程教材包含大量经典的VMM源代码,可以实际操作练习的例子,更是ic从业人员的绝佳学习资料。SystemVerilog 的VMM 验证方法学教程教材[hide][/hide]

2012-01-11 11:21:38

SystemVerilog有哪些标准?

2021-06-21 08:09:41

官方的一个systemverilog详解,很详细。推荐给打算往IC方面发展的朋友。QQ群374590107欢迎有志于FPGA开发,IC设计的朋友加入一起交流。一起为中国的IC加油!!!

2014-06-02 09:47:23

官方的一个systemverilog详解,很详细。推荐给打算往IC方面发展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本语法以及和verilog语言之间的区别。

2015-04-01 14:24:14

里面有不同spi模块的时序图距离,相互对比才更清晰。

2021-01-27 21:58:08

引言:花半秒钟就看透事物本质的人,和花一辈子都看不透事物本质的人,注定是截然不同的命运做开发也一样,如果您能看透开发的整个过程,就不会出现“学会了某个RTOS的开发,同样的RTOS开发换一块开发板

2020-12-07 14:34:34

引言:花半秒钟就看透事物本质的人,和花一辈子都看不透事物本质的人,注定是截然不同的命运做开发也一样,如果您能看透开发的整个过程,就不会出现“学会了某个RTOS的开发,同样的RTOS开发换一块开发板

2020-12-07 16:41:35

引言:花半秒钟就看透事物本质的人,和花一辈子都看不透事物本质的人,注定是截然不同的命运做开发也一样,如果您能看透开发的整个过程,就不会出现“学会了某个RTOS的开发,同样的RTOS开发换一块开发板

2020-11-26 20:00:07

引言:花半秒钟就看透事物本质的人,和花一辈子都看不透事物本质的人,注定是截然不同的命运做开发也一样,如果您能看透开发的整个过程,就不会出现“学会了某个RTOS的开发,同样的RTOS开发换一块开发板

2020-12-02 16:53:27

从内核协议栈转向DPDK/netmap或者XDP的本质原因是什么?

2021-10-25 07:43:12

世界上大部分的科学与工程问题本质上都可以归为两类,即滤波与控制。首先看滤波。滤波是一种信号处理的手段,用以从观测到的信号中提取出你想要的部分或者特征。从数学对应关系上看,滤波就是从一系列观测值中获得

2018-03-02 14:41:00

多态VI例子,希望大家喜欢

2015-06-26 17:16:09

咨询一下,原来点击Read Holding Registers 可以选择其他功能,但是现在添加的都是没有下面这个蓝色框(多态Vi选择器)。请问一下是什么导致这个原因的呢?还有如何复原?

补充内容 (2017-8-18 17:30):

我去专门学习了多态vi的建立和使用,我明白了,其实是我选的vi并不是多态vi。

2017-08-15 17:10:14

多态子VI已断开,运行该VI前必须解决多态子VI的所有错误。外部连接了USB-4711的采集卡,等有正常显示;

2020-01-14 20:35:42

FPGA小白一枚,个人理解的FPGA本质上或者核心就是查找表(LUT),即将所有的函数/方法 转换为固定的查找表(使用DSP除外)。但是为什么所有的文章提到FPGA全部都注重逻辑门呢?其实FPGA本身内部也没有多少物理的逻辑门吧?

2019-05-30 10:53:46

请对面向对象编程中多态性(polymorphism)的概念以及多态性对代码可重用的意义进行阐述。解析:在面向对象编程中一般是这样表述多态性:向不同的对象发送同一条消息(!!!obj.func

2019-01-04 15:55:56

多态 VI, 选择 文件(File) »新建(New)从弹出的对话框中, 选择 VI 目录下的 多态 VI 。在新弹出来的对话框中, 就可以为自己的新多态 VI 添加不同的多态实例。 在LabVIEW

2022-05-10 21:04:44

MATPOWER工具本质原理是什么?运行IEEE标准14电网模型的最优潮流计算的方法是什么?

2021-10-21 08:32:48

从Java的角度理解设计模式1:什么是重构 MF在《重构》一书中是这样定义重构的:重构是这样一个过程,在不改变代码外在行为的前提下,对代码作出修改,以改进程序的内部结构。重构

2009-06-19 16:40:31

设计验证相关的公开课!SystemVerilog作为IEEE-1800,将VLSI设计、验证和断言属性集中在一起,是数字超大规模集成电路设计和验证领域最流行的语言。从2006年至今

2013-06-10 09:25:55

大家好,我对一个 round robin 的 systemverilog 代码有疑惑。https://www.edaplayground.com/x/2TzD代码第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

多态子VI,刚看到的,分享给大家,希望对新学者有帮助。。。。。。

2015-12-11 13:50:01

一般情况,一个程序本质上都是由 bss段、data段、text段三个段组成——这是计算机程序设计中重要的基本概念。而且在嵌入式系统的设计中也非常重要,牵涉到嵌入式系统运行时的内存大小分配,存储单元

2021-12-21 07:08:46

为什么多态VI创建出来没有接线端子,线都不能连

2014-07-20 11:55:16

在某大型科技公司的招聘网站上看到招聘逻辑硬件工程师需要掌握SystemVerilog语言,感觉SystemVerilog语言是用于ASIC验证的,那么做FPGA工程师有没有必要掌握SystemVerilog语言呢?

2017-08-02 20:30:21

创建一个多态VI的方法,分享也是一种快乐!希望在分享中一起成长。。。

2019-03-23 17:04:31

嗨,我怀疑为什么射频发射器本质上是非线性的,而接收器本质上是线性的。 以上来自于谷歌翻译 以下为原文Hi I have a doubt that why RF transmitter are non-linear in nature while receiver are linear in nature.

2018-11-01 09:34:29

如何完备地实现C++多态性?虚函数怎么使用?

2021-04-28 06:44:30

首先总体上谈一谈看法:1、我从不说51是基础,如果我这么说,也请把这句话理解为微机原理是基础。2、对51单片机的操作本质上就是对寄存器的操作,对其他单片...

2021-07-01 07:27:24

内核中的封装继承与多态RT-Thread 虽然是使用面向过程的 C 语言来编写,但是处处都体现了面向对象的编程思想,先前对其感悟不够深,随着编写的程序越来愈多,对其理解也逐步加深。封装封装是一种

2022-04-13 17:41:45

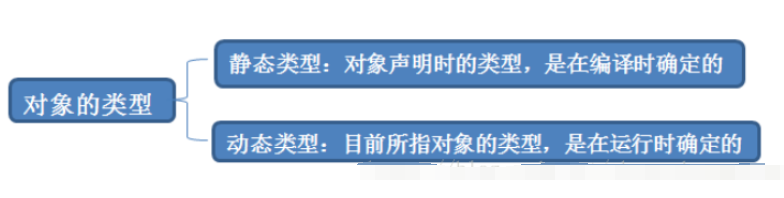

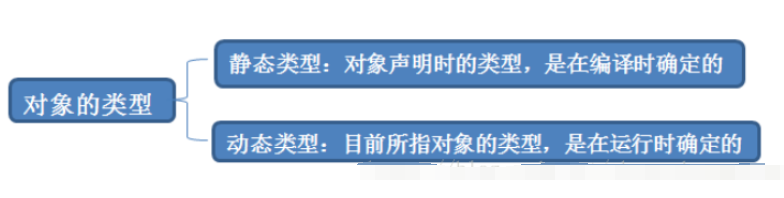

多态(Polymorphism) ,从字面意思上看指的是多种形式,在OOP(面向对象编程)中指的是同一个父类的函数可以体现为不同的行为。在SystemVerilog中,指的是我们可以使用父类句柄来

2022-12-05 17:34:00

有刷电机的优缺点是什么?无刷直流电机是由哪些部分组成的?有刷电机和无刷电机有哪些本质上的区别?

2021-07-20 07:27:29

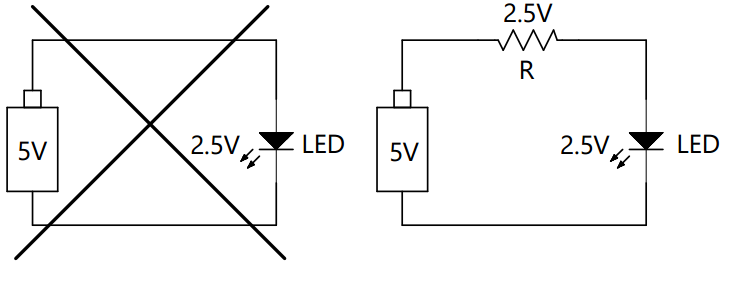

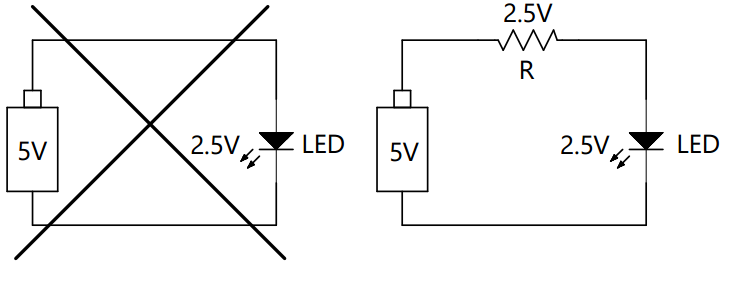

共享了一些电子工程师学习的资料(硬件设计),虽然是一些基本概念的理解,没有长篇大论,但是都讲到本质上了!还有一些设计的经验,论坛上,网络上搜集的。希望大家可以一起学习下。

2013-06-06 13:53:54

TI 的电容式电流隔离技术在很多方面与光耦合器隔离技术不同,其中最突出的当属隔离实施。首先,我们来确定一下我们是否理解“隔离”的真正含义。隔离从本质上讲是一种保护形势,允许两点间的通信,但阻止电流

2022-11-22 06:46:06

和内涵基本切合了智能电网的部分发展趋势,而且丰富了智能电网的内涵,实际上也就成为了智能电网再起步的依托和方向性的指引。 能源互联网和智能电网二者本质上的差异化在哪里? 能源互联网和智能电网有着本质

2016-04-01 09:37:17

什么是多态?多态的必要条件是什么?

2020-11-06 06:22:40

导入SystemVerilog程序包意味着什么?

2020-12-11 06:53:29

SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

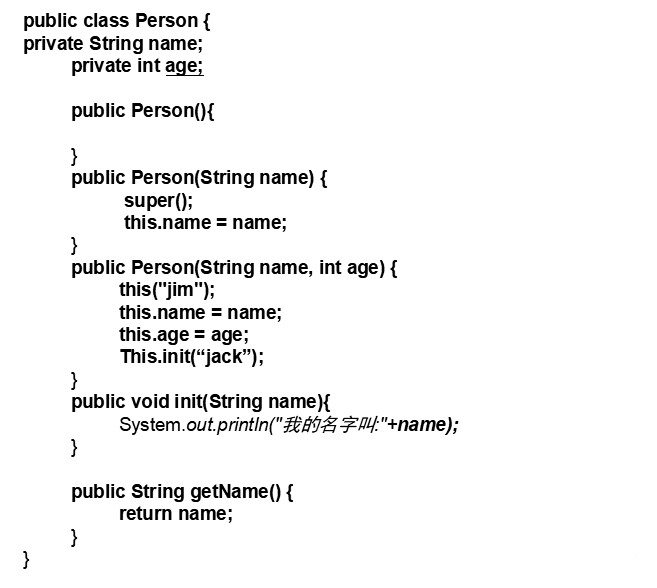

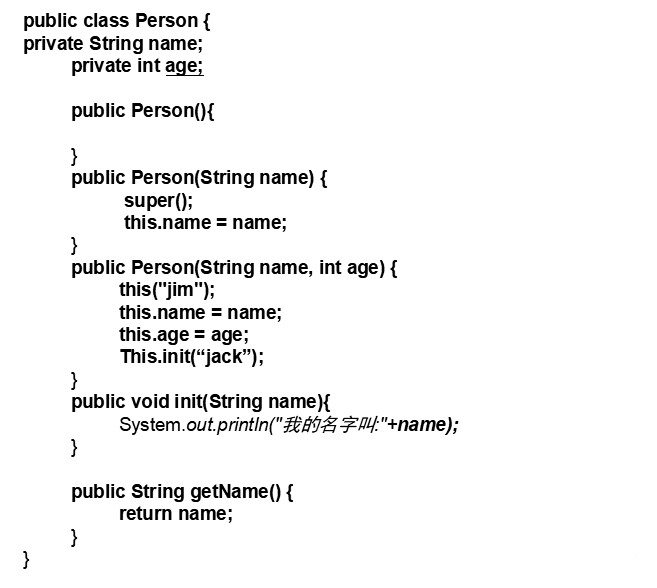

20 Java 中的多态体现在类的继承和实现接口等方面。通过对与多态有关的概念进行归纳比较,从继承和接口两方面对多态的正确实现进行分析,结合实例说明多态性在程序设计中的

2009-09-09 08:51:56 24

24 本文利用形式化的方法对SystemVerilog的指称语义进行研究,采用EBES(extendedbundle event structure)作为抽象模型,以便更好的描述SystemVerilog真并发的特点。我们的主要工作是:首先,

2009-12-22 14:01:07 12

12 如何采用SystemVerilog 来改善基于FPGA 的ASIC 原型关键词:FPGA, ASIC, SystemVerilog摘要:ASIC 在解决高性能复杂设计概念方面提供了一种解决方案,但是ASIC 也是高投资风险的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 什么是方法的重载(多态性)?

在同一个类中至少有两个方法用同一个名字,但有不同的参数。

2009-04-28 14:28:38 1213

1213

就 SystemC 和 SystemVerilog 这两种语言而言, SystemC 是C++在硬件支持方面的扩展,而 SystemVerilog 则继承了 Verilog,并对 Verilog 在面向对象和验证能力方面进行了扩展。这两种语言均支持

2010-08-16 10:52:48 5140

5140 文章主要介绍《VMM for SystemVerilog》一书描述的如何利用SystemVerilog语言,采用验证方法学以及验证库开发出先进验证环境。文章分为四部分,第一部分概述了用SystemVerilog语言验证复杂S

2011-05-09 15:22:02 52

52 多态是 C++ 中面向对象技术的核心机制之一包含静态多态和动态多态它们之间有一定的相似性但是应用范围不同该文论述了这种相似性并重点论述了以模板实现的静态多态的应用范围

2011-06-29 15:41:27 41

41 c++面向对象课程实验指导书题目_数据的共享和保护以及多态性。

2016-01-14 16:25:12 0

0 《Visual C# 2005开发技术》抽象类、多态及接口

2017-02-07 15:17:36 0

0 Java中多态性的实现 什么是多态 面向对象的三大特性:封装、继承、多态。从一定角度来看,封装和继承几乎都是为多态而准备的。这是我们最后一个概念,也是最重要的知识点。 多态的定义:指允许不同类的对象

2017-09-27 10:36:18 9

9 如何基于有限且确定的路由结构来支持多样化服务是当前研究面临的问题,采用路由结构的自组织和自调节来实现路由与业务的自适配,提出一种面向多样化服务定制的多态路由机制。该机制通过自适配网络路由结构

2018-03-13 16:43:53 2

2 由中国社会科学院工业经济研究所、腾讯研究院共同研究编制的《“人工智能+制造”产业发展研究报告》认为,放入“人工智能”的“智能化”过程,与过去制造业追求“自动化”的过程实际上有本质的差异。

2018-06-13 09:03:39 3590

3590 物联网本质上是一个设备网络——从可穿戴健身追踪器到智能工厂车间的连网机器,每一个设备都包含技术,使它能够通过网络发送和接收信息。然而,它真正的力量在于这些连网设备所产生的数据,提供有关它们如何运行、位于何处以及如何使用它们的持续反馈。

2018-12-12 14:15:18 1808

1808 本文档的主要内容详细介绍的是JAVA教程之消息、继承与多态的应用和资料介绍说明主要内容包括了:1 消息,2 访问控制,3 多态机制 ,4 继承机制,5 抽象类、接口与包

2019-01-16 11:02:40 0

0 本文档详细介绍的是C++程序设计教程之多态的详细资料说明主要内容包括了:1.继承召唤多态 (Inheritance Summon up Polymorphism) ,2.抽象编程的困惑

2019-02-22 10:52:00 9

9 学习Java语言的过程中,对于多态的理解是非常关键的,理解了多态也就意味着打开了理解Java各种“抽象”的大门。

2019-09-10 15:50:23 1840

1840 区块链本质上是一个分布式的公共账本。任何人都可以对这个公共账本进行核查,但不存在一个单一的用户可以对它进行控制。

2019-09-27 15:04:23 5016

5016 继承是为了重用父类代码。两个类若存在IS-A的关系就可以使用继承。,同时继承也为实现多态做了铺垫。那么什么是多态呢?多态的实现机制又是什么?请看我一一为你揭开:

2019-10-15 10:05:45 1294

1294

我从去年年底开始进行一些统计数据的汇总,今年继续这么做似乎很合适。总言之,波卡Polkadot项目,包括了Substrate、Grandpa、Cumulus以及一些支持代码,目前共有300,000行代码。这是去年的三倍多,而且这还不包括我们的用户界面以及很多智能合约代码库。

2020-01-04 10:08:05 1624

1624 不用掏出身份证,扫描一下人脸就能甄别出个人的身份信息。但是发现有不少人将ETC与RFID混为一谈,虽然最近各地都在大力开展提升ETC安装率的工作,但两者有着许多本质上的区别;为便于大家理解,兵哥将借着时下ETC的热度,通过ETC与RFID的一些不同的地方,为大家介绍汽车电子身份证——RFID。

2020-03-15 17:09:00 10467

10467 多态意思既是同一个事物的多种形态,用我们C++的专业词语来说就是:一个借口、多种实现方式。

2020-06-29 12:54:04 1733

1733

众所周知,Java的三大特性:封装,继承与多态。本文方便读者朋友们快速理解Java语言中的多态性,以便在面试过程及日常开发中更好的指导具体编程思维,因而自我总结如下:

2020-06-30 17:34:00 1810

1810 手册的这一部分探讨了使用SystemVerilog进行验证,然后查看了使用SystemVerilog的优点和缺点。

2021-03-29 10:32:46 23

23 作者:limanjihe https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一种硬件描述和验证语言

2021-10-11 10:35:38 2042

2042 event是SystemVerilog语言中的一个强大特性,可以支持多个并发进程之间的同步。

2022-10-17 10:21:33 1024

1024 SystemVerilog casting意味着将一种数据类型转换为另一种数据类型。在将一个变量赋值给另一个变量时,SystemVerilog要求这两个变量具有相同的数据类型。

2022-10-17 14:35:40 1960

1960 学习Systemverilog必备的手册,很全且介绍详细

2022-10-19 16:04:06 2

2 SystemVerilog提供了几个内置方法来支持数组搜索、排序等功能。

2022-10-31 10:10:37 1760

1760 SystemVerilog packages提供了对于许多不同数据类型的封装,包括变量、task、function、assertion等等,以至于可以在多个module中共享。

2022-11-07 09:44:45 862

862 SystemVerilog“struct”表示相同或不同数据类型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog中的句柄赋值和对象复制的概念是有区别的。

2022-11-21 10:32:59 523

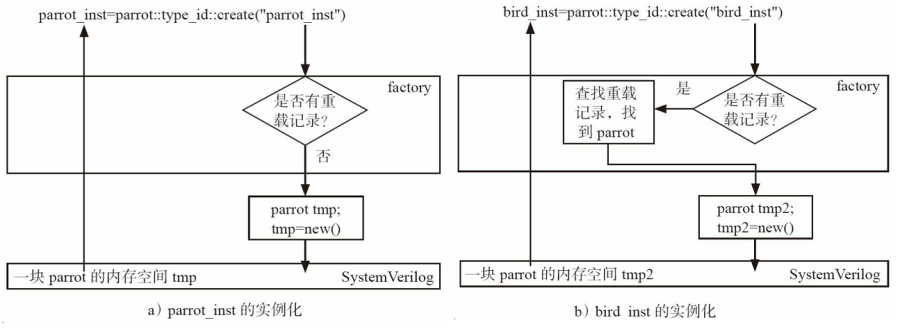

523 要想理解清楚SystemVerilog语言中的Upcasting和Downcasting概念,最好的方式从内存分配的角度理解。

2022-11-24 09:58:15 925

925 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了 C语言 数据类型、结构、压缩

2022-12-08 10:35:05 1262

1262 SystemVerilog中Semaphore(旗语)是一个多个进程之间同步的机制之一,这里需要同步的原因是这多个进程共享某些资源。

2022-12-12 09:50:58 2344

2344 上一篇文章介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-01-21 17:03:00 1519

1519 存在于采购、工程、软件等非硬件人员中,因此,若你是硬件专业人员,这篇文章对于你来说可能是你早已理解过的知识,若你认为以下文字描述的还比较恰当且容易理解,那么当有一名采购同事或软件工程师再问你类似的问题,你可以转发这个给他而非多次重复回答这个问题。

2023-02-17 10:58:06 951

951

数独是一种非常流行的游戏,数独本质上也是一个约束问题,所以我们可以让SystemVerilog的约束求解器来帮助我们解决。 约束求解器的精妙之处就是,我们只描述约束限制,繁重的数值生成工作由工具来帮我们完成。 你只需“既要...又要...”,其他的让下人干吧。

2023-03-08 14:06:00 943

943 factory机制本质是对SystemVerilog中new函数的重载

2023-05-26 14:55:12 579

579

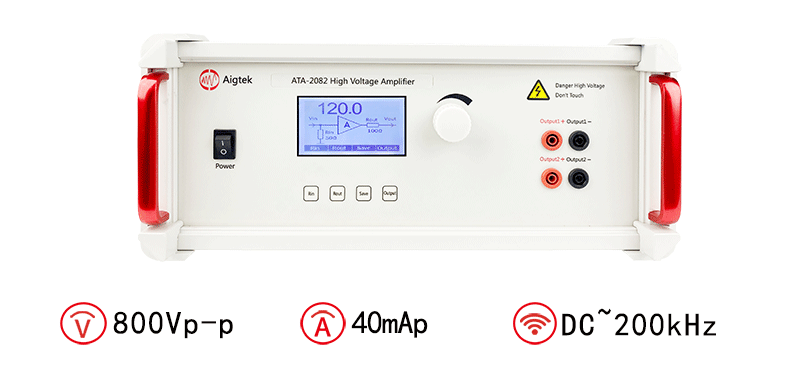

电压放大器和电荷放大器是两种常见的信号放大器,它们在信号处理中都扮演着重要的角色。本质上,电压放大器和电荷放大器在功能和应用上有着很大的不同。虽然它们都涉及到信号放大的过程,但其本质和原理却截然不同

2023-05-30 11:53:18 486

486

在面向对象的编程中,多态性是一个非常重要的概念。

2023-06-08 14:19:10 366

366 本文讲一下SystemVerilog的time slot里的regions以及events的调度。SystemVerilog语言是根据离散事件执行模型定义的,由events驱动。

2023-07-12 11:20:32 775

775

上一篇文章《暗藏玄机的SV随机化》介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-09-24 12:15:30 396

396 谈到SystemVerilog,很多工程师都认为SystemVerilog仅仅是一门验证语言,事实上不只如此。传统的Verilog和VHDL被称为HDL(Hardware Description

2023-10-19 11:19:19 342

342

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

晶振频率和时钟频率本质上有何区别呢?时钟频率有什么作用? 晶振频率和时钟频率是两个相关但又有所不同的概念。下面我们将逐一介绍这两个概念的含义、区别和作用。 首先,我们来了解晶振频率。晶振是一种

2024-01-24 16:11:35 307

307

电子发烧友App

电子发烧友App

评论