寄存器,是集成电路中非常重要的一种存储单元,通常由触发器组成。在集成电路设计中,寄存器可分为电路内部使用的寄存器和充当内外部接口的寄存器这两类。

2023-07-21 16:59:22 2761

2761

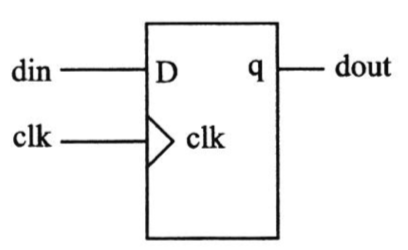

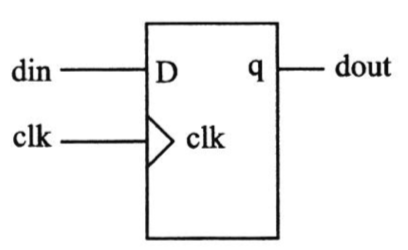

现代逻辑设计中,时序逻辑设计是核心,而寄存器又是时序逻辑的基础,下面将介绍几种常见的寄存器的Verilog设计代码供初学者进行学习理解。

2023-07-27 09:03:59 1899

1899

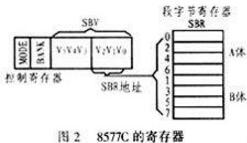

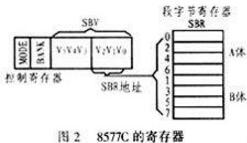

最近在玩74HC595,大学期间也玩过,只是当时没有做笔记习惯,所以好多东西都没有留底稿,最近一直想干点事,那就先从74HC595这个款8位移位寄存器/锁存器(3状态)开始吧,这款芯片有好多厂商在做

2021-12-07 07:40:09

输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器

2011-08-01 16:25:44

我是FPGA的新手想请教一下Verilog中什么时候需要给变量定义寄存器。一开始我以为每个输入、输出都要定义没定义的话默认为一,但是今天看到一段代码输入变量[3:0] key_in并没有定义寄存器。

2017-01-18 19:55:47

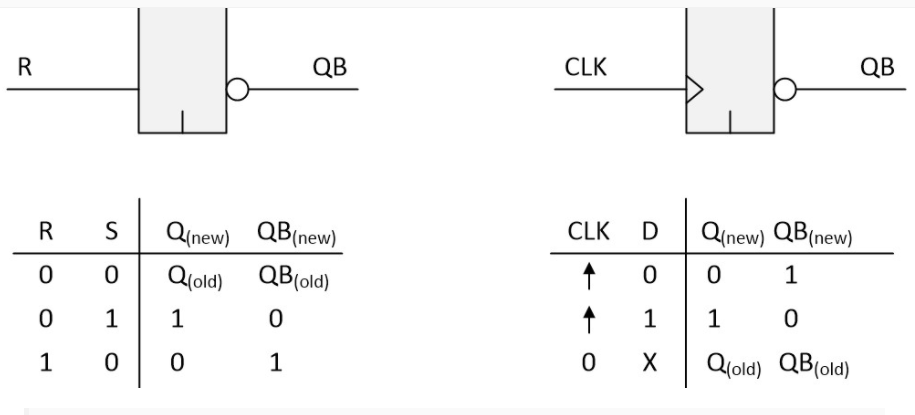

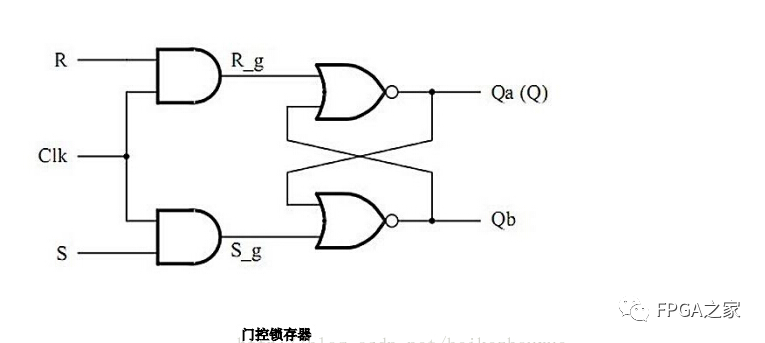

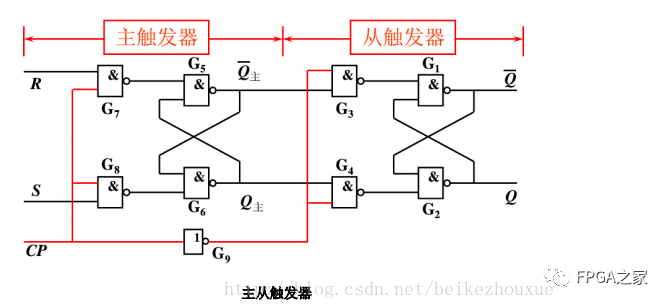

触发器:flipflop锁存器:latch寄存器:register锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时输出才会随着数据输入

2019-08-27 08:30:00

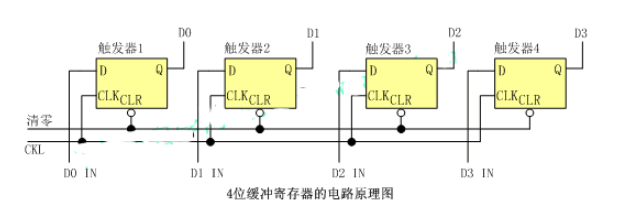

,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。 工程中的寄存器一般按计算机中字节

2018-07-03 11:50:27

存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。 工程中的寄存器一般按计算机中字节的位数设计,所以一般有8位

2019-06-27 04:20:03

本帖最后由 gk320830 于 2015-3-9 20:36 编辑

寄存器电路及应用寄存器1、寄存器寄存器中用的记忆部件是触发器,每个触发器只能存一位二进制码。 按接收

2010-09-18 08:40:09

寄存器 寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。补充:触发器,在数字电路系统中

2022-02-24 06:35:10

最近学了下ARM7,我发现,每个寄存器都有个32位的地址。这么说,对某个寄存器的操作,其实最根本就是对这个地址操作。而寄存器的概念就是有触发器和控制门组成的数字电路。但我越是深究,疑惑就越多。比如:为什么用软件能够改变寄存器的某位的值呢?求各位讨论讨论

2012-04-06 13:48:35

触发器:能够存储一位二值信号的基本单元电路统称为“触发器”。锁存器:一位触发器只能传送或存储一位数据,而在实际工作中往往希望一次传送或存储多位数据。为此可把多个触发器的时钟输入端CP连接起来,用一个

2018-09-11 08:14:45

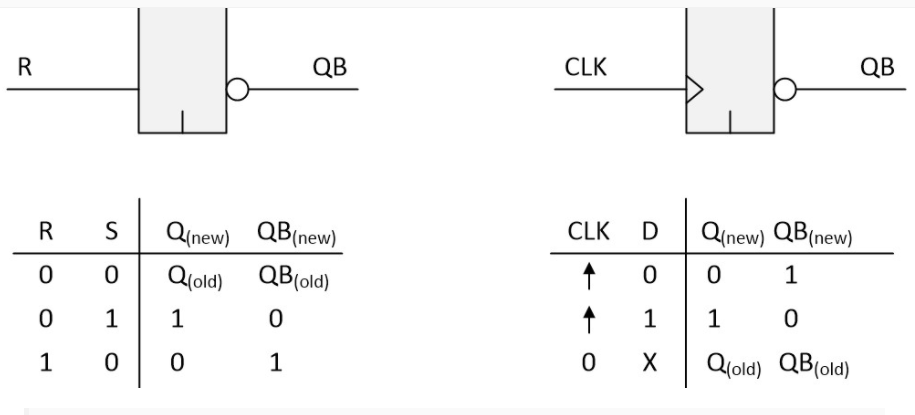

触发器实验1)熟悉常用触发器的逻辑功能及测试方法。2)了解触发器逻辑功能的转换。三.实验内容及步骤 (1) 基本RS触发器逻辑功能测试(2) JK触发器逻辑功能测试(3) D触发器逻辑功能的测试

2009-03-20 10:01:05

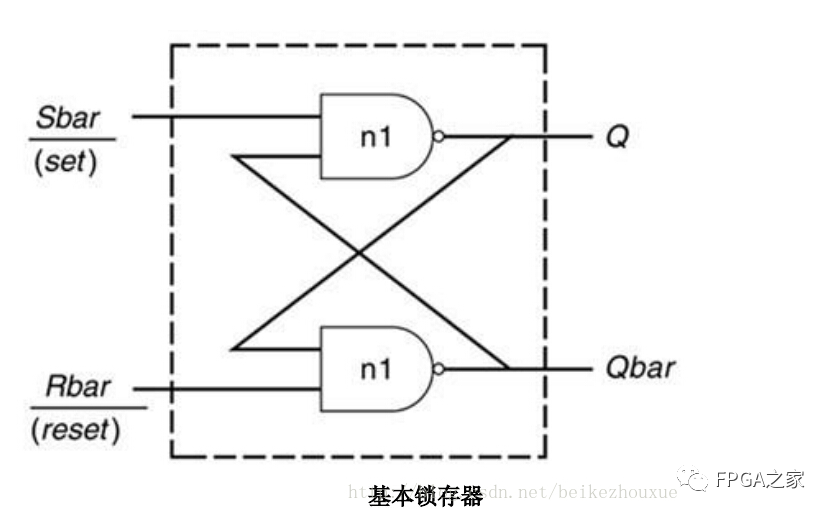

“复位”端。具有置位、复位功能的触发器称为R-S触发器。双稳态触发器可用来构成各种计数器、分频器和寄存器等。射极耦合触发器又称施密特触发器,其原理电路如图2。它也由两级反相器直接耦合而成。第一级反相器

2012-06-18 11:42:43

请问,锁存器的工作原理是什么?

2013-10-15 19:35:26

的数据和运算结果,它被广泛的用于各类数字系统和计算机中。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1

2011-10-09 16:19:46

锁存器的工作原理是什么?锁存器的动态特性及其应用有哪些?触发器的工作原理是什么?触发器的电路结构是如何构成的?

2021-11-03 06:48:50

锁存器和触发器1.什么情况要用到锁存器?状态不能保持?现在的单片机状态都是可以保持的吧2.看到很多产品用施密特触发器作为门极驱动器(栅极驱动器),是隔离的作用还是其他?这种触发器和专用的门极驱动器有哪些异同

2022-03-10 17:52:14

数码管的动态显示截取了部分程序,使用了74hc573锁存器,但是我觉得去掉锁存器程序照样可以执行,那么这里使用锁存器的意义是什么呢?还是说只是用一下没有什么特殊的含义? for( i=0; i

2013-03-11 16:59:52

数码管的动态显示截取了部分程序,使用了74hc573锁存器,但是我觉得去掉锁存器程序照样可以执行,那么这里使用锁存器的意义是什么呢?还是说只是用一下没有什么特殊的含义?

for( i=0

2023-10-26 07:18:07

前言在学习了基本锁存器原理后,剩下就是对各个外设以及对单片机寄存器的相关学习,如果没有看过之前对锁存器原理的讲解的同学,可以回看一下。蓝桥杯基础教程之锁存器操作(非常重要!)学习蓝桥杯必看

2021-12-03 08:05:27

的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2019-04-23 03:35:28

请教下CY8CMBR3xxx系列中的LATCHED_BUTTON_STAT寄存器锁存机制是怎样的?器件是在什么时候

去清除LATCHD_BUTTON_STAT?谢谢。

2024-01-24 07:43:17

今日偶然看到一些知名企业的笔试试题,随便扫描了下,看到有几道关于FPGA/CPLD的题目,小小的编程题,用VerilogHDL或VHDL语言编触发器,脑袋转了一下,模糊似乎清晰,清晰又像浸入模糊

2012-02-22 13:54:40

D触发器中PRN、CLRN区别在Quartus II当中查看RTL视图会有PRN和CLRN(CLR)两个引脚的区别PRN是异步置位,可以将输出Q置为输入D(输出Q立马变成输入D)CLRN(CLR)是异步复位,将输出Q置地。

2022-01-11 06:43:53

(14)FPGA触发器与寄存器区别1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA触发器与寄存器区别5)结语1.2 FPGA简介FPGA(Field

2022-02-23 06:16:56

指标都是有余量的。轻微的违反tSU或者tH并不会发生亚稳态,只是导致触发器的tCO超出器件的规范(spec)。只有当数据的跳变出现在亚稳态捕捉窗口W (见图2中的W,fs级别的时间窗口),才会发生亚稳态

2012-12-04 13:51:18

FPGA如何实现对片外寄存器的读写(Verilog语言)?它与单片机有区别吗?

2016-03-24 09:40:43

操作与具有相同“置位”和“复位”输入的先前SR触发器完全相同。这次的区别是,即使S和R都为逻辑“ 1” ,“ JK触发器”也没有SR锁存器的无效或禁止的输入状态。该JK触发器基本上是一个门控SR触发器

2021-02-01 09:15:31

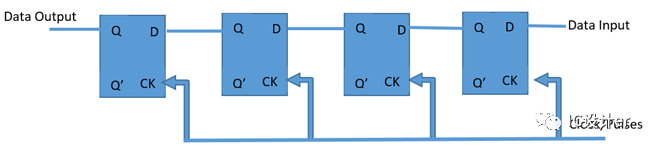

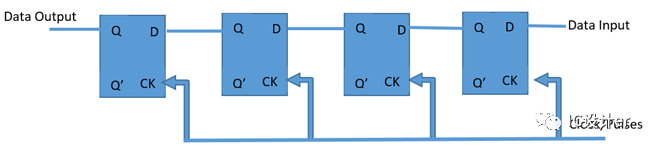

左边一个触发器中原来的数据(F0接收的输入数据D1)。寄存器中的数据依次右移一位。 2、移位寄存器作用 移位寄存器是一种存储器,存在里边的数据可以从低位向高位移动或从高位向低位移动。例如一个8位

2019-06-20 04:20:27

【8-15】端口配置寄存器 32位IDR 数据寄存器 32位 输入ODR 数据寄存器 32位 输出BSRR 置位/复位寄存器 32位BRR 复位寄存器 16位LCKR 锁存寄存器 32位3、常用的IO端口寄存器 CRL CRH IDR ODR4、CRL ...

2022-02-28 06:51:38

STM32时钟分析寄存器:寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成在计算机领域

2021-08-10 06:28:45

山地车的设备配置器中,我看到了触发器输入和触发通道输入的选项。

我可以知道这两者有什么区别,以及使用它们而不是另一个的注意事项吗?

2024-01-24 07:53:07

jk触发器是什么原理jk触发器特性表和状态转换图

2021-02-26 08:18:24

,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。在计算机领域,寄存器是CPU内部的元件,包括通用寄存器、专用寄存器和控制寄存器。寄存器拥有非常高的读写速度,所以在寄存器之间的数据传送非常快。STM32内部的所有寄存器都有唯一

2021-08-10 06:07:57

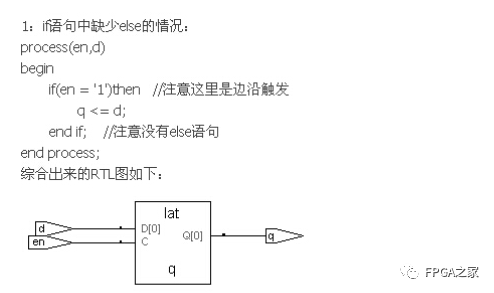

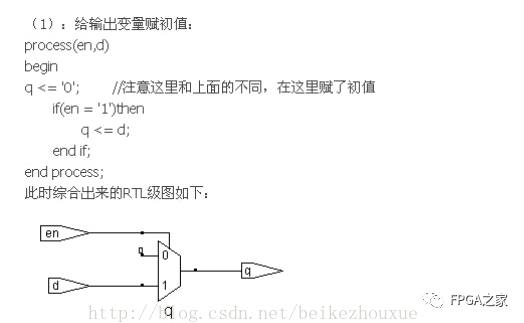

。由引可见,实现“保持不变”的关键在于D寄存器。众所周知,组合逻辑代码是没有D寄存器的,那么它又是如何实现保持不变呢?这个就会用到锁存器了。 上图左边是组合逻辑代码,右边是其电路。为了让信号b保持不变

2020-03-02 00:25:31

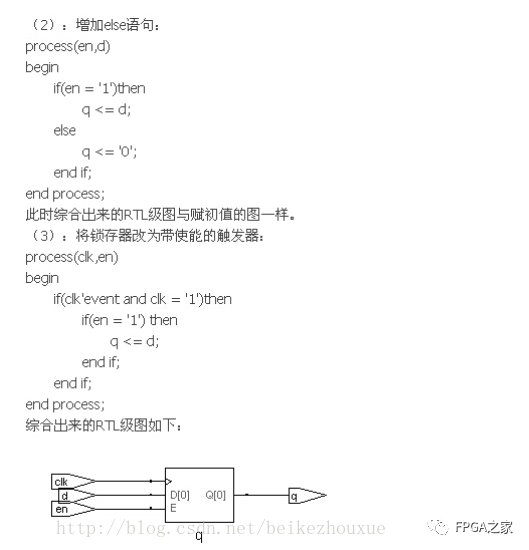

寄存器。 在FPGA设计中建议如果不是必须那么应该尽量使用触发器而不是锁存器。钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳

2018-10-27 22:38:21

2020.3.26_学习笔记两个D触发器 最近发现一个问题,代码中会特地的新建一个D触发器用来锁存信号,让很多人都比较疑惑,明明一个D触发器就可以检测输入是上升沿和下降沿。两个触发器的目的主要

2021-07-30 06:44:48

根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。触发器是一种能够保存1位二进制数的单元电路,是计算机中记忆装置的基本单元,由它可以组成

2019-12-25 17:09:20

你好我是Xylinx的新手,我10年前才使用Altera设计。我需要设计一个使用1GHz时钟速度的电路来同步时钟D-FF和移位寄存器和锁存器。任何FPGA都可以支持这个吗?你能给我一些关于触发器

2020-03-30 08:45:38

光立方必须是74ALS573这种锁存器吗?我现在有这种74hc373d的锁存器能用吗?

2013-11-22 00:18:53

本帖最后由 xvjiamin 于 2021-9-26 20:46 编辑

如图,在编写TDC延时链的时候,结果通过D触发器做锁存。但是出现了红色的不定态,这是为什么?该怎么解决呢?可以看到,信号

2021-09-26 20:46:03

逻辑可构成时序逻辑电路,简称时序电路。现在讨论实现存储功能的两种逻辑单元电路,即锁存器和触发器。双稳态:电子电路中。其双稳态电路的特点是:在没有外来触发信号的作用下,电路始终处于原来的稳定状态。在外

2016-05-21 06:50:08

型触发器的Q输出直接连接到D输入,从而使器件具有闭环“反馈”,则连续的时钟脉冲将使每两个时钟周期使双稳态“切换”一次。在计数器教程中,我们看到了如何将数据锁存器用作“二进制分频器”或“频率分频器”以

2021-02-03 08:00:00

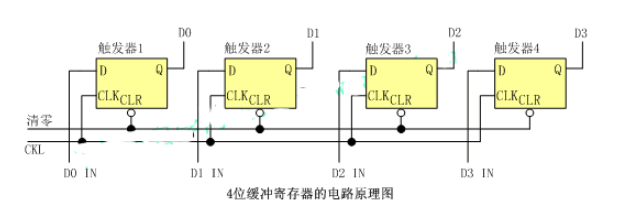

用D触发器设计的四位移位寄存器

2016-06-13 13:05:50

逻辑,应在敏感信号表中列出所有的输入信号;7、所有的内部寄存器都应该可以被复位;8、用户自定义原件(UDP元件)是不能被综合的。一:基本Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器,还有可能被优化掉。二:veril...

2021-07-29 06:10:04

如何用D触发器设计四位移位寄存器。求程序框图

2016-06-13 13:48:29

的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。(2)什么是寄存器映射由于存储器本身没有地址,给存储器分配地址的过程就叫存储器映射,在存储器Block2 这块区域,设计的是片上外设,它们以四个...

2022-02-28 09:36:37

Verilog模型有哪几种?Verilog HDL模型是由哪些模块构成的?如何用Verilog HDL语言描述D型主从触发器模块?

2021-10-19 08:36:32

单片机内部有大量寄存器, 寄存器是一种能够存储数据的电路, 由触发器构成。1.触发器触发器是一种具有记忆存储功能的电路, 由门电路组成。 常见的触发器包括: RS 触发器、 D 触发器和 JK触发器

2022-01-20 07:13:51

`请问锁存器下面3个针脚怎么接线?`

2014-12-28 15:45:25

想做一个基于D触发器的寄存器,结果运行时出现这种情况,请大神指点一下

2019-06-27 10:14:56

一、定时器0/11、控制寄存器TCON为定时器/计数器T0、T1的控制寄存器,同时也锁存T0、T1溢出中断源和外部请求中断源等,TCON格式如下:TCON : 定时器/计数器中断控制寄存器 (可位寻址)]

2021-12-02 08:26:15

Chapter5 锁存器与触发器5.1 基本双稳态电路一、双稳态电路具有0 、1 两种逻辑状态, 一旦进入其中一种状态,就能长期保持不变的单元电路,称为双稳态存储电路,简称双稳态电路。1. 最基本

2021-07-30 06:43:29

晶体管,门电路,锁存器,触发器的理解

2021-01-12 07:55:02

和K输入点连接在一起,即构成一个T触发器。应用场合:时钟有效迟后于数据有效。这意味着数据信号先建立,时钟信号后建立。在CP上升沿时刻打入到寄存器。

2019-06-20 04:20:50

由与非门构成的555定时器触发锁存电路解析

2021-04-07 06:20:04

移位寄存器概要 在数字电路中,移位寄存器(英语:shiftregister)是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或

2019-06-20 04:20:29

移位寄存器概要 在数字电路中,移位寄存器(英语:shiftregister)是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或

2019-06-20 04:20:47

锁存器就是把当前的状态锁存起来,使CPU送出的数据在接口电路的输出端保持一段时间锁存后状态不再发生变化,直到解除锁定。还有些芯片具有锁存器,比如芯片74LS244就具有锁存的功能,它可以通过把一个

2022-03-01 07:00:42

电平触发器和边沿触发器符号

2019-10-18 09:01:09

、BRR五、锁存寄存器 LCKR1、LCKR六、ODR、BSRR、BRR之间的联系与区别**既然ODR寄存器既可以输出高电平也可以输出低电平那么为什么还需要BSRR和BRR呢?****为什么BSRR

2022-01-18 09:15:23

预放大锁存比较器是什么工作原理?运放锁存器的电路结构分析如何使用Spectre预放大锁存比较器进行仿真?

2021-04-08 06:56:02

具有三态输出和施密特触发器输入的八路透明 D 类锁存器 Number of channels (#) 8 Technology Family HCS Supply

2022-12-12 15:16:21

具有三态输出和施密特触发器输入的八路透明 D 类锁存器 Number of channels (#) 8 Technology Family HCS Supply

2022-12-12 15:16:22

具有施密特触发输入和三态输出寄存器的 8 位移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8 Technology

2022-12-12 15:16:26

具有施密特触发输入和三态输出寄存器的汽车类 8 位移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8

2022-12-12 15:16:35

具有输出锁存器的 8 位移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8 Technology Family

2022-12-12 15:18:38

具有输入锁存器的 8 位移位寄存器 Configuration Parallel-in, Serial-out Bits (#) 8 Technology Family

2022-12-12 15:18:38

具有输出锁存器的串行输入移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8 Technology Family

2022-12-12 15:21:52

具有输入锁存器的串行输出移位寄存器 Configuration Parallel-in, Serial-out Bits (#) 8 Technology Family

2022-12-12 15:21:52

具有输入锁存器的移位寄存器 Configuration Parallel-in, Serial-out Bits (#) 8 Technology Family LS

2022-12-12 15:21:53

寄存器与移位寄存器

寄存器是用来寄存数码的逻辑部件,所以必须具备接收和寄存数码的功能。任何一种触发器都可以构成寄存器,每一个触发器存放一位二进

2010-03-12 15:19:40 59

59 本文开始介绍了寄存器分类、特点与用途,其次介绍了触发器的分类与触发器的作用,最后介绍了寄存器和触发器的区别。

2018-04-11 14:39:23 25447

25447

寄存器是由触发器组成的,一个触发器是一个一位寄存器。多个触发器就可以组成一个多位的寄存器。由于寄存器在计算机中的作用不同,从而被命名不同,常用的有缓冲寄存器、移位寄存器、计数器等。下面我们就简单的来介绍下这些寄存器的电路结构及工作原理。

2020-06-19 16:44:45 17323

17323

你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及

2021-01-05 16:03:53 5109

5109

寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

2020-12-31 16:42:41 10613

10613 STM32 第二天寄存器寄存器功能:寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成

2021-12-08 17:36:11 18

18 (14)FPGA触发器与寄存器区别1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA触发器与寄存器区别5)结语1.2 FPGA简介FPGA(Field

2021-12-29 19:41:06 1

1 寄存器 寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。补充:触发器,在数

2022-01-04 10:45:24 9

9 1:锁存器、触发器、寄存器的关联与区别 首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性

2022-12-19 12:25:01 8206

8206 触发器也是单个寄存器,当一个寄存器设计有多个触发器时,可以存储一位,可以容纳更多位数据。最后,移位寄存器是一种用于存储或传输数据的逻辑电路。

2023-01-06 14:22:09 1067

1067 你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及为什么它们都与寄存器有关。

2023-01-30 15:21:15 2666

2666 带输入触发器的 8 位移位寄存器-74HC_HCT597

2023-02-15 19:01:46 0

0 带输入触发器的 8 位移位寄存器-74HC_HCT597_Q100

2023-02-15 19:01:59 0

0 cpu寄存器和存储器的区别 寄存器存在于CPU中,速度很快,数目有限;存储器是内存,速度稍慢,但数量很大。寄存器的功能是存储二进制代码,是由具有存储功能的触发器组合起来构成的。一个触发器可以存储

2023-03-21 15:12:16 866

866 移位寄存器是一种时序逻辑电路,能够存储和传输数据。它们由触发器组成,这些触发器的连接方式使得一个触发器的输出可以作为另一个触发器的输入,具体取决于所创建的移位寄存器的类型。

2023-09-20 10:44:13 2470

2470

正在加载...

电子发烧友App

电子发烧友App

评论