Aurora 是一个很高效的低延迟点对点的串行协议,它使用了GTP收发器。它旨在隐藏GTP的接口细节和开销。

2018-01-26 09:46:59 11614

11614

firmware文件夹下只有ipnc_rdk_fw_m3video.xem3和ipnc_rdk_fw_m3vpss.xem3两个M3核固件更新生成,而DSP核的固件ipnc_rdk_fw_c6xdsp.xe674

2020-08-19 09:41:08

本帖最后由 黎释 于 2017-5-17 16:57 编辑

我在FPGA中调用AURORA_8b10b核时,发现在接受端RX_SRC_RDY_N一直为低电平,也就是说一直在接受数据,可是我在

2017-05-17 16:55:51

小弟最近在调用Aurora 8b/10b IP模块时,在用modelsim功能仿真时,一切正常。 但是直接使用了例化后的example,并将Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

使用ISE 14.1,我试图在Virtex-4 FX中生成一个简单的Aurora 8B / 10B内核。核心似乎生成(生成完整的.vhd函数模型文件),但不会在.vho文件中生成任何代码以实例化到我

2019-03-20 15:43:41

我开发了一个应用程序,包括Userapp,Aurora IP 8b10b v8.3,两个FIFO(Tx和Rx)和sram模块。我使用ISim模拟了总应用程序。我得到了所需的结果。现在,我的疑问

2020-03-30 08:49:04

最近使用V6130T和75T链接,aurora8B10BIP核,ISE14.5.上电以后可以channelup正常,一旦FPGA别的部分开始工作,电流变大了就发现数据出错,有softerror。改变

2015-03-06 10:52:56

现象描述:仿真器直接连接开发板,编译链接下载仿真程序都没有问题,运行正常。生成ldr文件烧写到flash之后无法正常启动。生成和烧写ldr的方法都没有问题,已经回读验证过,板子上的启动管脚状态正常,可能是什么原因?

2018-08-28 11:48:39

你好!我现在在尝试电路板上TMS320C6670 双核驱动调试。发现调试存在问题。当我将.txt放在L2SRAM中时,调试正常。但当我将.txt.放在共享内存中时,出现有的断点无效,及有些判断

2018-06-21 17:12:52

您好!

我们现在遇到这样一个问题:

C6678的电源、时钟、复位已全部完成,并且复位状态信号RESETSTAT也已经拉高,觉得通过这个信号可以看出芯片复位已经完成,但是通过仿真器连接,核0连接不上

2018-06-21 03:03:27

嗨,核纳米板 stm32l432kc 上的 HSE 值是多少?未来:24MHz 晶体但是当我在 cubemx 中初始化默认设置时,它将 HSE 设置为 8 MHz。在船上用户手册中找不到船上 HSE 的价值。

2022-12-28 06:36:15

)在CCS串口栏或其他串口调试工具上可以看到M核的输出信息。04程序实测我们以gpio_led_blink为例,来演示硬件仿真功能。(1)将am62-mcu-m4f0_0-fw放至开发板,这一步必须有

2023-03-31 11:40:45

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

你好, 我正在使用Aurora 8B / 10B v5.3 IP内核,Virtex 5 FPGA用于使用SFP电缆的GB收发器。我使用核心生成器创建了IP核,获得了示例设计(所有文件)。我模拟了示例

2020-04-07 14:52:25

DAP仿真器 BURNER

2023-03-28 13:06:20

,而且不知道怎么把小数生成Hex文件存到ROM里面,于是把数据扩大了2^12倍。之前用产生的余弦函数来试得到的结果是对的,fft之后就是一条线谱。我是用的DSP builder调用fft ip核来做

2016-04-21 20:36:18

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

例程

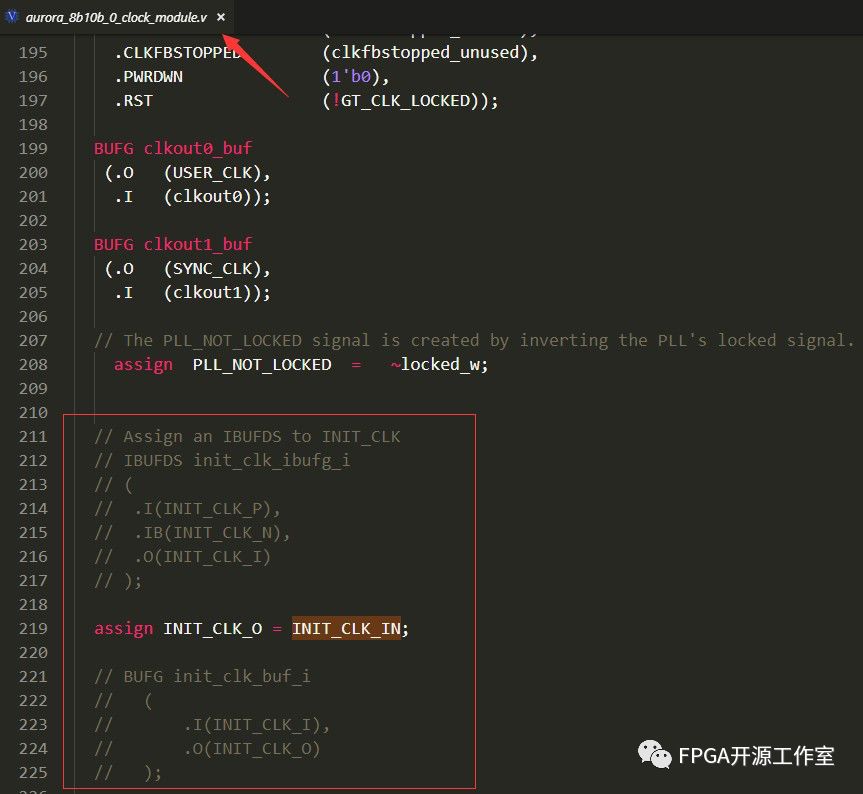

右键点击刚生成的IP,选择“Open IPExample Design”,打开IP对应配置下的测试工程,选择指定路径,自动打开新生成的测试工程。

4、阅读示例工程,仿真分析

工程中包含了时钟

2023-11-17 11:09:22

Vivado:2016.4FPGA:xcvu190Hello,我在两个xcvu190平台之间遇到Aurora 64B66B IP(v11.1)的一些问题。使用x4 GTY通道将IP配置为全双工,成帧

2018-09-28 11:29:48

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

我制作了一个Aurora 64/66项目。 6.25 Gb / s,250 Mhz参考时钟。看一下生成的示例设计。在UCF的示例设计中,我生成了Xilinx工具#50 MHz板时钟约束NET

2020-07-27 12:10:28

本帖最后由 elecfans跑堂 于 2015-9-7 13:54 编辑

一个项目里有IP核rom,想改其中的参数重新生成,结果打开失败,然后我把它移除了,在项目里边新添加不了,提示如下错误

2015-09-07 12:21:59

PCB板上的高速信号需要进行仿真串扰吗?

2023-04-07 17:33:31

最近在做FFT IP核,,走了好多弯路,LISENCE激活过了0034的IP核,通过修改LISENCE.DAT的方法。后来生成FFT的时候卡住,又尝试了关闭quartus_map进程和重装jre

2019-04-03 16:16:21

请问一下,我使用QuartusII 13.0 生成不了Rapid IO IP核,iP核已破解,其他诸如FIR、CIC、NCO等都能正常生成,到底是怎么回事呢?是Quartus版本的问题吗?

2017-07-17 16:23:29

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

创建项目时,我无法添加 touchGFX 生成器,并且在版本 4.16 的发行说明中它说:“TouchGFX 生成器以前可用于具有双核 MCU 的项目尽管尚未支持 H747* 和 H745*。”我还可以获取 touch GFX 软件使用的项目来生成在创建图形应用程序时编程到评估板的二进制文件

2022-12-28 08:33:03

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

在仿真fft ip核时 输出信号一直为0,检查了输入波形,应该没有问题,大家帮忙看看吧输入是由rom里面的mif文件产生的信号。

2017-11-21 10:44:53

我用quartus II调用modelsim仿真fft ip核,仿真结束后我想验证下数据是否正确,结果是:我用matlab生成同样的整形数据,然后用modelsim仿出的结果txt文件与用

2012-09-20 12:48:37

我调用了一个ip核 在下载到芯片中 有一个time-limited的问题 在完成ip核破解之后 还是无法解决 但是我在Google上的找到一个解决方法就是把ip核生成的v文件加到主项目文件中就是上面

2016-05-17 10:28:47

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

modelsim 仿真 altera IP核(ROM,RAM实例)急求大神们ROM和RAM 的综合仿真代码

2015-11-19 21:02:57

modelsim仿真fftip核方法:重点有3:1,添加库文件方式正确2,添加编译文件,要包括.vo文件3,仿真时要重新再添加一下库文件

2013-05-12 14:05:12

本帖最后由 liu1032042013 于 2017-5-3 22:16 编辑

使用quartus 12.1生成NCO IP 核失败,进度条一直卡着不动,经百度得网友分享的方法,成功解决问题

2017-05-02 21:39:22

quartus 11.0 IP核的simulation如果勾选 就生成不出IP核出错,但是不选的话就没办法RTL仿真 求大神问题原因或者解决方法

2016-11-25 20:39:45

用的xilinx的FFT 9.1版本的ip核 , 仿真出来的结果和我MATLAB算出来的结果差的很多,也没有倍数关系,scaled因数改了好几次,没有溢出,波形大致相同,但是数值上差的太多,已经弄了快两周了,求做过这个的讲讲经验。

2018-07-10 16:16:31

相关、下载仿真。添加信号:时钟配置:仿真波形如下,分析与上一篇是一样的,这里不再详细说明。对于SignalTap Ⅱ和Modelsim的使用经过这几个IP核的学习应该算是熟悉了,其实使用是次要的,主要

2016-10-11 22:24:16

Aurora最新实验室记录视频。注意,右上角相机为老式磁带相机,时间轴对不准

2014-01-29 12:18:28

你好!我正在使用Aurora 64/66示例设计项目(4个通道),每个clk发送8帧。当使用我的Vivado调试工具从我的K7开发板获取RX数据时,在最后一帧(如

2019-04-10 09:57:31

用 quartus 生成一个ddr2的ip核,选择了生成仿真模型,但生成不了,文件目录下没有example.v,只有一个对应 的sdc文件 。 另外生成报告里还有 一个warning ,,求指导

2017-09-07 11:48:09

本帖最后由 Laputa_fly 于 2013-11-23 13:46 编辑

用quartus9.0调用了altera FFT IP 核 生成了modisim 和 matlab 的仿真文件。用modelsim 仿真有结果。但是按照官方的使用说明用matlab仿真时出现问题。请大家帮忙解决一下。谢谢!

2013-11-23 13:43:41

1、在Picorv32 / 蜂鸟E203软核上运行RT-Thread 首先介绍一下我用的 FPGA 开发板,也就是荔枝糖(EG4S20),这块开发板性价比应当算是很高了,100RMB有20K逻辑

2022-09-16 16:15:39

在quartus II13.0版本上调用FFT IP核并进行modelsim-altera仿真,在生成IP核时,step2中勾选generate simulation model、generate

2016-10-07 22:23:33

树莓派Pico采用他自己的处理器RP2040,双核M0,133MHz。为了体验它的双核编程环境和性能,我用它来实现一个AppleII仿真,当然是在AppleWin代码基础上移植改造的。Core0用作

2022-05-24 20:58:55

基于FPGA的FFT和IFFT IP核应用实例AT7_Xilinx开发板(USB3.0+LVDS)资料共享腾讯链接:https://share.weiyun.com/5GQyKKc百度网盘链接

2019-08-10 14:30:03

导入(2) 编译与仿真(3) 综合(4) IP核封装(5) IP核测试基于创龙科技TLK7-EVM开发板,是一款基于Xilinx Kintex-7系列FPGA设计的高端评估板,由核心板和评估底板组成

2021-02-19 18:36:48

文章,小编就将以飞凌嵌入式的OKMX8MP-C开发板为例,为大家介绍多核异构处理器M核程序的启动配置、程序编写和实时仿真的过程。飞凌嵌入式OKMX8MP-C开发板所搭载的NXP i.MX8M Plus处理器

2023-02-21 16:08:17

如何仿真IP核(建立modelsim仿真库完整解析)

2012-08-15 13:16:12

你好,我正在尝试使用Aurora 8B / 10B建立仅传输(流媒体)。现在使用Vivado 2014.4进行模拟阶段。我知道GTXE2_COMMON原语需要在设计中使用以包含一个QUAD PLL

2020-08-14 08:49:13

嗨,我正在尝试将Aurora与Virtex-6 LX240t配合使用。示例设计是由核心生成器(11.5和12.1)生成的测试代码。当我使用环回模式(近端PCS和PMA)进行测试时,两者都能正常工作

2020-06-02 13:14:40

嗨, 我在自定义板(Kintex 7)中为Aurora 8b10b创建了两个项目。Aurora Simplex_Tx和Aurora Simplex _RX。我想将这些设计整合在一起。我已将Rx的源文件添加到Tx项目中。我应该将Rx项目的XDC文件添加到Tx项目中吗?谢谢,Abinaya

2020-08-17 09:59:17

在使用Aurora时,我可以决定是否发送数据吗?非常感谢您的帮助。

2020-07-25 11:22:01

本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2021-05-08 06:22:32

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

HI可以两个或多个BD地址,动态改变在一个板上生成使用PSoC Creator?最好的问候,Yoshizu

2019-10-22 06:14:47

我的quartus ii 版本13.1fft核版本13.1 modelsim版本64位 10.4在quartus ii 中使用rtl仿真时(已经在quartus ii中编译成功) 弹出

2019-02-26 16:21:08

在开发板上正常运行的程序生成.hex文件后无法在proteus上仿真,用到了外部中断和systick定时器,配置的引脚也完全没反应

2023-09-25 07:07:05

本帖最后由 yirenonege 于 2012-5-17 10:05 编辑

用 core insert生成的核怎么删掉啊?以前没有过ISE,工程下面的文件也太多了另外如何观测两个模块之间的连线

2012-05-13 18:22:51

fft仿真没有输出,初始值不正常,但上板验证没问题,试过重新生成ip核没有用,请教一下是什么问题。

2019-05-10 10:27:57

我使用Aurora(5.2)内核在125MHz GT REFclock上运行光纤,核心表示将使用2.5Gbps的线速(线宽为16位)。我现在需要发送更高分辨率的图像,看不出核心生成器如何生成

2019-06-20 15:26:44

IMX6Q四核开发板,怎么做到分核运行?

2022-01-10 06:59:30

没用过ISE,不知道生成的IP核文件夹中 ,哪些是需要添加到modelsim中用于仿真的文件 。拿ram举例,仿真库文件还应该添加哪些内容。希望大神们指导下 多谢

2018-12-18 17:58:32

请问为什么生成FFT ip 核会卡在生成这一步,前两天还好好的。求大神的解决办法,网上实在找不到方法

2016-11-01 13:42:43

如题,调用altera公司的FFT IP核,用的是13.1版本,将modulsim仿真的结果输入到matlab画出频谱图,功能仿真结果没有问题,但门级仿真中除了原频率信息外,出现了很多不存在的频率

2018-08-28 20:43:56

高速DAP仿真器 BURNER

2023-03-28 13:06:20

描述了利用Vega Prime生成红外场景的方法,针对该方法在成像制导仿真系统应用中出现的问题进行了讨论。介绍了地形场景模型的建立方法;分析了制导仿真图像生成、仿真数据流程等方

2011-05-19 18:25:30 0

0 基于8051的Proteus仿真-DAC0832生成锯齿波

2016-09-01 23:28:14 42

42 Aurora 是赛灵思的高速串行通信协议,一直在行业内非常受欢迎。当某些应用领域中的行业协议实现过程太过复杂或者太耗费资源时,Aurora 通常是首选方案。Aurora 能实现低成本、高数据速率

2017-11-17 05:31:09 2090

2090

Aurora系统被关注,源于2019年6月,国外媒体注意到华为在自家产品测试Aurora系统的消息。在国外媒体更早关于该系统的报道中,他们发现开发Auroa系统的公司早在2015年就被俄罗斯巨商收入麾下。

2019-08-29 14:37:10 4271

4271 在AWS re:Invent上,AWS发布了新一代Aurora Serverless,以及一个让客户能更轻松的从SQL Server迁移到Amazon Aurora PostgreSQL的新功能

2020-12-03 10:38:28 1666

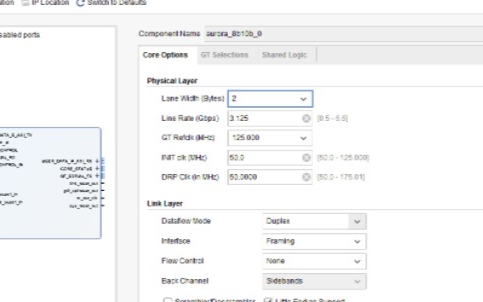

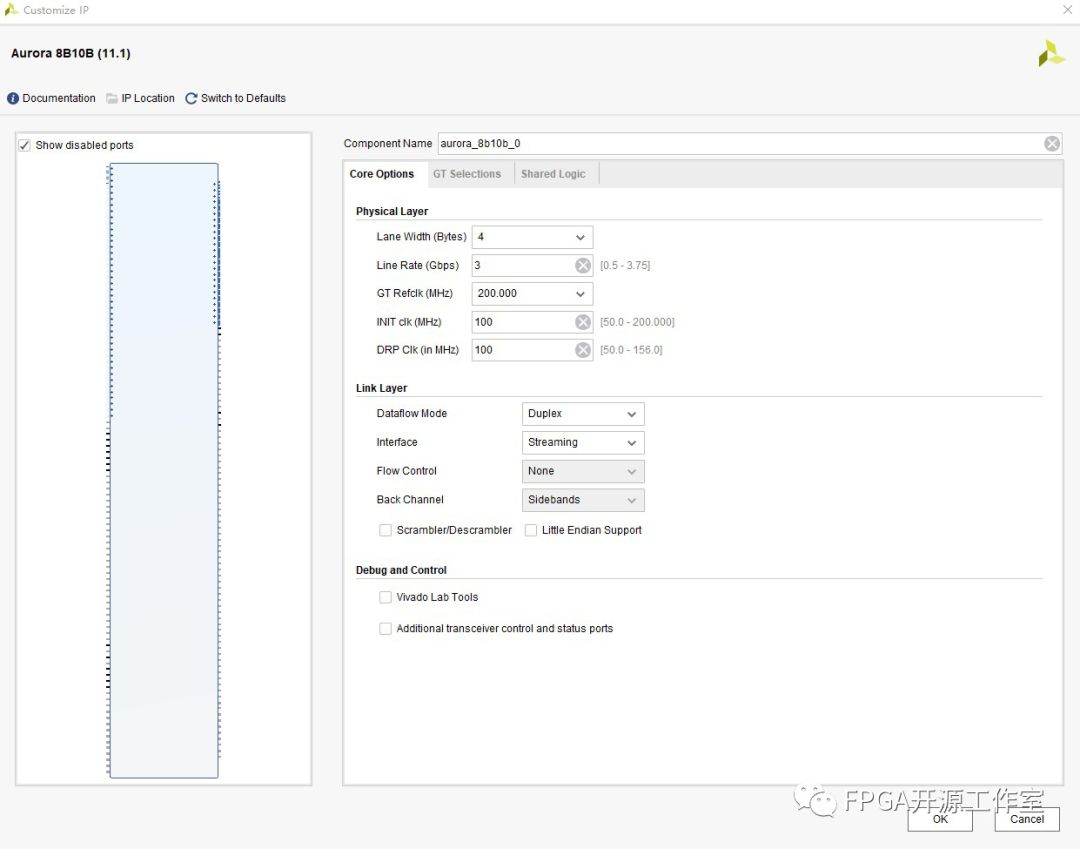

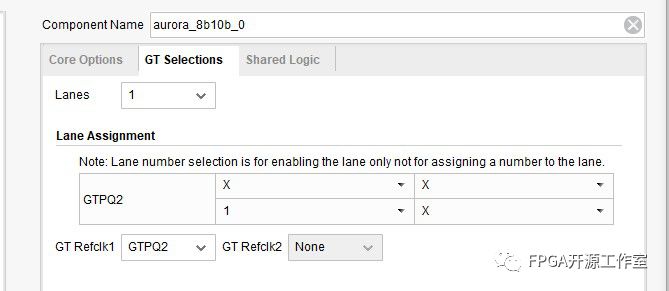

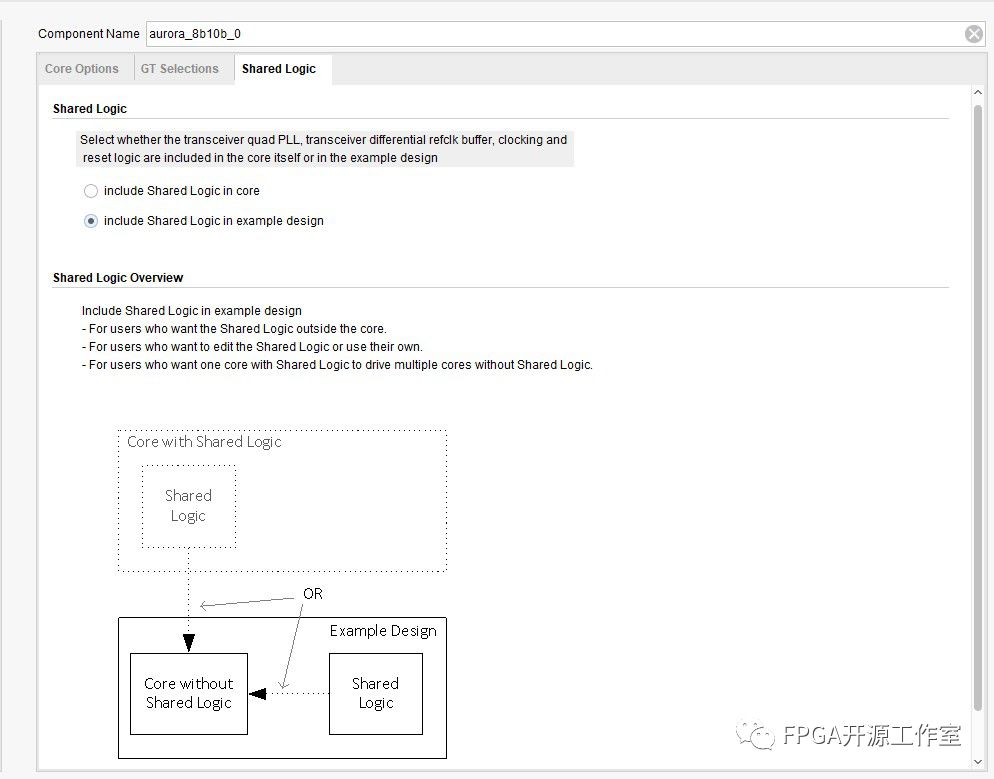

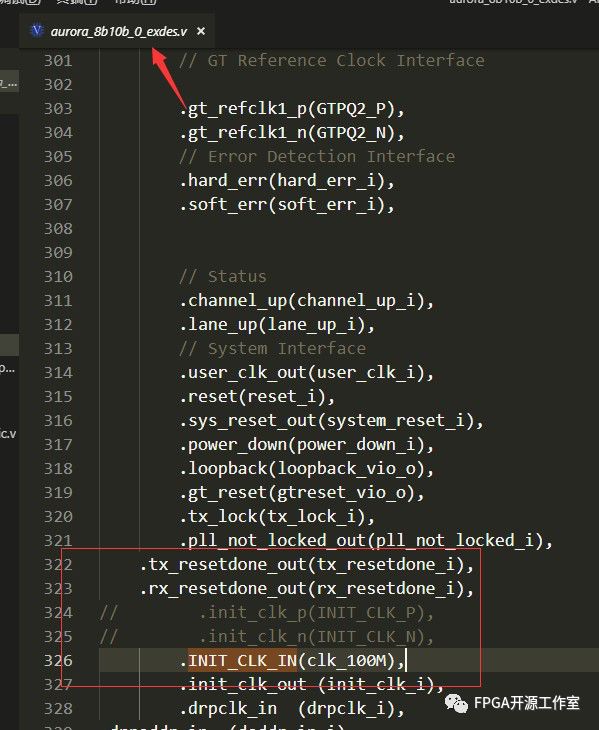

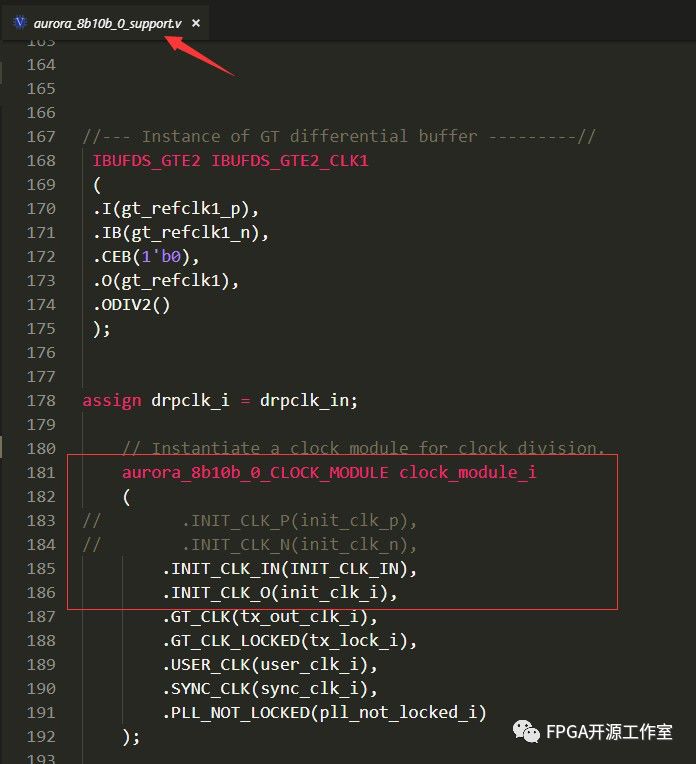

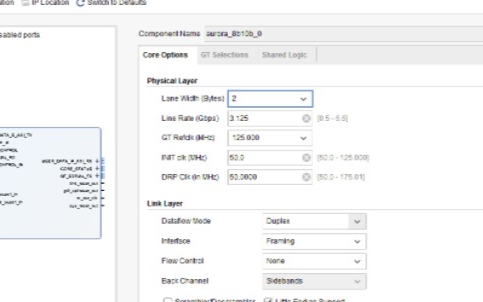

1666 开门见山的说,跟DDR/PCIE/GTX这种复杂的IP相比,Aurora配置那是相当的简单。走着。

2022-02-19 18:52:10 6548

6548

Aurora 是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议。这为物理层提供透明接口,让专有协议或业界标准协议上层能方便地使用高速收发器。虽然使用的逻辑资源非常少,但 Aurora

2022-02-19 18:21:55 6013

6013

在Vivado软件中,我们生成好IP后可以可以打开带有例子的工程,进行仿真查看LANE_UP和CHANNEL_UP信号拉高后,即可认为光纤通道初始化成功,在对其数据接口进行查看,官方给的例程主要分为三大块,数据产生模块、光纤传输模块、数据检查模块 。

2023-03-30 09:28:46 1012

1012

电子发烧友App

电子发烧友App

评论