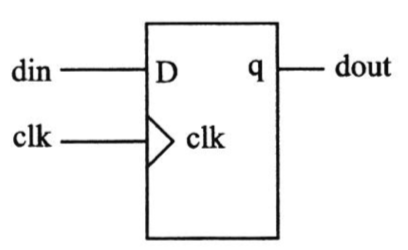

xilinx verilog语法技巧 一 硬件描述语言(HDL)编码技术让您: •描述数字逻辑电路中最常见的功能。 •充分利用Xilinx®器件的架构特性。 1 Flip-Flops

2020-12-13 10:29:00 3065

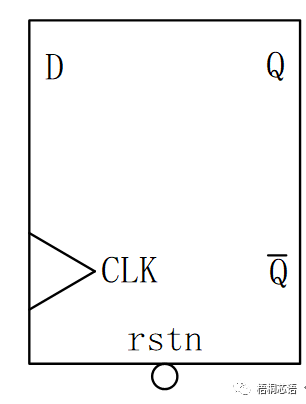

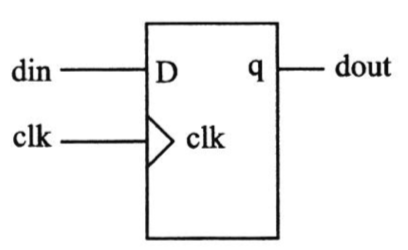

3065 现代逻辑设计中,时序逻辑设计是核心,而寄存器又是时序逻辑的基础,下面将介绍几种常见的寄存器的Verilog设计代码供初学者进行学习理解。

2023-07-27 09:03:59 1899

1899

Verilog HDL硬件描述语言

2013-01-13 14:40:20

Verilog HDL的语法,希望能帮助正在学习或者要用到的朋友

2014-05-25 14:10:04

;5"><strong>Verilog HDL硬件描述语言。J.Bhasker著,徐振林等译<br/></strong></font><br/>

2009-08-21 12:37:14

Verilog HDL硬件描述语言(非常经典的教材)FPGA软件无线电开发(全阶视频教程+开发板+实例)详情链接:http://url.elecfans.com/u/5e4a12f2ba

2013-07-22 14:50:03

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214.5.2 寄存器类型

2017-12-08 14:39:50

本帖最后由 IC那些事儿 于 2020-11-30 19:05 编辑

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象

2020-11-30 19:03:38

前不久学FPGA,找到的verilog的教程 第1章 简 介 本章介绍Verilog HDL语言的发展历史和它的主要能力。 1.1什么是Verilog HDL? Verilog HDL是一种硬件描述

2018-07-03 05:19:30

Level):描述数据在寄存器之间流动和如何处理这些数据的模型。• 门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。• 开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

2019-09-06 09:14:16

本合集资料包括:1.Verilog HDL程序设计实例详解2.Verilog HDL经典教程3.Verilog HDL实验练习与语法手册4.Verilog HDL硬件描述语言

2020-08-21 10:06:20

我是FPGA的新手想请教一下Verilog中什么时候需要给变量定义寄存器。一开始我以为每个输入、输出都要定义没定义的话默认为一,但是今天看到一段代码输入变量[3:0] key_in并没有定义寄存器。

2017-01-18 19:55:47

Verilog_HDL硬件描述语言 FPGA的资料

2013-02-26 14:03:42

verilog+hdl硬件描述语言 初学者的福音 帮助广大初学者步入此行

2013-08-12 23:47:12

个人觉得如果用“HDL通用寄存器描述”一个32位寄存器,则综合需要32个LUT(假设每个LUT后有1个FF)。而用厂家 distributed ram 原语描述,则是不是可把每个LUT用做RAM

2012-10-04 22:44:03

各位大佬有会FPGA Verilog HDL编程的嘛,小弟现在有一个关于移位寄存器的问题想问:利用ASM流程图写出代码!!有会的可以联系我!可支付酬金!!

2019-11-15 06:19:58

NVIC是与内核高度集成的外设,由ARM负责设计,与其他外设不同,因此在ST的参考手册中并为过多提及,具体的寄存器需要参考 M4内核参考手册 。寄存器描述 core_cm4.htypedef

2022-01-24 07:14:57

大,目前很多国外大学都使用SystemVerilog作为教学语言。本文以Verilog语言为基础讲述HDL代码编写技巧。RAM部分内容比较多,单独放在第27篇讲述。1.触发器、寄存器和锁存器

2020-09-29 10:08:57

《Verilog_HDL硬件描述语言》_,[美]贝斯克(Bhasker,J.)_,徐振林等译

2013-04-18 15:57:52

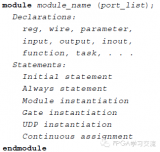

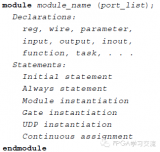

、寄存器、线网和参数等的说明部分必须在使用前出现。为了使模块描述清晰和具有良好的可读性, 最好将所有的说明部分放在语句前。图 2-6 所示的是一个半加器。图 2-6 半加器这个半加器用 Verilog

2018-09-18 09:37:40

、数据流方式、结构化方式;• Verilog HDL 中有线网(Wire)数据类型和寄存器(Reg)数据类型两类数据类型,线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。• 能够描述

2018-09-18 09:33:31

硬件描述语言Verilog,西安科大教学课件,总共包括完整八个章节学习内容。具体每章节内容如下第一章:Verilog HDL数字集成电路设计方法概述第二章:Verilog HDL基础知识第三章

2021-03-30 14:31:41

逻辑,应在敏感信号表中列出所有的输入信号;7、所有的内部寄存器都应该可以被复位;8、用户自定义原件(UDP元件)是不能被综合的。一:基本Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器,还有可能被优化掉。二:veril...

2021-07-29 06:10:04

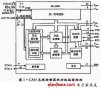

CAM具有什么功能?基于移位寄存器的CAM的设计基于移位寄存器的CAM的Verilog HDL实现

2021-04-13 06:28:23

Verilog模型有哪几种?Verilog HDL模型是由哪些模块构成的?如何用Verilog HDL语言描述D型主从触发器模块?

2021-10-19 08:36:32

)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。HDL硬件描述语言(HDL)是一种用来设计数字逻辑系统和描述数字电路的语言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一种用于电路设计的高级

2021-12-22 07:39:43

Verilog HDL Synthesis (A Practical Primer)

2009-02-12 09:36:24 40

40 本书简要介绍了Verilog硬件描述语言的基础知识,包括语言的基本内容和基本结构 ,以及利用该语言在各种层次上对数字系统的建模方法。书中列举了大量实例,帮助读者掌握语言

2009-07-20 11:36:35 0

0 Verilog-HDL实践与应用系统设计本书从实用的角度介绍了硬件描述语言Verilog-HDL。通过动手实践,体验Verilog-HDL的语法结构、功能等内涵。在前五章,以简单的实例列举了Verilog-HDL的用法;

2009-11-14 22:57:40 146

146 Verilog HDL 华为入门教程

本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL设计方法,初步了解并掌握Verilog HDL语言的基本要素,能

2010-02-11 08:35:38 140

140 本书简要介绍了Verilog 硬件描述语言的基础知识,包括语言的基本内容和基本结构,以及利用该语言在各种层次上对数字系统的建模方法。书中列举了大量实例,帮助读者掌握

2010-07-02 14:55:51 124

124 摘要:一种利用Verilog HDL设计CAM的方案,该方案以移位寄存器为核心,所实现的CAN具有可重新配置改变字长、易于扩展、匹配查找速度等特点,并在网络协处理器仿

2006-05-26 21:52:14 933

933

什么是Verilog HDL?

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统

2009-01-18 14:53:26 3678

3678

【摘 要】 基于EPP协议的特点,应用复杂可编程逻辑器件(CPLD)开发了移位寄存器输出接口。介绍了EPP协议和接口的Verilog HDL描述。

2009-05-11 19:34:31 1215

1215

摘要:一种利用Verilog HDL设计CAM的方案,该方案以移位寄存器为核心,所实现的CAN具有可重新配置改变字长、易于扩展、匹配查找速度等特点,并在网络协处理器仿真中得到

2009-06-20 12:49:52 1307

1307

摘要: 介绍了一种采用硬件控制的自动数据采集系统的设计方法,包括数字系统自顶向下的设计思路、Verilog HDL对系统硬件的描述和状态机的设计以及MAX+PLUSII开发

2009-06-20 14:57:47 1264

1264

Verilog HDL程序基本结构与程序入门

Verilog HDL程序基本结构

Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的

2010-02-08 11:43:30 2185

2185 Verilog HDL语言简介

1.什么是Verilog HDLVerilog HDL是硬件描述语言的一种,用于数

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL语言对比

Verilog HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。VHDL是在1987年成为IEEE标准,Verilog HDL

2010-02-09 09:01:17 10317

10317 寄存器,寄存器是什么意思

寄存器定义 寄存器是中央处理器内的组成部分。寄存器是有限存贮容量的高速存贮部件,它们可用

2010-03-08 14:26:32 20897

20897 在我国使用Verilog HDL的公司比使用VHDL的公司多。从EDA技术的发展上看,已出现用于CPLD/FPGA设计的硬件C语言编译软件,虽然还不成熟,应用极少,但它有可能会成为继VHDL和Verilog之后,设计大规模CPLD/FPGA的又一种手段。

2011-03-12 11:21:20 1686

1686 《Verilog HDL 程序设计教程》对Verilog HDL程序设计作了系统全面的介绍,以可综合的设计为重点,同时对仿真和模拟也作了深入的阐述。《Verilog HDL 程序设计教程》以Verilog-1995标准为基础

2011-09-22 15:53:36 0

0 verilog硬件描述语言课程讲义

2012-05-21 15:01:29 33

33 在此利用Verilog HDL设计了一款CAN总线控制器,首先根据协议把整个CAN总线控制器划分为接口逻辑管理、寄存器逻辑和CAN核心模块3个模块,然后用Verilog HDL硬件描述语言设计了各个功能模块

2012-07-31 14:25:24 7806

7806

Verilog_HDL的基本语法详解(夏宇闻版):Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结

2012-10-08 14:48:31 0

0 电子发烧友网核心提示 :目前,硬件描述语言(HDL)可谓是百花齐放,有VHDL、Superlog、Verilog、SystemC、Cynlib C++、C Level等等。电子发烧友网小编今天就带大家一起来了解下几种具有代表

2012-10-15 10:51:38 4127

4127 Verilog HDL程序设计与实践着重介绍了Verilog HDL语言

2015-10-29 14:45:47 21

21 Verilog硬件描述语言参考手册,Verilog语法内容介绍

2015-11-12 17:20:37 0

0 Verilog HDL硬件描述语言

有需要的下来看看

2015-12-29 15:31:27 0

0 本章讲述Verilog HDL中的结构建模方式。结构建模方式用以下三种实例语句描述,verilog相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 14:58:20 14

14 本章讲述Verilog HDL指定用户定义原语UDP的能力。UDP的实例语句与基本门的实例语句完全相同,即U D P实例语句的语法与基本门的实例语句语法一致。verilog相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 16:09:32 12

12 本章讲述Verilog HDL为门级电路建模的能力,包括可以使用的内置基本门和如何使用它们来进行硬件描述。verilog相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 16:09:32 18

18 本章讲述在Verilog HDL中编写表达式的基础。表达式由操作数和操作符组成。表达式可以在出现数值的任何地方使用。verilog相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 16:09:32 19

19 本章介绍Verilog HDL语言的发展历史和它的主要能力。verilog相关教程材料,有兴趣的同学可以下载学习

2016-04-25 16:09:32 14

14 本章介绍Verilog HDL的基本要素,包括标识符、注释、数值、编译程序指令、系统任务和系统函数。另外,本章还介绍了Verilog硬件描述语言中的两种数据类型。verilog相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 16:09:32 16

16 本章描述Verilog HDL中的第三种建模方式,即行为建模方式。为充分使用Verilog HDL,一个模型可以包含所有上述三种建模方式。verilog相关教程材料,有兴趣的同学可以下载学习

2016-04-25 16:09:32 14

14 本章给出了一些用Verilog HDL编写的硬件建模实例。verilog相关教程材料,有兴趣的同学可以下载学习

2016-04-25 16:09:32 25

25 本章介绍了如何编写测试验证程序(test bench)。测试验证程序用于测试和验证设计的正确性。Verilog HDL提供强有力的结构来说明测试验证程序。verilog相关教程材料,有兴趣的同学可以下载学习

2016-04-25 16:09:32 17

17 本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL设计方法,初步了解并掌握Verilog HDL语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的Verilog HDL建模。

2016-07-15 15:27:00 0

0 verilog HDL,fpga,硬件电路学习资料

2016-09-01 14:55:49 0

0 VHDL语言编程学习Verilog硬件描述语言

2016-09-01 15:27:27 0

0 ;第4章至第6章主要讨论如何合理地使用Verilog HDL语言描述高性能的可综合电路;第7章和第8章重点介绍了如何编写测试激励以及Verilog的仿真原理;第9章展望HDL语言的发展趋势。

2016-10-10 17:04:40 566

566 Verilog HDL硬件描述语言,感兴趣的小伙伴们可以瞧一瞧。

2016-11-11 11:20:11 11

11 Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),Verilog HDL语言是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2017-02-11 14:00:20 35998

35998

本文描述的是GD32硬件中断错误的所有寄存器以及相应的位功能。

2017-08-28 15:32:09 9

9 9s12系列单片机寄存器描述详细

2017-10-24 10:40:21 10

10 本文档的主要内容详细介绍的是Verilog HDL入门教程之Verilog HDL数字系统设计教程。

2018-09-20 15:51:26 80

80 本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL 设计方法,初步了解并掌握Verilog HDL语言的基本要素,能够读懂简单的设计代码并能够进行一些简单设计的Verilog HDL建模。

2019-02-11 08:00:00 95

95 Verilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。

2019-03-08 14:29:12 12094

12094 从数字电路中学到的逻辑电路功能,使用硬件描述语言(Verilog/VHDL)描述出来,这需要设计人员能够用硬件编程思维来编写代码,以及拥有扎实的数字电路功底。

2019-12-05 07:10:00 2977

2977

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。

2019-11-13 07:03:00 3029

3029 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2019-11-20 07:00:00 5088

5088 硬件描述语言基本语法和实践

(1)VHDL 和Verilog HDL的各自特点和应用范围

(2)Verilog HDL基本结构语言要素与语法规则

(3) Verilog HDL组合逻辑语句结构

2019-07-03 17:36:00 53

53 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL

2020-06-17 16:13:11 12910

12910 本书介绍了硬件描述和Verilog HDL概述、Verilog HDL的基本语法、Verilog HDL程序设计语句和描述方式、Verilog HDL对组合逻辑和时序逻辑的设计举例、Verilog

2020-07-21 08:00:00 0

0 Verilog HDL和VHDL是目前两种最常用的硬件描述语言,同时也都是IEEE标准化的HDL语言。

2020-08-25 09:14:34 8605

8605 的是硬件描述语言。最为流行的硬件描述语言有两种Verilog HDL/VHDL,均为IEEE标准。Verilog HDL具有C语言基础就很容易上手,而VHDL语言则需要Ada编程基础。另外Verilog

2020-09-01 11:47:09 4002

4002

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2020-11-02 17:30:55 23

23 本文档的主要内容详细介绍的是Verilog教程之Verilog HDL程序设计语句和描述方式。

2020-12-09 11:24:23 46

46 本文档的主要内容详细介绍的是Verilog HDL硬件语义的详细资料分析。

2021-02-01 15:37:11 13

13 进行描述; 时序行为使用过程结构描述。一个模块可以在另一个模块中使用。 一个模块的基本语法如下: 说明部分用于定义不同的项,例如模块描述中使用的寄存器和参数。语句定义设计的功能和结构。说明部分和语句可以散布在模块中的任何地方

2021-03-12 16:24:28 1951

1951

1、如何使用Verilog HDL描述可综合电路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL语言仅是对已知硬件电路的文本描述。所以编写前: 对所需实现的硬件

2021-04-04 11:19:00 3837

3837

),这里的D也是描述的首字母。 也就是说,HDL的D,是描述的意义。HDL也就是硬件描述语言。 2. 为了支持Soc的验证,支持数模混合,新的System Verilog加入了HVL(Hardware Verification Language),即硬件验证语言。 3. 合并之前的硬件描述语言功能,称为

2021-04-15 15:44:02 2773

2773 其中,返回值的类型和位宽是可选项,如果缺省会返回一位寄存器类型数据。Verilog HDL认为函数的定义隐式地声明了与函数同名的寄存器。函数的定义把函数被返回值所赋值寄存器的名称初始化为与函数同名的内部变量。

2021-07-02 10:24:26 1939

1939 Verilog HDL是一种以文本形式描述数字系统硬件的结构和行为的硬件描述语言,也可描述逻辑电路图、逻辑表达式等。Verilog HDL和VHDL是目前主流的、最受欢迎的两种硬件描述语言。

2021-07-23 14:36:55 9910

9910 Verilog HDL入门教程-Verilog HDL的基本语法

2022-01-07 09:23:42 159

159 个人感觉:硬件描述语言(vhdl等):是为了制造cpu(类似的芯片),设计人员使用hdl设计和安排寄存器和时序电路如何组合,然后最终会生成门级网表,然后通过相关软件等生成最终物理电气电路(怎么布局

2022-01-13 15:09:46 0

0 HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

2022-08-31 09:06:59 1168

1168 VersaClock 6E 系列寄存器描述和编程指南

2023-01-10 19:13:58 0

0 汽车 VersaClock 6E 寄存器描述和编程指南

2023-01-30 18:47:53 0

0 VersaClock 6 系列寄存器描述和编程指南

2023-03-15 19:12:28 0

0 VersaClock 6E 系列寄存器描述和编程指南

2023-06-30 20:07:01 2

2 汽车 VersaClock 6E 寄存器描述和编程指南

2023-07-03 20:13:38 0

0 VersaClock 6 系列寄存器描述和编程指南

2023-07-05 20:54:30 0

0 使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

2023-07-09 10:20:12 562

562

节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点。

2023-08-28 09:54:34 1115

1115

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL

2023-08-29 15:58:29 0

0

电子发烧友App

电子发烧友App

评论