高速数字电路的仿真

介绍了专用于高速数字电路的仿真工具Hyperlynx,并使用它对高速数字电路中的阻抗匹配、传输线长度

2009-03-20 14:11:39 1275

1275

关键字:Altera 、FPGA、软硬件协调设计(Verilog & C)、CPU、总线、外设FPGA硬件结构知识Verilog HDL语言编程基础FPGA常用开发工具 SOPC硬件系统开发SOPC软件系统开发Avalon总线规范Nios II外设及其编程 七段数码管时钟...

2021-12-22 08:06:06

本帖最后由 lee_st 于 2017-11-30 12:35 编辑

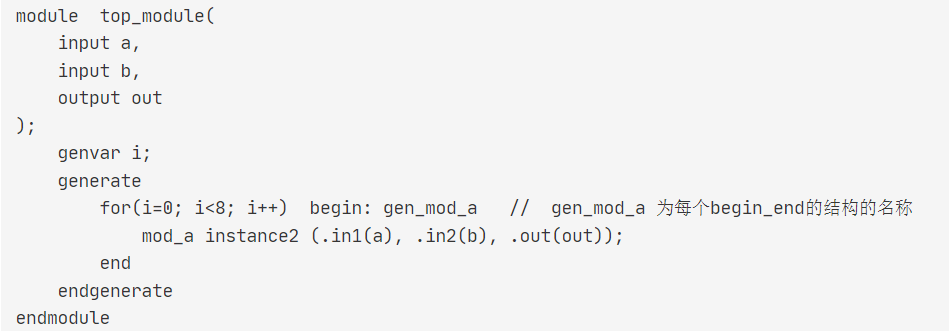

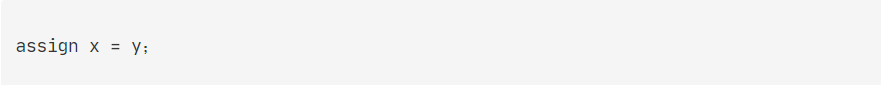

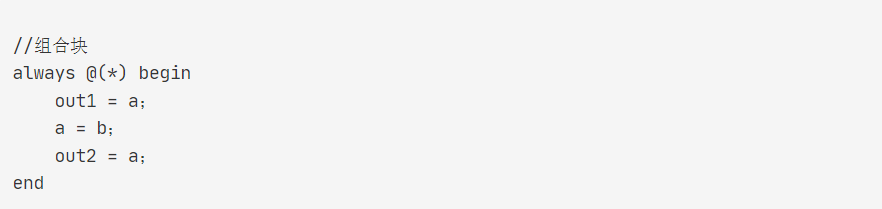

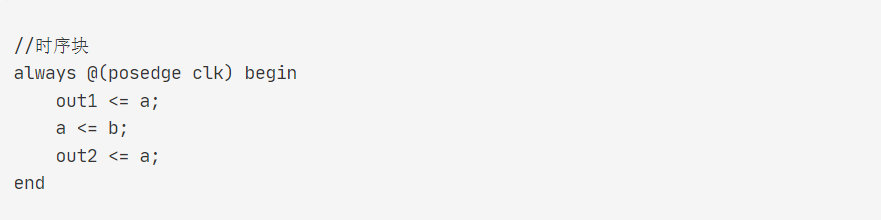

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:33:55

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:36:07

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:38:44

本帖最后由 lee_st 于 2017-11-30 12:42 编辑

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:41:35

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:44:09

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:46:17

讲授内容EDA设计方法学;Verilog HDL语言;数字电路与系统设计;高级描述语言及工具使用;

2017-11-30 12:48:48

Verilog数字系统设计十二复杂数字电路设计2文章目录Verilog数字系统设计十二前言一、什么是FIFO控制器?二、编程1.要求:2.设计思路:3.FIFO控制器实现:总结前言随着人工智能

2022-02-09 07:23:50

介绍一款可编程语音处理器的设计与应用

2021-06-03 07:16:50

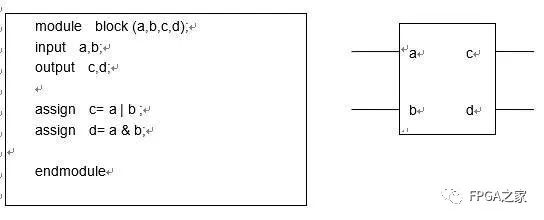

、韩国、美国等区域应用很普遍。本文简要地介绍国内数字电路设计普遍使用的Verilog语言。verilog是什么。Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言

2021-07-26 06:39:56

数字电路-数字时钟电路设计 希望大家喜欢。

2016-12-06 09:46:39

相关推荐导读在与E课网学员们的学习交流过程中,E课网的讲师们发现很多人对数字电路设计的基本理论概念缺乏了解,而且对实际工程项目的发烧友学院发表于 2016-12-09 00:00•4969次阅读

2021-09-15 06:02:55

两种类型,这里又以CMOS集成数字电路为主,因它功耗低、工作电压范围宽、扇出能力强和售价低等,很适合电子爱好者选用。 介绍应用时,以实用为主,特别介绍一些家电产品和娱乐产品中的数字电路。这样可使

2018-08-28 15:36:27

数字电路设计与Verilog HDL

2015-07-16 16:21:19

数字电路作为一门专业基础课,除了介绍数字电路的理论知识外,更需要通过配套的实验平台将理论知识和实践环节相结合,培养学生的动手能力和实践创新能力。为此,自主开发了基于 FPGA 的数字电路“口袋实验室

2020-09-04 17:04:34

在数字电子技术基础课程中,数字电路设计的数学基础是布尔函数,并利用卡诺图进行化简。卡诺图只适用于输入比较少的逻辑函数的化简。数字电路的设计方法是:组合电路设计:提出问题→确定逻辑关系→列真值表→逻辑

2019-02-27 11:55:00

答案,以助你在电路设计软件学习之路上更进一步。骚年,抱着以上的疑问,一起来看看吧。在电子设计辅助软件中,Protel是最常用的软件,新版本的Protel软件增加了电路仿真功能,能够对设计的电路进行模拟

2019-09-24 07:30:00

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

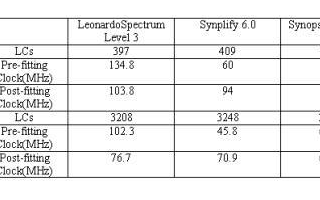

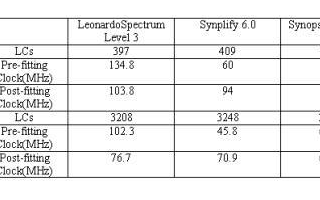

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解 RTL 电路时序模型的基础上,采用合理的设计方法在设计复杂数字

2012-02-02 15:40:10

本帖最后由 xianer317 于 2014-6-21 19:34 编辑

FPGA/CPLD数字电路设计经验分享

2014-06-21 19:33:20

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统

2012-03-05 16:33:30

FPGACPLD数字电路设计经验分享

2012-08-07 21:46:49

Perl语言在电路设计中的应用实用提取和报表语言是由Perl语言在电路设计中的应用 开发并不断更新,用于Perl语言在电路设计中的应用 环境下编程的一种模块化的、可扩展的高级语言。在集成电路后端

2012-01-11 15:19:01

关于数字电路设计的一些经验

2015-03-17 21:27:38

基本的了解,自己买了更详细的夏闻宇的书,如果有谁需要电子稿的我可以发给他,留邮箱Verilog的语法覆盖的方面比C语言更加多,可使用的灵活性更强,一定要贯彻的是数字电路的设计,不要用C语言的思想来做三

2016-09-02 19:13:29

)、AUTOCA等开发工具的应用;3、熟悉单片机和数字电路应用、善于用C语言编写驱动程序,4、开发过电机控制的单片机电路和驱动程序;5、熟悉常用电子元器件的特性和选型方法;电子组件板的加工工艺、流程和检验

2017-10-16 10:57:04

非常清楚的, 下面就数字电路聊聊芯片设计的一些事情,就是芯片设计有哪些活做, 这并不是全面完整的系统介绍,只是个人的了解和总结, 希望抛砖引玉,也许不全面, 不正确, 欢迎同学们指正和补充 说到数字芯片

2013-01-04 17:07:12

数据的数字电路。从整体上看,数字电路可以分为组合逻辑电路和时序逻辑电路两大类。一、数字电路的发展与分类 从前面的介绍,大家已经了解到数字电路是以二值数字逻辑为基础的,其工作信号是离散的数字信号。电路

2009-04-06 23:45:00

求一款基于VHDL的异步串行通信电路设计分享

2021-04-08 06:16:42

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案

2021-04-30 06:34:54

本帖最后由 gk320830 于 2015-3-5 00:03 编辑

华为《高速数字电路设计教材》

2012-08-20 13:23:04

华为《高速数字电路设计教材》这本书是专门为电路设计工程师写的。主要描述模拟电路原理在高速数字电路设计中的分析应用

2014-09-01 23:09:11

华为《高速数字电路设计教材》这本书是专门为电路设计工程师写的。主要描述模拟电路原理在高速数字电路设计中的分析应用

2014-09-01 23:20:19

本帖最后由 eehome 于 2013-1-5 10:02 编辑

就算作一个数字电路设计,附有 protuse仿真图还有 相关用到的资料

2012-06-08 14:12:12

FPGA芯片是由哪些部分组成的?如何去实现一种基于FPGA芯片的可重构数字电路设计?

2021-11-05 08:38:57

如何用C语言实现一款猜数字游戏

2021-01-06 07:10:06

射频和数字电路设计的区别是什么?

2021-05-18 06:05:19

;MMICAD等。下面简单介绍前三个软件。 (1)SPICE:由美国加州大学推出的电路分析仿真软件,现在用得较多的是PSPICE6.2,在同类产品中是功能最为强大的模拟和数字电路混合仿真 EDA软件

2018-10-17 11:48:12

设计工具软件、数字电路系统设计实践”的体系结构编写。为了让读者更容易掌握Verilog HDL知识,本书在介绍数字电路设计的过程中列举了Verilog HDL的很多例程,并假定读者没有任何数字逻辑

2022-04-19 14:40:04

怎么实现基于可编程逻辑器件的数字电路设计?

2021-05-06 08:36:18

大家好,我是电子爱好者新手,现在想学点数字电路设计。刚把数字电路这么课程学完。我想学电路设计,不知道如何下手。比如FPGA什么的,这些都怎么开始学习啊。请知情者指点下。谢谢

2013-08-02 08:17:31

数字集成电路设计ASIC设计/验证经验;2.熟悉逻辑/时序电路的原理和设计;3.精通verilog语言;熟练使用Cadence,Modelsim,NC-Verilog,DC等设计验证工具;4.有较强的责任心

2015-02-27 10:52:58

及基本逻辑器件的硬件描述语言引入各个章节中。《新编数字电路与数字逻辑》可作为高等院校计算机、电子、通信、自动化、机电一体化等专业本科和专科的教材,也可作为自学考试和从事电子技术工程人员的自学用书。注 本资料来源于网络资源 出处电子爱好者论坛

2018-10-28 21:36:01

请求大佬分享一款用于物体探测与统计的电路设计

2021-04-14 06:42:37

)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。HDL硬件描述语言(HDL)是一种用来设计数字逻辑系统和描述数字电路的语言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一种用于电路设计的高级

2021-12-22 07:39:43

等。下面简单介绍前三个软件。(1)SPICE:由美国加州大学推出的电路分析仿真软件,现在用得较多的是PSPICE6.2,在同类产品中是功能最为强大的模拟和数字电路混合仿真 EDA软件,它可以进行

2020-06-28 10:49:47

现在有什么电路仿真软件比较不错的,能不能介绍一款。

2019-01-21 09:30:43

群主好,我想请教数字电路的系统级设计验证工具及流程?即系统工程师常用的硬件描述语言,系统验证工具以及设计验证的基本流程,多谢!

2012-09-05 15:11:23

、综合素质、创新能力[’]。2005年我校电子技术实验教学中心(以下简称中心)以“加强基础训练,培养能力,注重创新”为指导思想,在面向各类专业的数字电路实验教学中,开设了以学生为主、教师为辅的数字电路设计

2012-10-25 11:59:02

【简介】本书从高速数字电路的定义谈起,介绍了传输线的基本理论,并涉及到了如何运用Grounding/Guard降低噪声等内容,还以高速数字电路电气特性,如串扰、反射及时钟脉冲不对称等为例,阐述了一

2017-12-12 08:51:55

《高速数字电路设计及EMC设计》分享。

2015-08-04 11:50:33

高速数字电路设计的几个基本概念高速数字电路设计的基本要求是什么

2021-04-27 06:19:05

基于LabVIEW的数字电路设计和仿真

数字电路设计和仿真是电子工程领域的基本技术。介绍了基于LabV IEW的数字电路设计和仿真的原理和方法,比较了其与专业EDA软

2010-03-30 16:09:49 123

123 本书是专门为电路设计师工程师写的

它主要描述模拟电路原理在高速数字电路设计中的分析应用

1-3章分别介绍了模拟电路术语、逻辑门高速特性和标准高速电路测量

2010-06-23 18:02:57 63

63 流水线技术在高速数字电路设计中的应用

2010-07-17 16:37:21 6

6 高速数字电路设计

关于高速数字电路的电气特性,设计重点大略可分为三项 : Ø 正时 (Timing) :由于数字电路大多依据时脉信号来做信号间的同

2007-10-16 17:22:57 2746

2746 数字电路设计

关于高速数字电路的电气特性,设计重点大略可分为三项:

正时(Timing) :由于数字电路大

2009-08-26 19:08:06 2665

2665 基于可编程逻辑器件的数字电路设计

0 引 言

可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以

2009-11-16 10:46:41 1473

1473

《VHDL与数字电路设计》是有卢毅、赖杰主编的,主要介绍涉及数字系统设计的多方面原理、技术及应用,主要内容有数字系统的基本设计思想、设计方法和设计步骤, VHDL 硬件描述语言

2011-07-11 15:54:27 0

0 主要内容有:第1 章实验基本知识、第2 章 PROTEUS 仿真软件快速入门、第3 章数字电路基础实验、第4 章数字电路综合设计实验、 第5章VHDL 语言基础、第6 章 数字电路的CPLD/FPGA 实现。在教

2011-09-07 16:29:53 0

0 高速数字电路设计及EMC设计!资料来源网络,如有侵权,敬请见谅

2015-11-19 14:48:57 0

0 基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计

2015-12-08 15:57:23 0

0 数字电路中的FPGA和verilog教程,好东西,喜欢的朋友可以下载来学习。

2016-01-18 17:44:30 42

42 高速数字电路设计及EMC设计(华为),下来看看。

2016-03-29 15:41:20 52

52 高速数字电路设计大全

2017-01-17 19:54:24 55

55 这本书是专门为电路设计工程师写的。它主要描述了模拟电路原理在高速数字电路设计中的分析应用。通过列举很多的实例,作者详细分析了一直困扰高速电路路设计工程师的铃流、串扰和辐射噪音等问题。

2018-09-10 08:00:00 61

61 高速数字电路设计跟低速数字电路设计不同的是:他强调组成电路的无源部件对电路的影响。这些无源器件包括导线、电路板和组成数字产品的集成电路。在低速设计中,这些部件单纯

的只是电路的一部分,根本不用多做考虑,可是在高速设计中,这些部件对电路的性能有着直接的影响。

2019-04-11 11:38:32 3581

3581

从数字电路中学到的逻辑电路功能,使用硬件描述语言(Verilog/VHDL)描述出来,这需要设计人员能够用硬件编程思维来编写代码,以及拥有扎实的数字电路功底。

2019-12-05 07:10:00 2977

2977

虽然在FPGA中,利用综合工具来可以将VHDL或者Verilog代码转化成电路。但是作为FPGA工程师而言,在没有综合工具的情况下,如何设计出数字电路呢?如果已经知道需要实现的功能的状态机,如何将它转化成数字电路呢?和设计出数字电路呢?

2020-06-17 16:33:38 2899

2899 在使用FPGA做数字电路设计的流程中,综合是其中非常重要的一个步骤。同样的设计源代码,无论是VHDL或Verilog HDL,采用不同的综合工具综合会产生不同的结果。

2020-07-24 15:47:00 1836

1836

本文档的主要内容详细介绍的是Verilog教程之Verilog HDL数字集成电路设计方法和基础知识课件

2020-12-09 11:24:19 52

52 高速数字电路设计-华为

2021-04-21 15:45:08 0

0 1. 前言 在数字电路课程中,老师在讲组合逻辑的时候,一般都会讲竞争与冒险。sky当时也听的云里雾里,没有想清楚如下问题: 1) 竞争与冒险究竟是什么东西?有啥物理现象? 2) 在数字电路设计

2021-08-09 14:43:08 2657

2657

知乎上刷到一个问题,问性能最强的编程语言是什么?看到高赞回答到是Verilog,然后在评论区就引发了一场Verilog到底算不算编程语言的争论,我觉得比较有意思,所以就也打算唠唠这个事情。 趁着最近

2021-08-23 14:30:49 5558

5558 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 、韩国、美国等区域应用很普遍。本文简要地介绍国内数字电路设计普遍使用的Verilog语言。verilog是什么。Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言

2021-11-06 09:05:57 15

15 的,呵呵。我们这里只讨论数字电路设计。实际上就是如何把我们从课堂上学到的逻辑电路使用原理图(很少有人用这个拉),或者硬件描述语言(Verilog/VHDL)来实现,或许...

2021-11-06 11:36:01 18

18 Verilog数字系统设计十二复杂数字电路设计2文章目录Verilog数字系统设计十二前言一、什么是FIFO控制器?二、编程1.要求:2.设计思路:3.FIFO控制器实现:总结前言 随着人工智能

2021-12-05 15:51:04 9

9 笔试时也很常见。[例1] 一个简单的状态机设计--序列检测器序列检测器是时序数字电路设计中经典的教学范例,下面我们将用Verilog HDL语言来描述、仿真、并实现它。序列检测器的逻辑功能...

2021-12-17 18:28:40 15

15 本书系统地介绍了数字电路的基础知识,组合和时序电路的分析、设计方法,使读者对数字系统的构成及描述有较深入的了解,达到在具有较坚实的数字电路和数字系统理论知识的基础上,独立使用可编程逻辑器件、其他

2022-06-06 16:54:09 8

8 实用电子电路设计与调试数字电路教材资料免费下载。

2022-04-07 14:46:38 26

26 黑魔书 351页- 高速数字设计PDF版,华为内部数字电路设计教材

2022-06-08 14:33:25 0

0 高速数字电路设计教材-华为

2022-06-13 14:55:54 0

0 数字电路设计是数字电路最为关键及重要的一步,今天我们将从各个流程为大家介绍完整的数字电路设计!

2022-07-10 17:14:16 6046

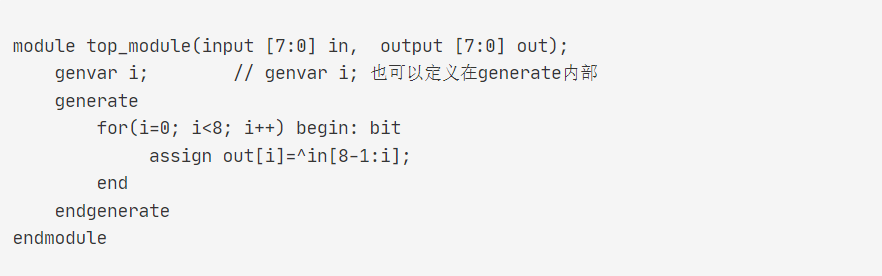

6046 HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

2022-08-31 09:06:59 1168

1168 眼图医生(Eye Doctor)是力科于2006年推出的用于高速串行数字电路设计的强大工具,包括了虚拟探测(virtual probing)与接收端均衡(receiver equalization

2022-09-30 09:08:41 976

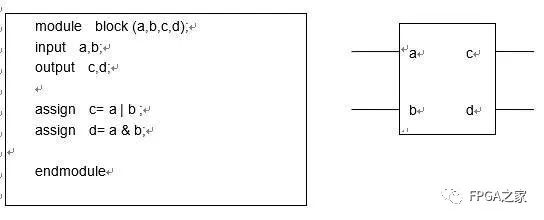

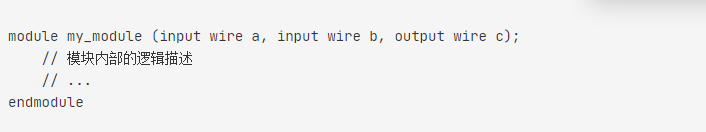

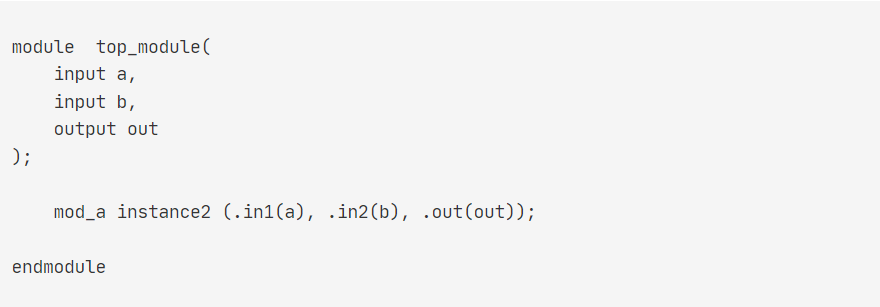

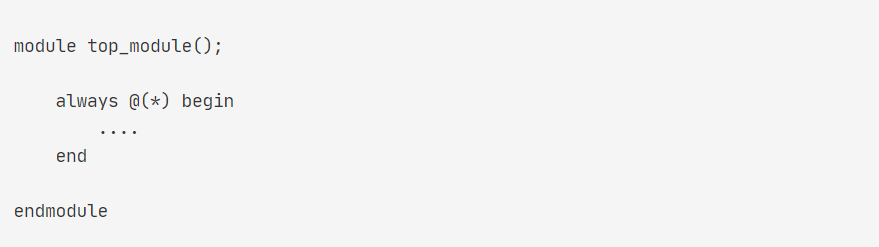

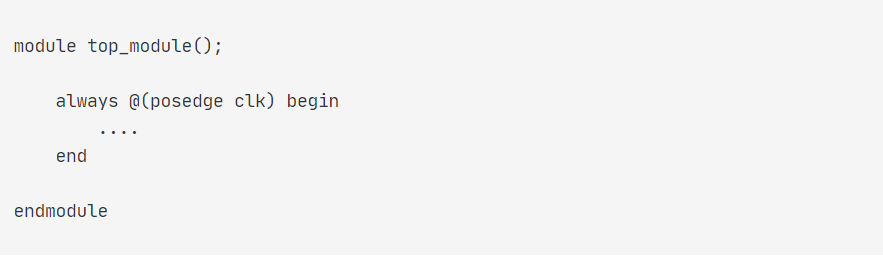

976 Verilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一种行为描述的语言也是一种结构

2023-05-22 15:52:42 557

557

Verilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一种行为描述的语言也是一种结构

2023-05-22 15:53:23 531

531

Verilog 是一种用于数字逻辑电路设计的硬件描述语言,可以用来进行数字电路的仿真验证、时序分析、逻辑综合。

2023-06-10 10:04:44 786

786

。这些测试工具包括测试杆,逻辑分析仪,示波器,多用途测试仪等等。下面我们将详细介绍这些测试工具。 1.测试杆 测试杆是一种用来测试数字电路芯片的工具。它包含了一系列的连接引脚和信号线。测试杆可以将芯片引脚连接到测试设

2023-09-19 16:33:13 570

570 高速数字电路设计

2022-12-30 09:22:18 19

19 高速数字电路设计教材-华为

2022-12-30 09:22:18 41

41 电子发烧友网站提供《FPGA/CPLD数字电路设计经验分享.pdf》资料免费下载

2023-11-21 11:03:12 3

3 Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。与其他编程语言相比,Verilog具有与硬件紧密结合的特点,因此其接口机制也有一些与众不同之处。本文将详细介绍Verilog与其他编程

2024-02-23 10:22:37 145

145

正在加载...

电子发烧友App

电子发烧友App

评论