Synopsys针对ARMv8处理器的VDK系列使采用ARMv8处理器产品的操作系统移植、固件和驱动器开发在开发板提供前一年就可开始,半导体厂商可以为他们的SoC创建一个VDK,以供他们自己及其客户与伙伴的软件开发人员使用.

2013-03-22 09:11:15 967

967

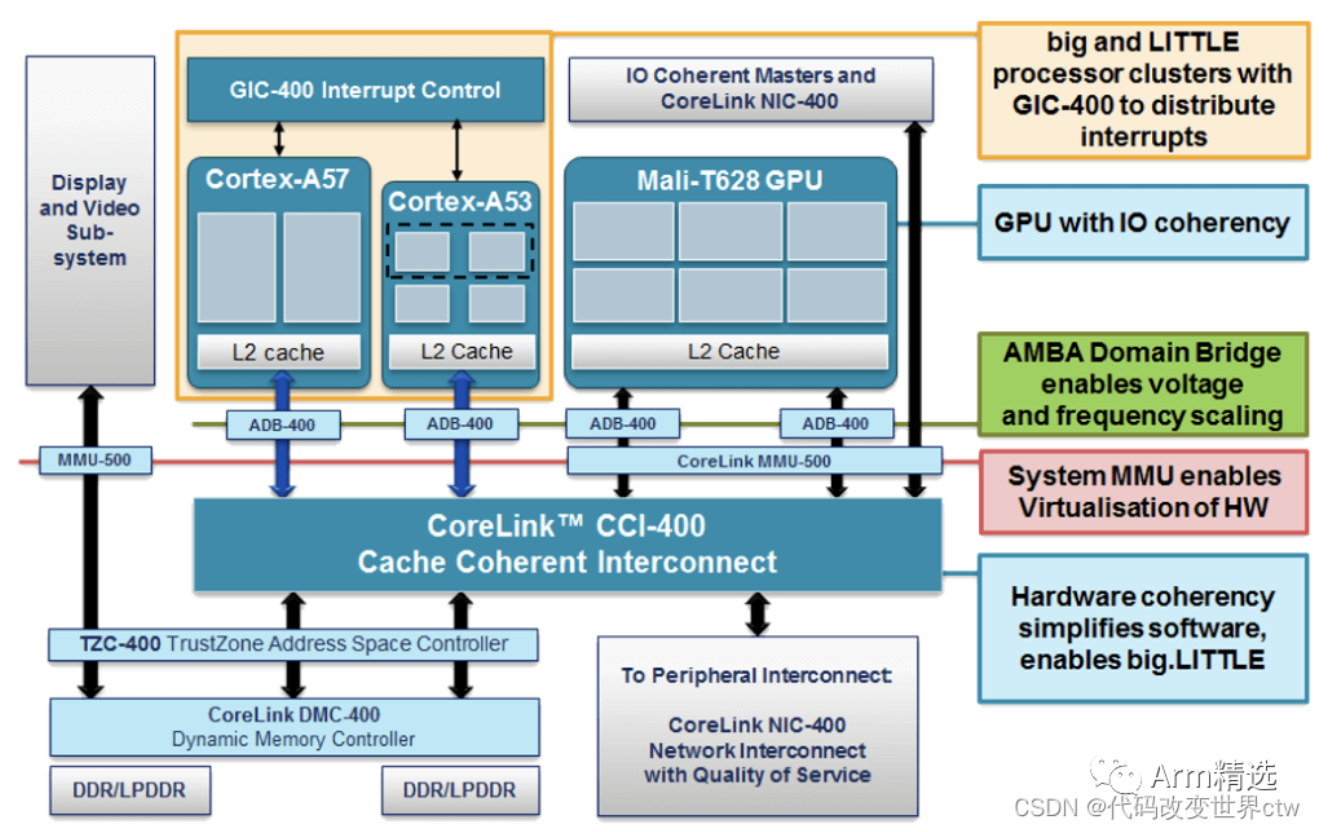

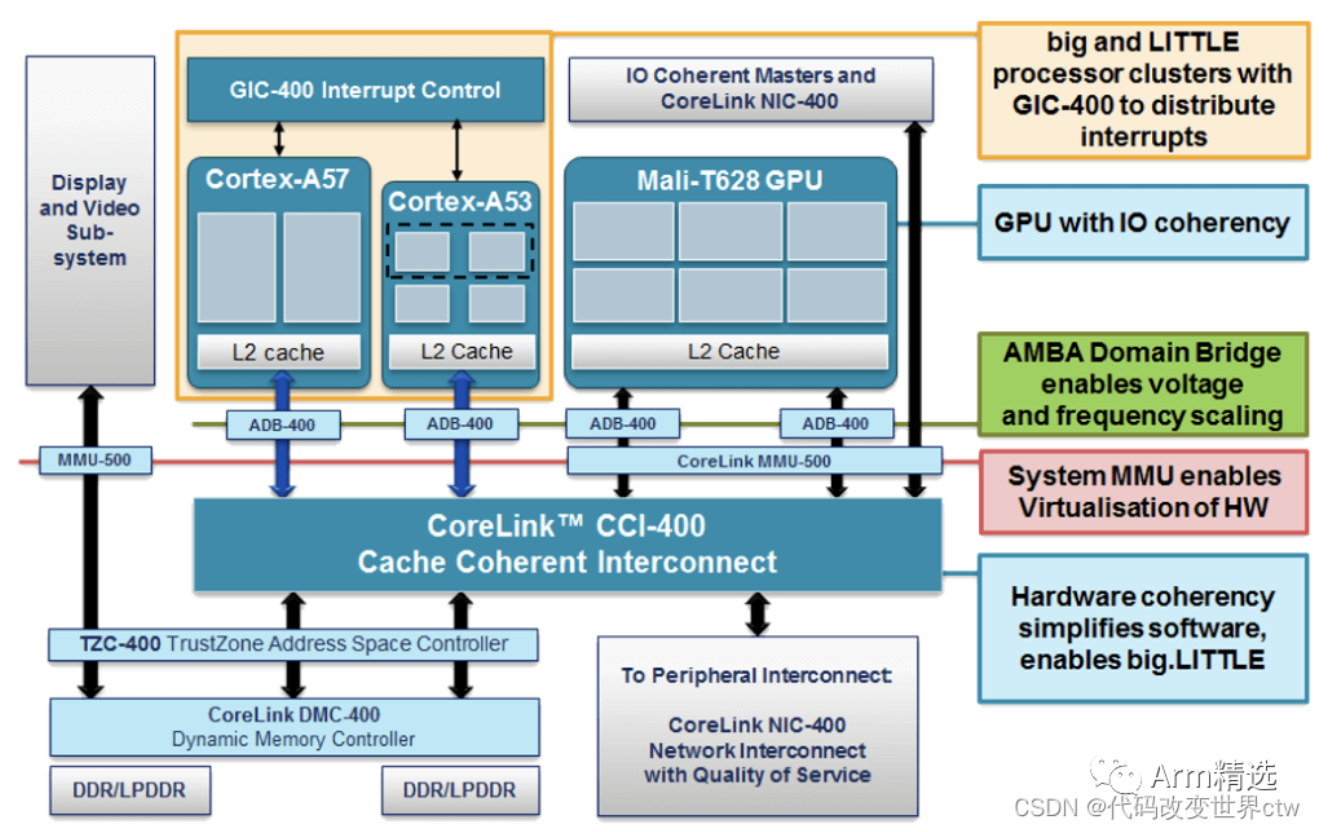

ARMv8是一个真正意义上的64位,同时这个64位的架构当中加入了或者说提供了32位的支持。Cortex-A57是ARM最先进、性能最高的应用处理器,而Cortex-A53不仅是功耗效率最高的ARM应用处理器,也是全球最小的64位处理器。

2013-03-22 09:26:18 14860

14860

本文从ARMv8-A产生的背景开始,对它进行一个简单的介绍,使大家从整体上,对ARMv8有一个简单的了解。

2020-10-08 17:02:00 9749

9749

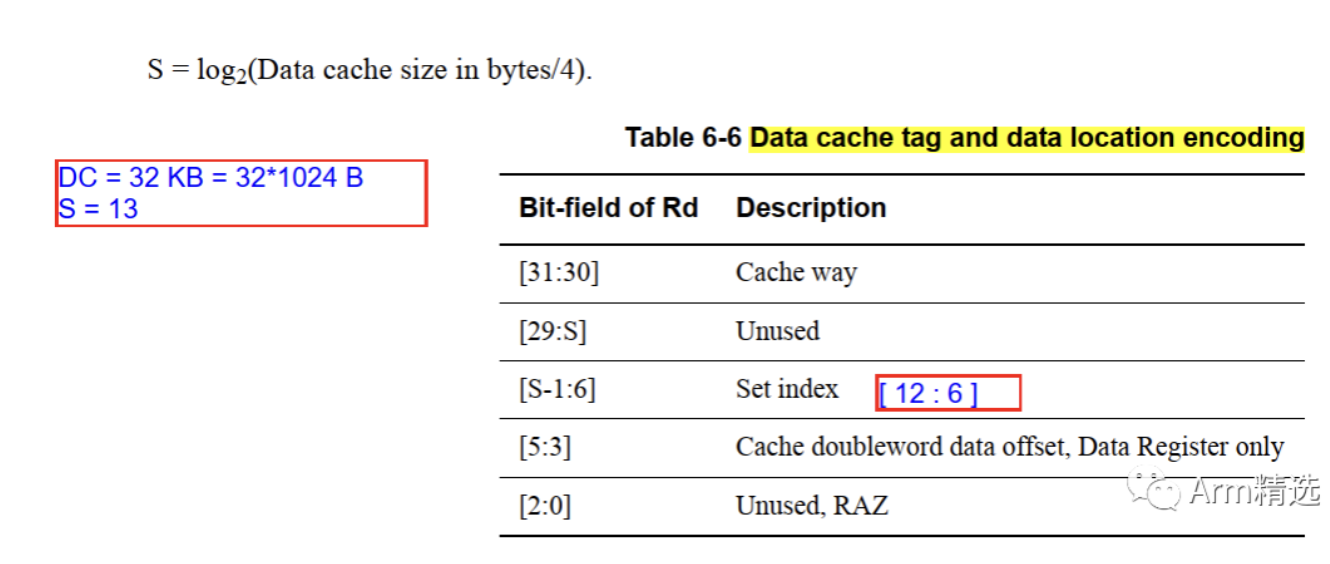

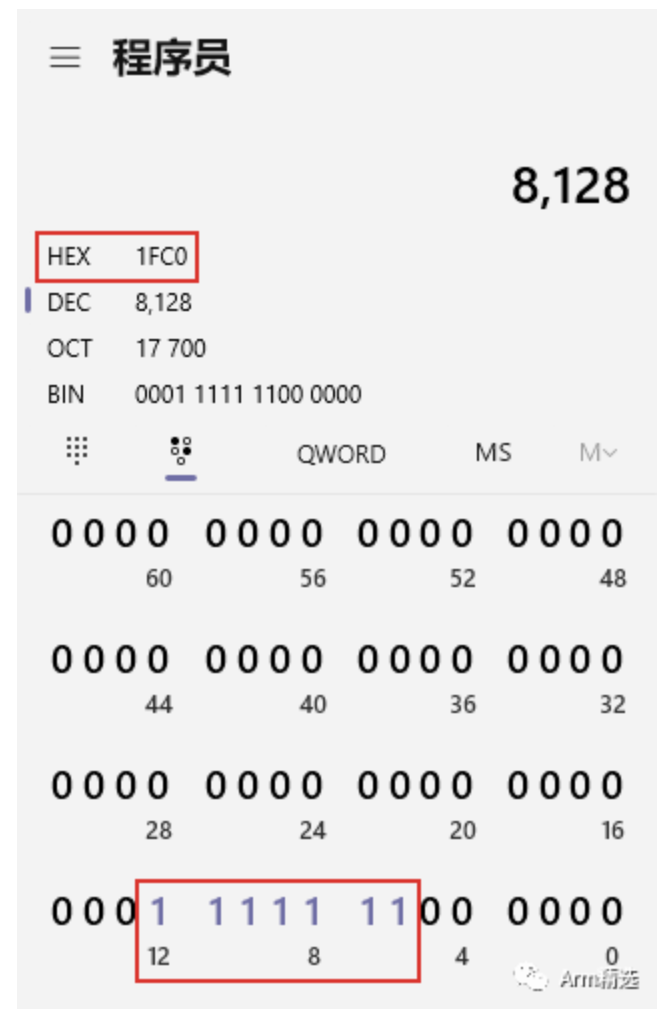

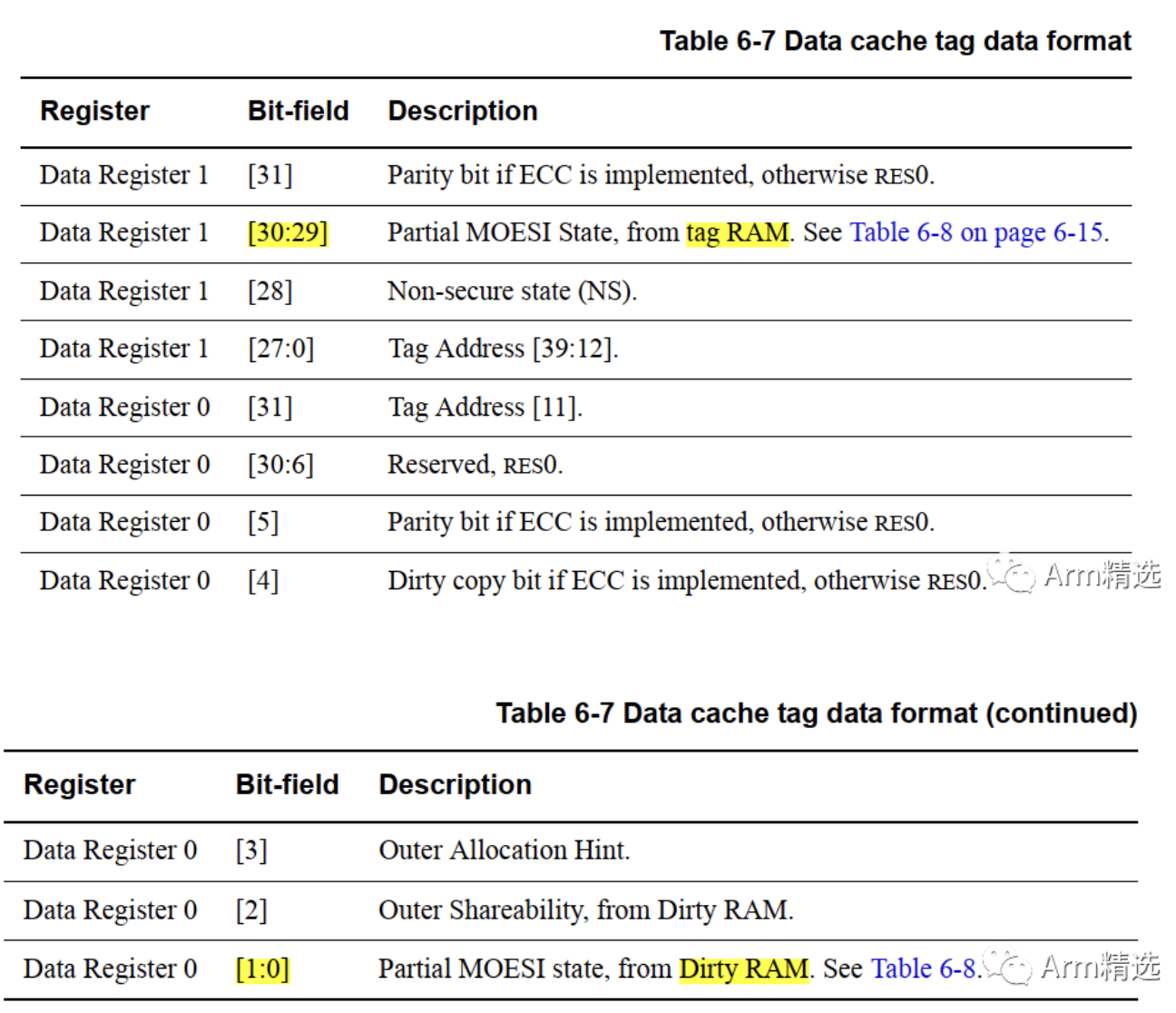

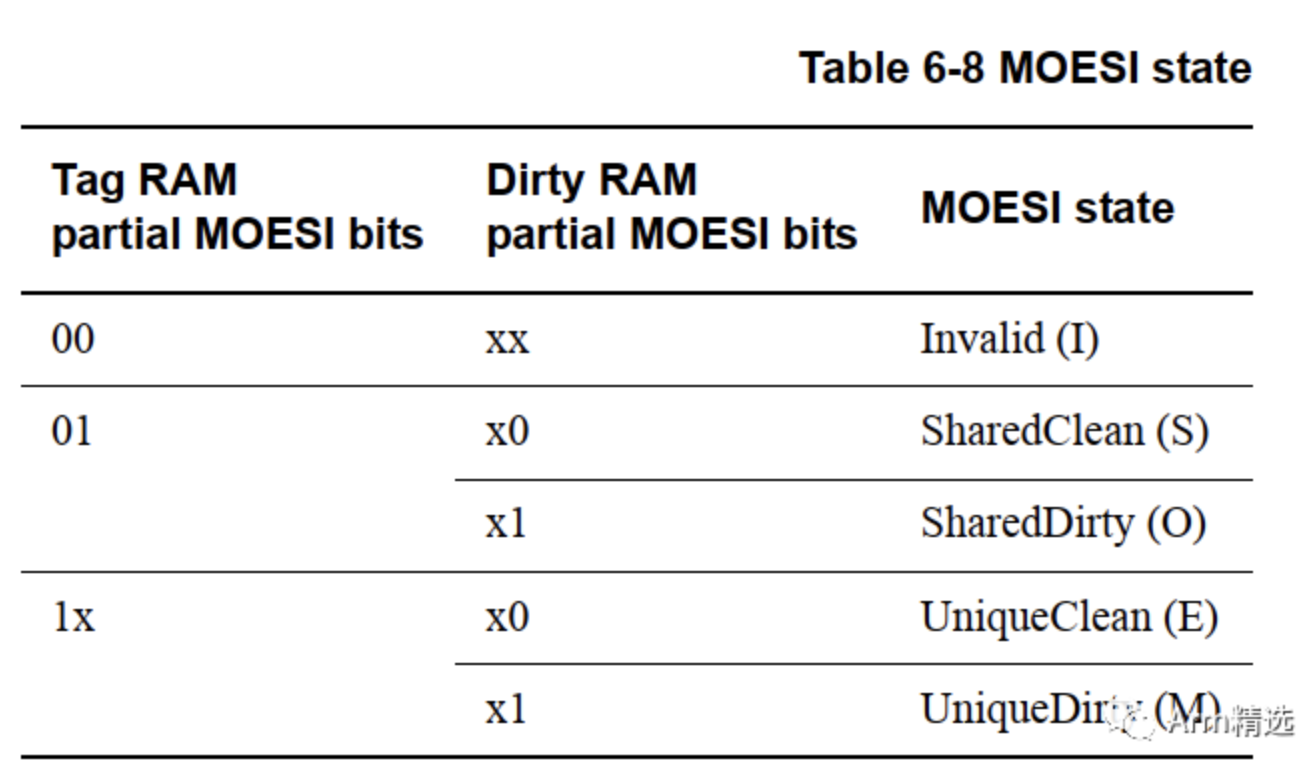

A53的L1 Data cache遵从的是MOESI协议,如下所示在L1 data cache的tag中存有MOESI的标记位。

2023-09-01 15:01:21 5024

5024

背景:64位平台需要使用armv8版本编译so。调试:从armv7版本配置上修改CMAKE_ANDROID_ARCH_ABIarmeabi-v7a为arm64-v8a报如下错误:Make Error

2022-11-11 17:57:25

请问:

1、如果将L1D CACHE设置为32KB,L1P CACHE设置为32KB,L2 CACHE设置为0KB;

在core的LL2中定义了两个数组,out1占用32KB存储空间,out2占用

2018-06-21 13:28:12

和 T32 不同,没有 4 或 8 字节的隐含偏移量。2、adrp和adradrp地址读取指令,它将基于PC的相对偏移的地址读到目标寄存器中ADR指令使用格式:adr register exper编译

2023-02-23 16:45:47

1. ARMv8 Uboot支持MMU和Cache说明由于Uboot是第一次在我司平台方案上支持,因此存在很多不完善的地方,在启动过程中,客户反馈Uboot在内核解压(gzip压缩内核)这一块耗时

2022-05-23 16:19:17

目前正在学习ARMv8 Arch Ref Manual.D1.10.2 Exception vectors有点疑惑:Table D1-6 定义了一个Vector Table应该具有的items我们

2022-08-17 15:54:07

本文档介绍ARMv8-A[ARMv8]的可伸缩向量扩展[SVE]对在应用程序处理器上以安全状态执行的软件的影响。

本文档考虑了部署现有ARMv8-A TrustZone软件对实施SVE的系统的影响,并为实施SVE的系统更新该软件和设计未来的安全软件提供了建议

2023-08-23 06:17:45

Armv8体系结构有几个不同的配置文件。这些配置文件是体系结构的变体针对不同的市场和用例。Armv8-M体系结构就是其中之一配置文件。

Arm定义了三个体系结构配置文件:应用程序(A)、实时(R

2023-08-08 06:18:24

错误检测和校正技术可用于帮助减轻硅器件。ARMv8-M处理器包括一些功能,可以检测这些错误。

在硅器件中,出现错误的原因可能是:

•软件错误。

•使用错误,条件在正常操作条件之外。例如温度或电源电压

2023-08-02 06:28:02

)、从 base地址处读取一个数字,存放到Wt寄存器中; (2)、将Monitor的状态变成exclusiveSTXR Ws, Wt, [base{,#0}](1

2023-02-21 15:26:27

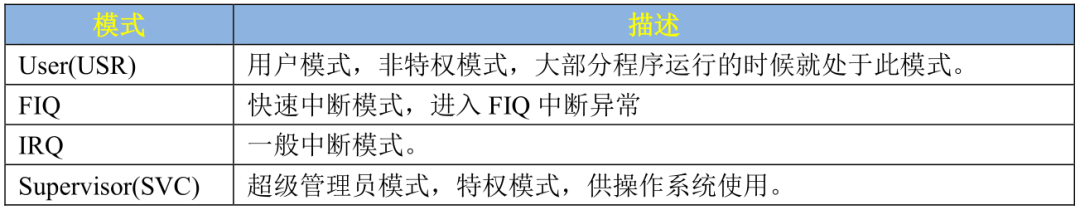

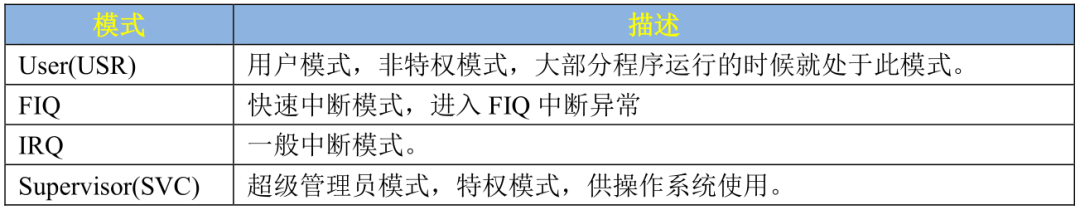

Armv8 OverviewARMv7与Armv8的升级示意如下:Aarch64指令集Aarch64的32个通用寄存器引用和描述如下,与Aarch32寄存器相比如下,在ARM 32位系统中,函数参数

2022-05-13 10:31:20

ARM结构,一直都在升级,到目前,已经升级到了ARMv8。ARMv8,提出了很多新的概念。一、两种执行状态在ARMv8中,引入了两种执行状态:◾ AArch32◾ARMv7的升级版◾ A32(ARM

2022-04-06 10:49:28

指令ARM 架构在特定点使用屏障指令来强制指定访问顺序和访问完成。在一些其他架构中,也有类似的指令被称为 fence。ARMv8 架构提供了三种类型的屏障指令:指令同步屏障(ISB)数据内存屏障

2022-03-29 09:56:23

随着开发工作逐渐迁移到 ARMv8 的 64 位平台,因此有必要尽快熟悉 ARMv8 架构。ARMv8 与先前较为熟悉的 ARMv7 架构有较大变化,其中非常重要的一点是支持了 A64 指令集

2022-03-21 14:50:39

stack,函数调用过程中用来保存CPU状态的存储空间就叫调用栈。ARM体系结构对64位的支持从ARMV8开始,V7及以前的版本并不支持。V8的寄存器及指令集都发生了较大的变化,导致V7之前版本的调用栈

2022-05-13 10:36:15

ARMv8架构中,定义了一个系统定时器(system timer),并且指定了这个系统定时器,需要实现的寄存器,以及各个寄存器的偏移。系统寄存器中,包含一个系统计数器,以及一些控制寄存器,状态寄存器

2022-04-01 15:30:21

本章总结了本增补与ARMv8 体系结构参考手册。

2023-08-08 07:53:09

Units (AMU)的虚拟化支持总结这篇博文简要介绍了Armv8-A构架中Armv8.6-A 引进的最新功能。这些功能提供了未来CPU在机器学习神经网络,虚拟化这些领域的增强,和改进处理效能的矩阵乘

2022-07-29 15:29:42

本指南主要介绍Armv7系统和Armv8系统中跟踪的高级视图,最高可达Armv8.4版本。

该指南涵盖:

•跟踪是什么以及如何使用

•跟踪体系结构是如何定义的,以及它如何映射到不同的跟踪组件实现

•在Arm系统中可以看到哪些跟踪组件

•一些跟踪系统的示例

2023-08-02 06:11:37

各位专家:

我之前把数据放在ddr中,1024点fft需要40万个周期,后来放在L2中,只需要10000左右的周期。但是还有其他的数据较大,只能放在ddr中,那请问怎么才能

2018-06-21 15:10:16

分别是指向 0x00、0x40 和 0x80 的指针,则此循环将导致对cache line index 0位置的颠簸。第一次读取地址 0x40 时,它不会在cache中,因此会发生linefill

2022-06-15 16:16:16

前面的文章中经常提到Armv8-A。那么到底Armv8-A是什么东西呢?这个问题要说简单也很简单,要说复杂也很复杂。今天我们花点时间来简单研究一下。众所周知,ARM是一家设计并授权处理器和相应IP

2022-08-22 15:39:32

CacheUser Guide文档中的34页2.3章节中的CACHE_enableCaching(CACHE_MAR128)中的CACHE_MAR128到底在哪啊?始终找不到,也不知道它对应的是什么数字?谁能给小弟解释一下!不胜感激啊!

2018-06-19 06:59:46

请问如何理解ARMv8内存属性device中,引入的Re-Ordering概念,感觉实际意义不大。或者可以举个例子来说明这个概念的必要性。谢谢!

2015-07-28 17:19:02

的semaphore机制的资料,我看了TMS320C6678的datasheet中的7.26节semaphore2中的内容,觉得讲得太简单了,看程序还是看不明白。 再请问一遍专家,CACHE_wbL1d()函数什么意思呢?多谢!

2018-06-25 05:45:41

吗?有的话麻烦您详细讲解以下。■三:RAM映射到cache的问题 请问怎么才能控制,操作RAM和cache的映射关系呢?以上问题,麻烦您讲解一下。

2018-06-21 04:06:04

ARMv8-A是针对应用配置文件的最新一代ARM架构。

在本书中,名称ARMv8用于描述整个体系结构,它现在包括32位执行状态和64位执行状态。

ARMv8引入了使用64位宽寄存器执行的能力,但提供

2023-08-22 07:22:29

本手册中的体系结构描述使用了与Armv8体系结构相同的术语。有关该术语的更多信息,请参阅Armv8-A架构配置文件Armv8 Arm®架构参考手册A部分的介绍。此外,在适当的情况下使用AArch64

2023-08-11 07:45:48

7Simulation Models:updated to Fixed Virtual Platforms 8.3.2 releaseadded ARMv8 simulation model for ARMv8

2014-10-14 17:23:48

is upgraded to version 7Simulation Models:updated to Fixed Virtual Platforms 8.3.2 releaseadded ARMv8

2014-10-15 10:31:38

is upgraded to version 7Simulation Models:updated to Fixed Virtual Platforms 8.3.2 releaseadded ARMv8

2014-10-14 17:41:16

is upgraded to version 7Simulation Models:updated to Fixed Virtual Platforms 8.3.2 releaseadded ARMv8

2014-10-15 10:54:51

is upgraded to version 7Simulation Models:updated to Fixed Virtual Platforms 8.3.2 releaseadded ARMv8

2014-10-15 10:56:10

我在armv8下(arch64)下使用neon中遇到一些疑问,希望得到大家解答1、在armv8下是编译的时候使用了O3优化,相关计算就会自动使用neon吗2、同样一段计算函数,计算速度是不是NEON

2022-09-08 11:34:29

请问一下c6000 dsp的 cache line有多长?也就是一个数组,取其中一个元素,会把这个元素附近的多少个元素带入到缓存中?是加载这个元素两边的数据,还是后面的数据?多谢了!

2020-05-22 15:06:32

到底什么是Cortex、ARMv8、arm架构、ARM指令集、soc?一文帮你梳理基础概念【科普】1. 从0开始学ARM-安装Keil MDK uVision集成开发环境

2021-12-14 08:20:33

的硬件。在本节中,我们总结了一篇文章,它概述了ARMv8服务器使用ACPI背后的原因。ACPI的字节码(AML)允许平台对硬件行为进行编码,而DT(device tree)明确地不支持这一点。对于硬件

2022-04-21 09:48:12

我正在尝试访问ARMV8系统寄存器icc_sre_el2,但遇到未知或丢失的系统寄存器错误。使用列表中的其他寄存器时,构建成功。但是任何带有icc_,ich_前缀的东西都会失败。我需要做什么来解决这个问题?

2022-08-30 15:19:44

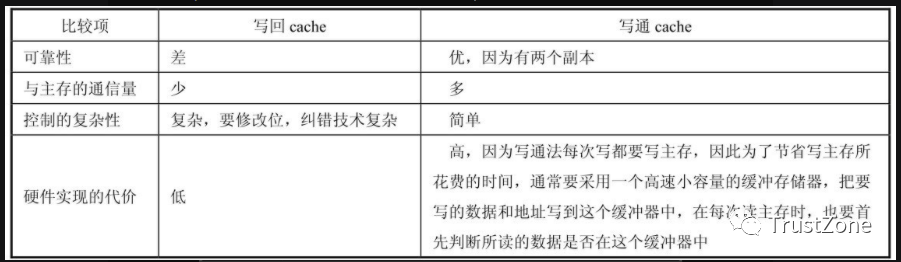

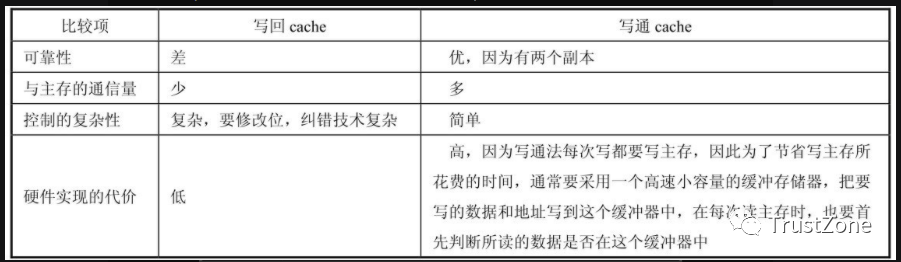

节数据的时候,如果cache缺失,那么cache控制器会从主存中一次性的load cache line大小的数据到cache中。例如,cache line大小是8字节。CPU即使读取一个byte,在

2022-04-21 11:10:49

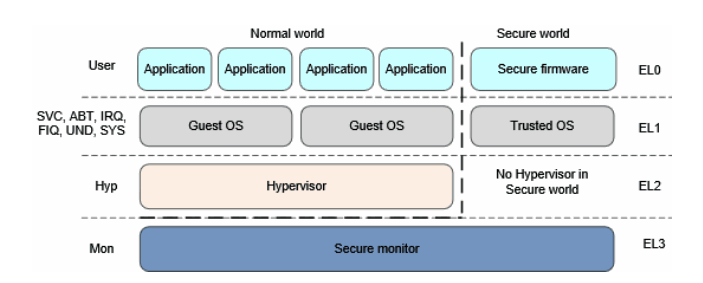

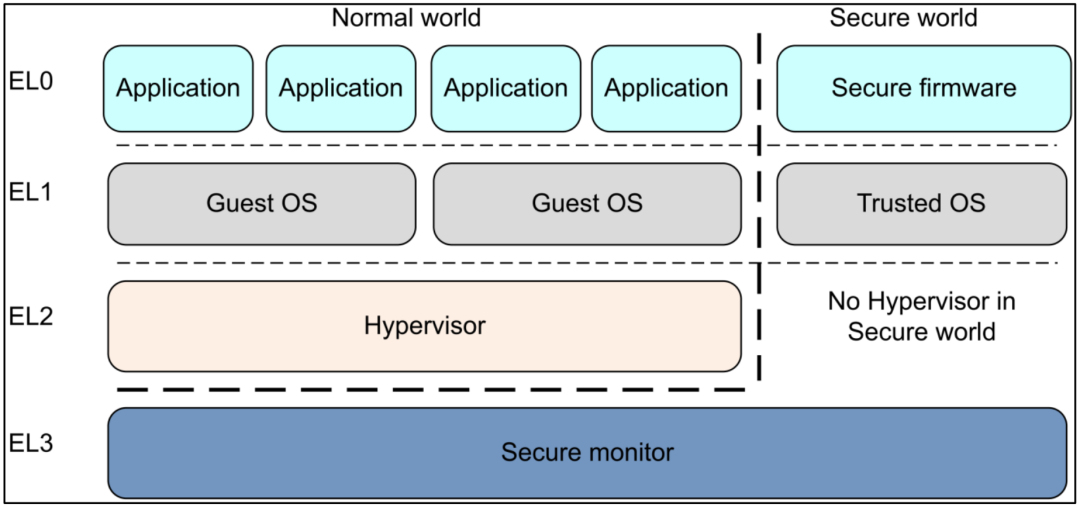

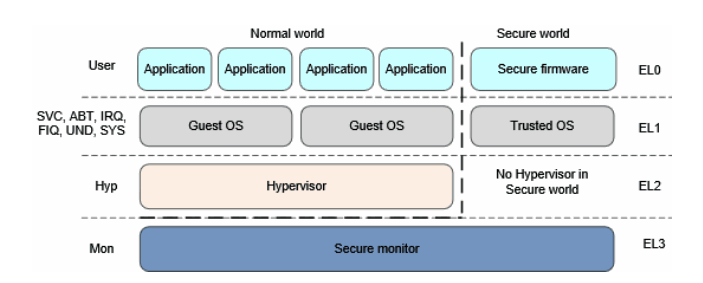

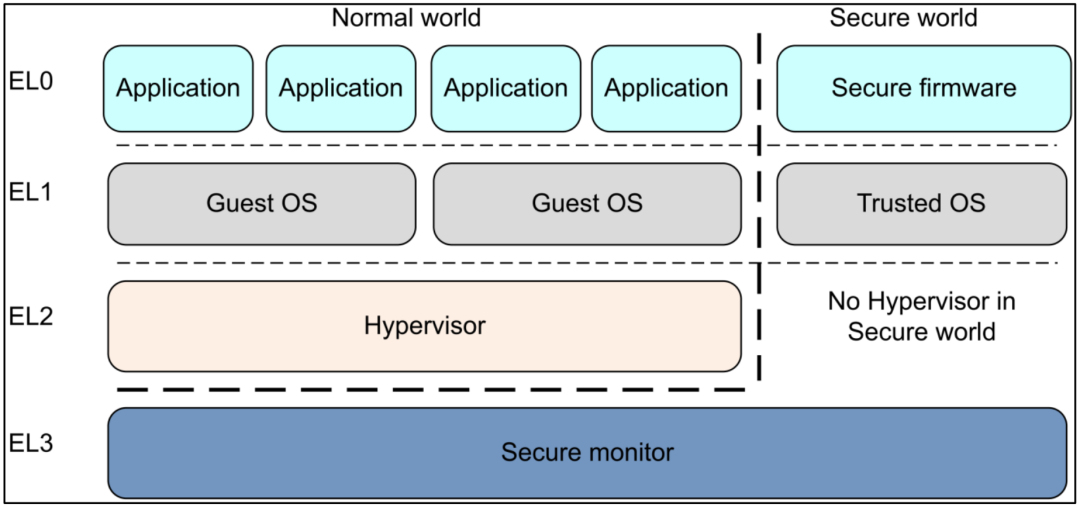

ARMv8-a架构是由哪些部分组成的呢?为何ARMv8-a架构要引入EL3呢?

2022-03-02 09:12:53

1、ARMv8/aarch64下TSC(Time Stamp Counter)读取方法在 x86 中,对 Time Stamp Counter(对计时码表)非常清晰,通过我们的 CPU Cycle

2022-06-02 17:22:57

CACHE_getMemRegionInfo (129, &pcx, &pfx); 读取pcx的值 仍然是1,所以没起作用。怀疑是当前模式是user mode,而修改MAR寄存器需要

2018-12-28 11:12:02

帮忙给解答一下一个基本概念,cpu在访问数据时,如果数据不在L1D和L2中,就需要从DDR等外设中取数,文献中说过,“cache会prefetch读取cache_line长度的地址,保证连续的地址上

2018-06-21 17:31:26

执行代码以对其进行初始化。让CPU复位引脚产生复位信号,CPU进入复位状态,并重新启动。软件产生的异常ARMv8架构提供了三种软件产生的异常,这些异常通常是指软件想尝试进入更高的异常等级而造成的错误

2022-05-23 15:51:36

各位大神,armv8架构中,如果Arch32要去切换到Arch64,是如何运作的?状态会清空吗?

2022-06-06 16:13:32

关于cache配置的问题,在L1或者L2中可以配置为cache或者SRAM,请问cache的配置与什么有关?有一些参考资料么?谢谢没有搞清楚应当如何配置cache,以及配置多大的cache,求指导!!!

2018-07-25 09:24:32

此教程将概述使用 CoreSight Access 工具( CSAT) 进行低级别调试的情况, 其目标为 Armv8 。 低级别调试允许您操作单个登记器, 包括通常无法为应用程序级别调试器访问

2023-08-28 06:28:31

指令集D--支持片上调试M--支持快速乘法器I--支持Embedded lCE,支持嵌入式跟踪调试E--支持增强型DSP指令J--支持JazelleF--具备向量浮点单元VFP-S --可综合版本ARMv8不同系列及应用场景原作者:Jack20华为云社区

2022-06-16 15:26:58

道某些逻辑是在完成什么工作。在armv8中,u-boot使用arch/arm/cpu/armv8/u-boot.lds进行链接。u-boot-spl和u-boot-tpl使用arch/arm/cpu

2022-05-23 15:59:50

boot参数,进行地址无关fixed,系统寄存器复位,底层平台相关初始化等,启动代码位于arch/arm/cpu/armv8/start.S,入口地址为_start。1.1 启动前为后续流程做的一些平台

2022-05-23 16:05:34

1.对于单核来说,没有cache无效/写回一说,因为无论在cache中还是在ram中值都是对应最新的值是吧?2.在调试6678过程中,发现一个问题.。过程是:Core0与Core1双核运行,共享

2019-01-08 10:57:11

在本教程中,您将学习如何使用Arm Compiler 6构建Hello World,并在Armv8固定虚拟平台(FVP)用Arm编译器6构建Hello World并在Armv8 Fixed

2023-08-08 07:41:52

本教程概述了如何使用CoreSight Access Tool执行低级调试(CSAT)与Armv8目标。低级调试允许您:

•操作单个寄存器,包括不能正常访问的调试寄存器

应用程序级调试器。

•执行

2023-08-02 10:27:29

如何使用DMA在UART上读取数据的信息呢?在STM32中有哪几种模式呢?分别有何优缺点呢?

2022-01-27 07:18:47

CPU Cache是什么?如何查看自己电脑CPU的Cache信息呢?

2021-10-19 08:42:39

请问,用I.MX6UL开发板OKMX6UL,使用Linux的情况下,如何获取CPU中L1/L2的Cache状态和大小;如何禁用和使能Cache?

2022-11-29 06:37:16

总线结构)总线接口连接到ASB总线上去访问内存。Cache由Line组成,Line是Cache进行块读取和替换的单位。 Writer Buffer是和DCache相逆过程的一块硬件,目的也是通过减少

2017-08-19 22:42:08

什么是交叉编译呢?怎样在PC机器上编译RK3566 ARMv8平台的代码呢?

2022-03-02 09:49:04

ARMv8,定义了异常等级,来进行权限控制。分别是EL0,EL1,EL2,EL3。对于AArch32,ARMv8定义了9种PE模式,来确执行权限,不使用EL。对于AArch64,不支持PE模式

2022-04-06 10:57:55

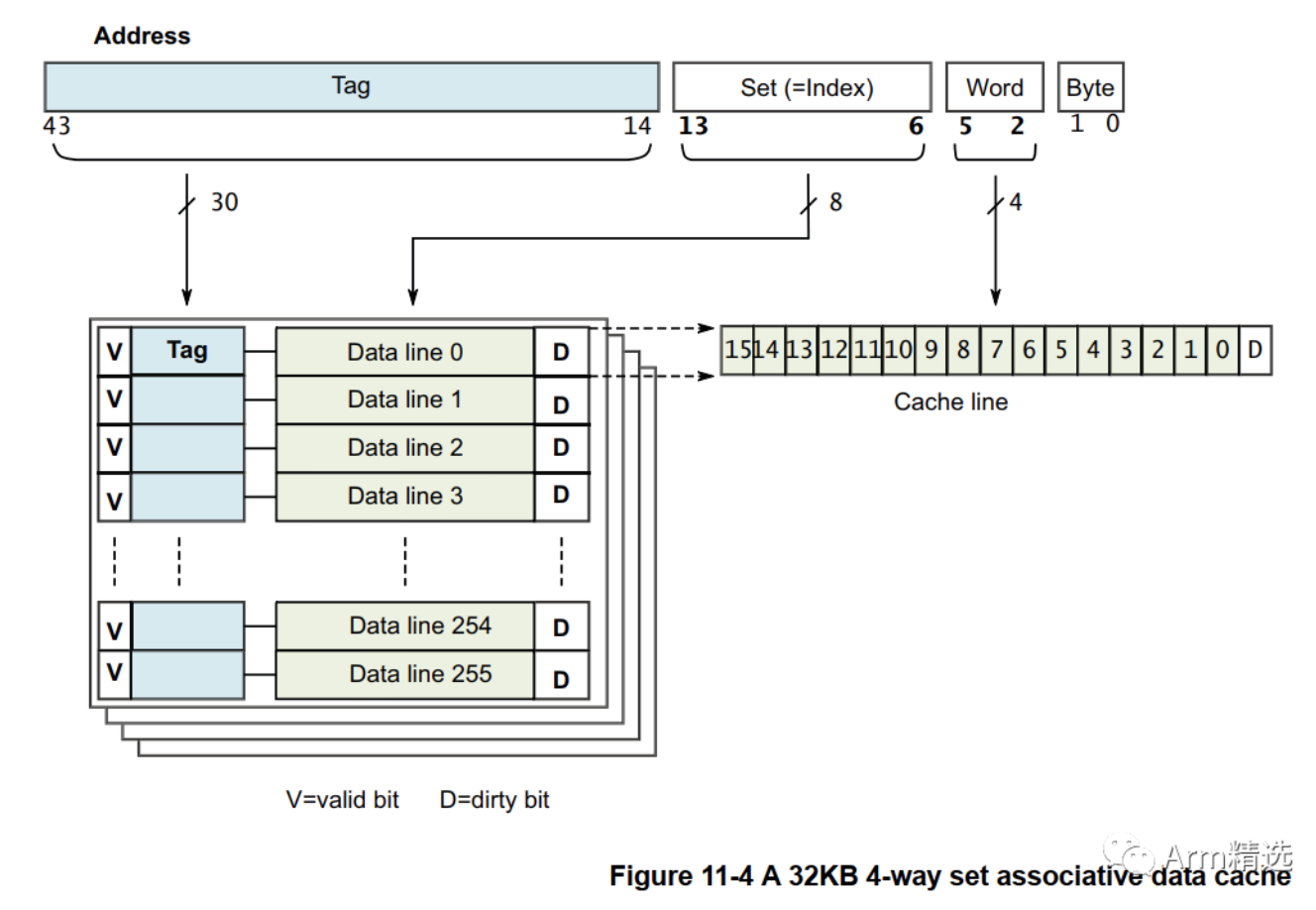

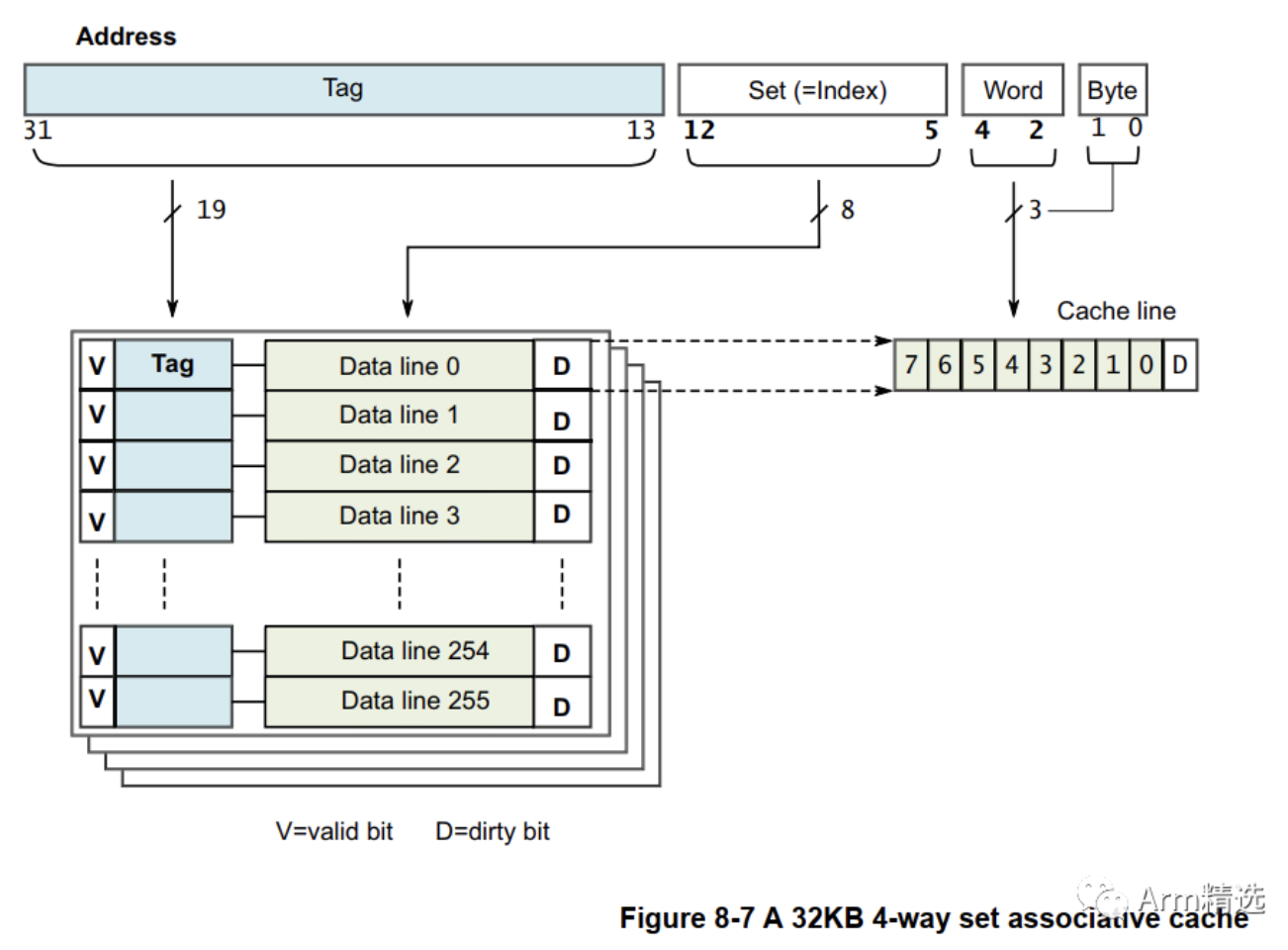

,指令cache和数据cache是同一个,在优化后的哈弗架构中使用独立的指令cache(I-cache)和数据cache(D-cache),即可以同时访问指令和数据。在ARMv8处理器中,L1

2022-06-15 16:30:39

什么是Instructions Cache/IMM/ID

Instructions Cache: (指令缓存)由于系统主内存的速度较慢,当CPU读取指令的时候,会导致CPU停下来

2010-02-04 11:51:01 583

583 什么是Cache

英文缩写: Cache

中文译名: 高速缓存器

分 类: IP与多媒体

解 释: 信息在本地的临时存储

2010-02-22 17:26:39 948

948 处理器授权大厂ARM于上周(10/27)公布最新处理器规格ARMv8架构,一举将其产品线推入64位元市场。ARMv8以ARMv7架构为基础,并内含64位元指令集,预估可将32/64位元应用优势极大化。

2011-11-01 09:32:29 1310

1310 无晶圆网络芯片公司Cavium宣布,计划提供一个基于全定制内核设计的的家用多核系统芯片,该芯片是由ARM公司基于ARMv8 64位指令集架构基础上设计和实现的。该公司表示,该芯片将针对“

2012-08-02 16:57:27 1383

1383 ARMv8系列,是ARM史上第一个64位的系列,Cortex-A 57是为智能手机和超级手机功耗级别提供最新的性能,超级手机指的是三星的Glaxay3或者是苹果的iPhone5手机这级别的手机

2016-08-05 15:19:11 1251

1251 ARMv8架构是首个包括64位执行模式的ARM架构,允许处理器将64位执行模式与32位执行模式相结合。开发该版本ARM指令系统的关键技术之一是将ARM处理器工艺的高能效优势融入64位计算,并获得更大的可用虚拟地址空间。ARMv8架构在异常及异常处理方面引入一种全新机制。

2017-09-12 19:01:00 11

11 查看intel 手册可以得到每个字节的解释,ebx寄存器中低八位查表得到如图3所示相关信息,3级cache 容量6M,12路组相连(每组有12个line),每个line大小为64 字节。其它信息查表得到如下

2018-08-15 14:25:41 3646

3646

当CPU开始访问地址0020h时,假设cache已经被完全被设定无效了(invalidated),即没有cache line包含有效数据。

2018-09-09 10:39:57 7601

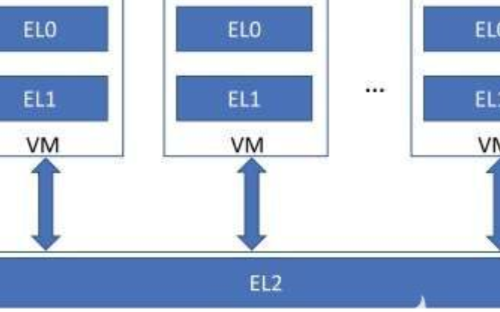

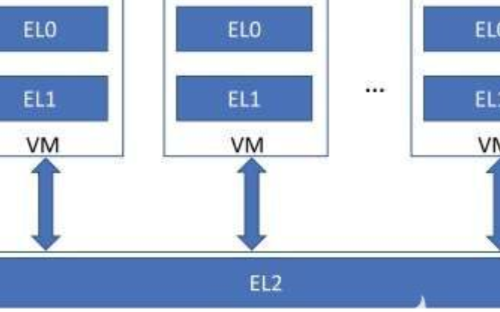

7601 ARMv8处理器CPU 基于ARMv8的系统中的虚拟化工具在这些系统中起着特殊的作用,它由几个组件组成,虽然ARMv7具有特殊的CPU模式来运行虚拟机管理程序作为扩展,但在ARMv8中,它已成为架构

2018-10-13 20:00:01 690

690

编者按 :最近,华为海思的鲲鹏、麒麟等系列处理器成为了网上热议的话题,因为它们使用了ARM的指令集,如果被禁用了,华为的ARM处理器会怎样?答案是:华为已经获得了ARMv8的永久授权,可完全自主

2019-01-27 15:46:01 1779

1779 基于ARMv8的系统中的虚拟化设施在这些系统中扮演着特殊角色,并且由几个组件组成。尽管ARMv7具有特殊的CPU模式来运行虚拟机监控程序作为扩展,但在ARMv8中,它已成为体系结构的一部分,并且

2020-05-13 10:48:01 1875

1875

②. 1 号核心读取变量 A,由于 CPU 从内存读取数据到 Cache 的单位是 Cache Line,也正好变量 A 和 变量 B 的数据归属于同一个 Cache Line,所以 A 和 B 的数据都会被加载到 Cache,并将此 Cache Line 标记为「独占」状态。

2020-12-11 16:44:28 2843

2843

英国芯片设计公司Arm周二发布了Armv9,这是其在2011年发布Armv8之后十年来首次推出新的芯片架构。Arm表示,与以前的架构相比,Armv9提供了三大主要改进,即安全性更高,更好的AI性能,以及总体上速度更快。

2021-04-01 15:17:12 2081

2081 Cache 的本质是由 Linux 内核管理的内存区域。我们通过 mmap 以及 buffered I/O 将文件读取到内存空间实际上都是读取到 Page Cache 中。 1.2 如何查看系统

2021-10-20 14:12:41 5320

5320

由于写入数据和读取指令分别通过 D-Cache 和 I-Cache,所以需要同步 D-Cache 和 I-Cache,即复制后需要先将 D-Cache 写回到内存,而且还需要作废当前的 I-Cache 以确保执行的是 Memory 内更新的代码

2022-12-06 09:55:56 1163

1163 新的Armv9兼容CPU所承诺的最大的新功能可能是开发人员和用户可以立即看到的——SVE2作为NEON的后继产品。

2023-03-10 14:02:21 3791

3791 新的Armv9兼容CPU所承诺的最大的新功能可能是开发人员和用户可以立即看到的——SVE2作为NEON的后继产品。 可伸缩矢量扩展(SVE)的于2016年首次亮相,并首次在富士通的A64FX CPU内核中实现,该芯片已为日本排名第一的超级计算机Fukagu提供支持。

2023-03-29 14:02:42 392

392 ARMv8基本概念

(1)执行状态(execution state):处理器运行时的环境,包括寄存器的位宽、支持的指令集、异常模型、内存管理及编程模型等。ARMv8体系结构定义了两个执行状态:

AArch64:64位的执行状态

提供31个64位的通用寄存器

2023-04-16 10:45:38 4303

4303 rk3588是armv8吗?rk3588 硬件资料 RK3588是一款高性能处理器,是Rockchip公司推出的最新芯片。本文将详细介绍RK3588的硬件资料。 首先,我们需要了解一下RK3588

2023-08-21 17:32:46 1744

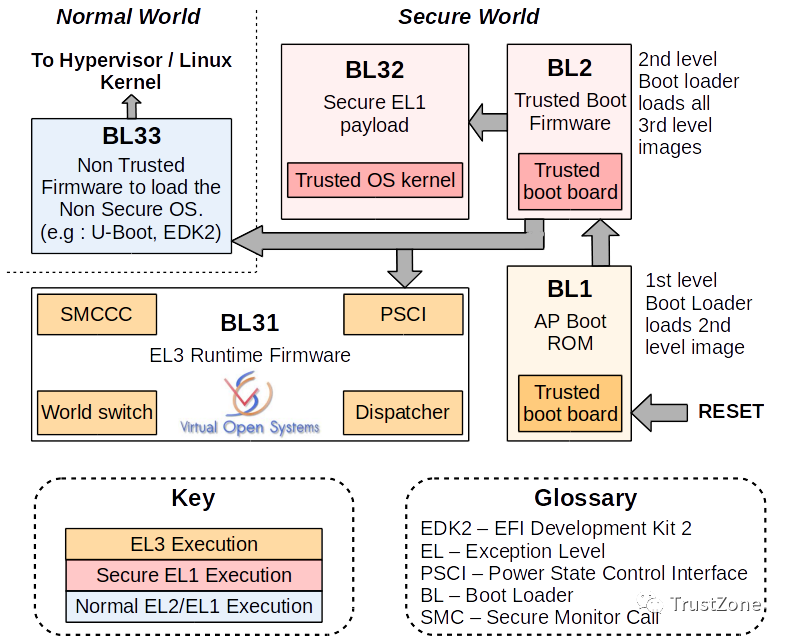

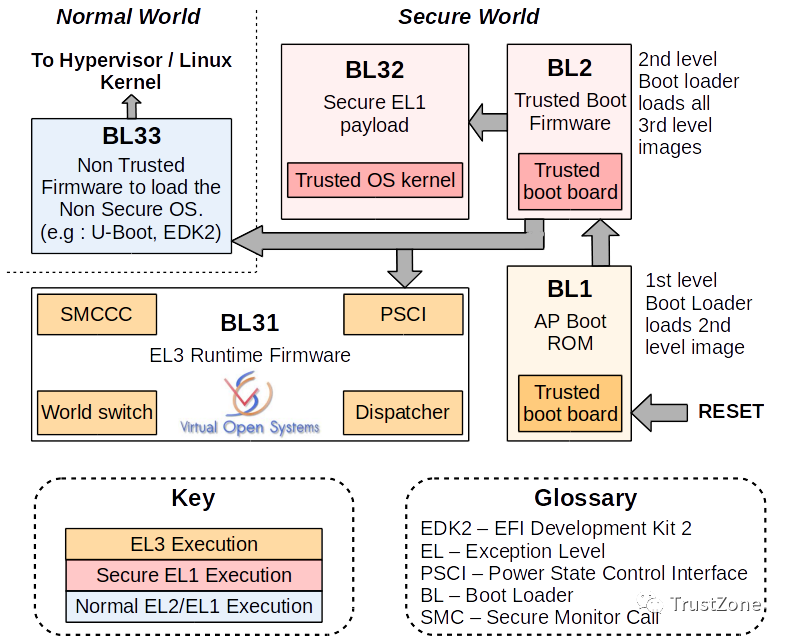

1744 TF-A 一开始是为 ARMv8 准备的,ARMv8 最突出的特点就是支持 64 位指令,但是为了兼容原来的 ARMv7,ARMv8提供了两种指令集:AAarch64 和 AArch32,根据字面

2023-09-11 16:31:00 422

422

ARMv8 工作模式 ARMv8 没有 Privilege level 的概念,取而代之的是 Exception level(异常级别),简称为EL,用于描述特权级别,一共有 4 个级别:EL0

2023-09-11 16:34:29 634

634

LRU(Least Recently Used)算法:该算法会跟踪每个cache line的age(年龄)情况,并在需要时替换掉近期最少使用的cache line。

2023-10-08 11:10:05 433

433 cache,那么在配制系统时可以作为独立的cache使用了。 使用独立的数据cache和指令cache,可以在同一个时钟周期中读取指令和

2023-10-31 11:26:31 371

371

Cache和存储器一样具有两种基本操作,即读操作和写操作。当CPU发出读操作命令时,根据它产生的主存地址分为两种情形:一种是需要的数据已在Cache中,那么只需要直接访问Cache,从对应单元中读取信息

2023-10-31 11:48:08 560

560 先看arm官网提供的一张图: 上图详细概括了arm官方推荐的armv8的启动层次结构: 官方将启动分为了BL1,BL2,BL31,BL32,BL33阶段,根据顺序,芯片启动后首先执行BL1阶段代码

2023-12-07 11:09:10 339

339

u-boot armv8链接脚本 在进行源码分析之前,首先看看u-boot的链接脚本,通过链接脚本可以从整体了解一个u-boot的组成,并且可以在启动分析中知道某些逻辑是在完成什么工作

2023-12-07 11:19:22 213

213

正在加载...

电子发烧友App

电子发烧友App

评论