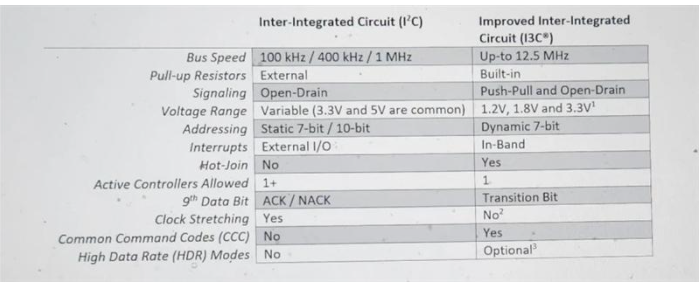

I3C 是一种用于嵌入式系统的新型串行通信协议,可提供比 I 2 C高得多的数据吞吐量和更多功能。借助 I3C,工程师和设计人员可以提高其设计的性能,同时还可以添加热连接等新功能,在带中断 (IBI) 和高数据速率 (HDR) 模式。此外,I3C 向后兼容并且可以与传统 I 2 C 目标进行通信。表 1总结了 I3C 和 I 2 C之间的差异。

表 1上述数据展示了 I3C 如何提供比 I 2 C 高得多的数据吞吐量和更的功能。资料

笔记:

标称值。不允许使用其他值。

时钟延展可由活动控制器(而非目标)执行,但对时序和总线状态有限制。

基本 I3C 通信不需要 HDR。即使连接了不支持的设备,I3C 总线也支持 HDR 通信。有关详细信息,请参阅高数据速率 (HDR) 模式。

总线速度

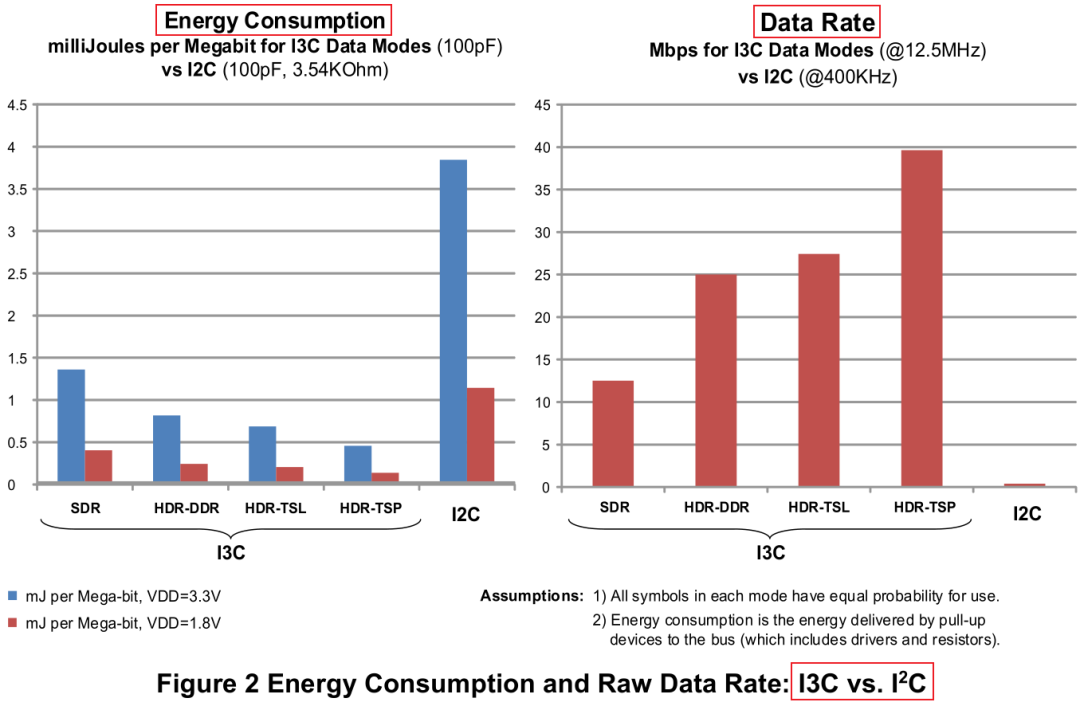

I 2 C 和 I3C之间显着的变化是时钟速度。I 2 C 通常为 100 kHz、400 kHz 或 1 MHz,而 I3C 可以达到高达 12.5 MHz 的速度。这种增长的主要因素之一是在 I3C 中使用推挽输出。I3C 根据总线状态在漏极开路和推挽驱动器之间切换。开漏在初始寻址或仲裁期间使用,其中多个目标可能同时控制线路。相比之下,当通信是单向的时使用推拉,并且没有其他设备同时通信的机会。

电气特性

与 I 2 C 不同,I3C 不需要外部上拉电阻,因为总线上的主控制器提供这些功能。I 2 C 具有很宽的工作范围,常见的是 3.3 V 和 5 V。I3C 具有三个标称电平:1.2 V、1.8 V 和 3.3 V。但是,允许使用其他工作范围。

设备寻址

I 2 C 支持目标设备的 7 位和 10 位寻址。使用 I3C,仅支持 7 位寻址。但是,I3C 使用动态寻址,主动控制器为每个目标分配一个地址以防止地址冲突。这与 I 2 C 形成对比,在 I 2 C 中,开发人员必须跟踪当前使用的地址以防止两个设备共享同一地址。目标的动态寻址发生在总线初始化期间。

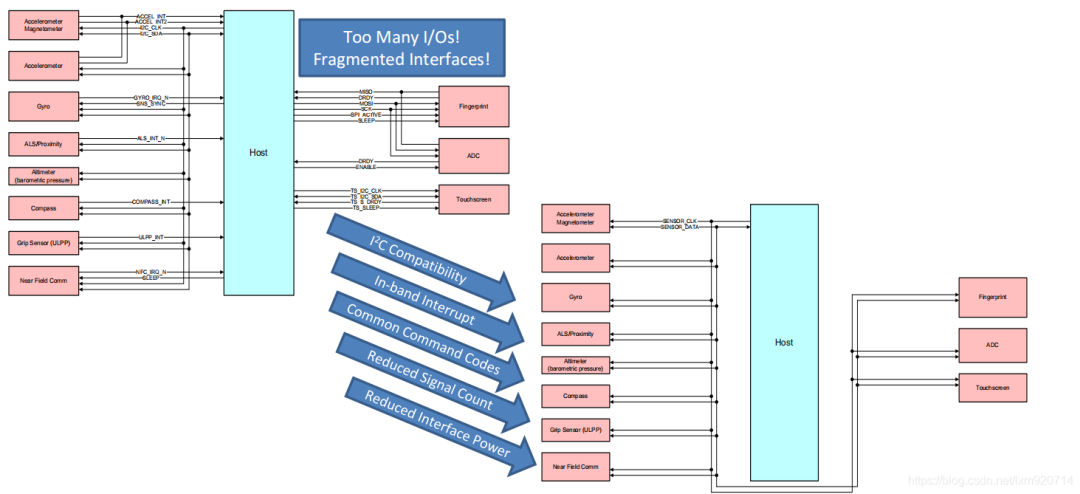

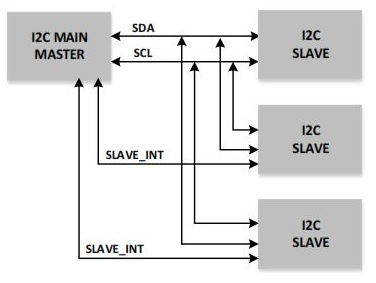

带内中断和热连接

在 I 2 C 中,没有一种机制可以让目标在不使用额外 I/O 线的情况下向控制器指示数据已准备就绪。但在 I3C 中,目标设备可以使用串行数据 (SDA) 和串行时钟 (SCL) 线发出中断信号,从而使其成为真正的双线协议。同样,这种带内信令也用于在 I3C 中实现热加入功能,因此设备可以在初始地址分配后加入。带内中断 (IBI) 和地址仲裁部分将对此进行更详细的讨论。

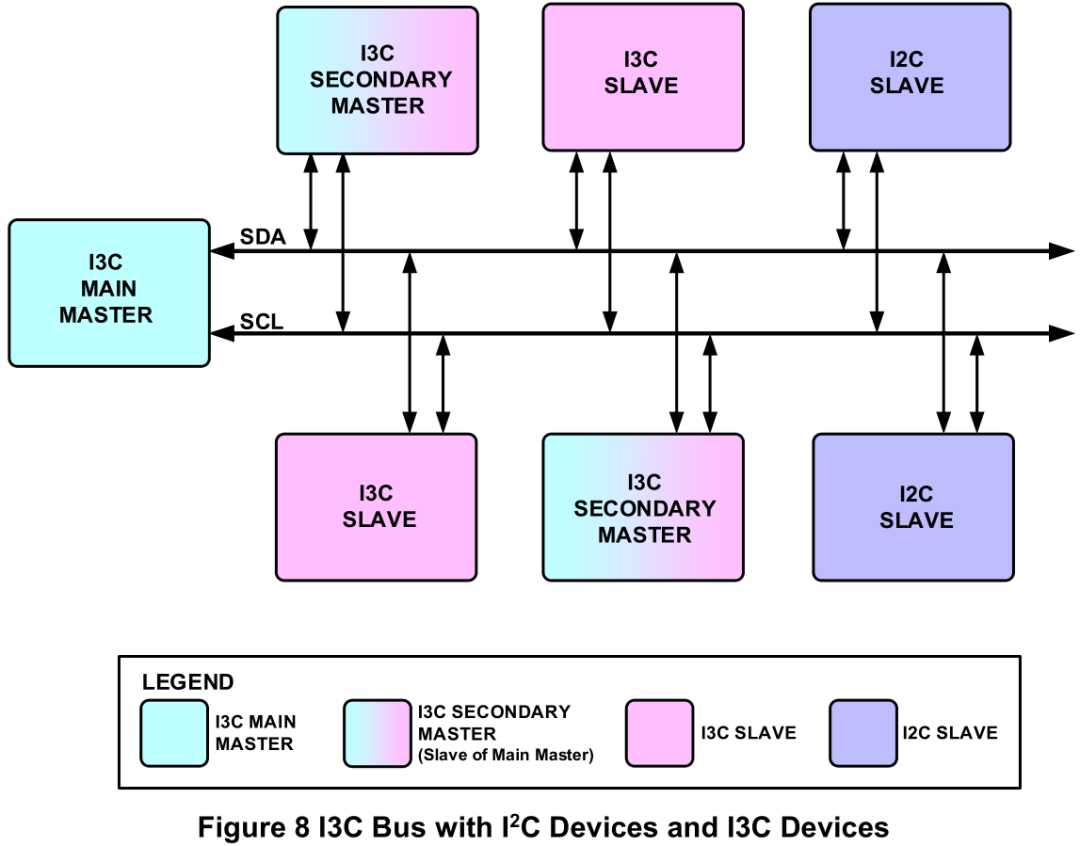

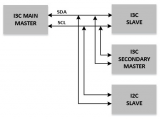

主动和辅助控制器

I 2 C 支持多控制器总线,其中多个设备作为控制器运行,但只有一个主动通信。但是,在 I3C 中,只有一个设备可以成为主动控制器;其他有能力的设备可能会请求成为总线上的活动控制器。这种设备称为辅助控制器。当辅助控制器不充当主动控制器时,它充当 I3C 目标。

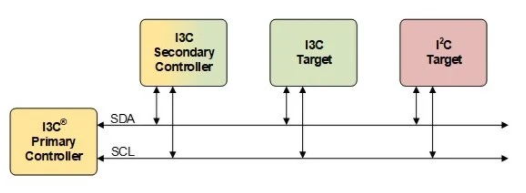

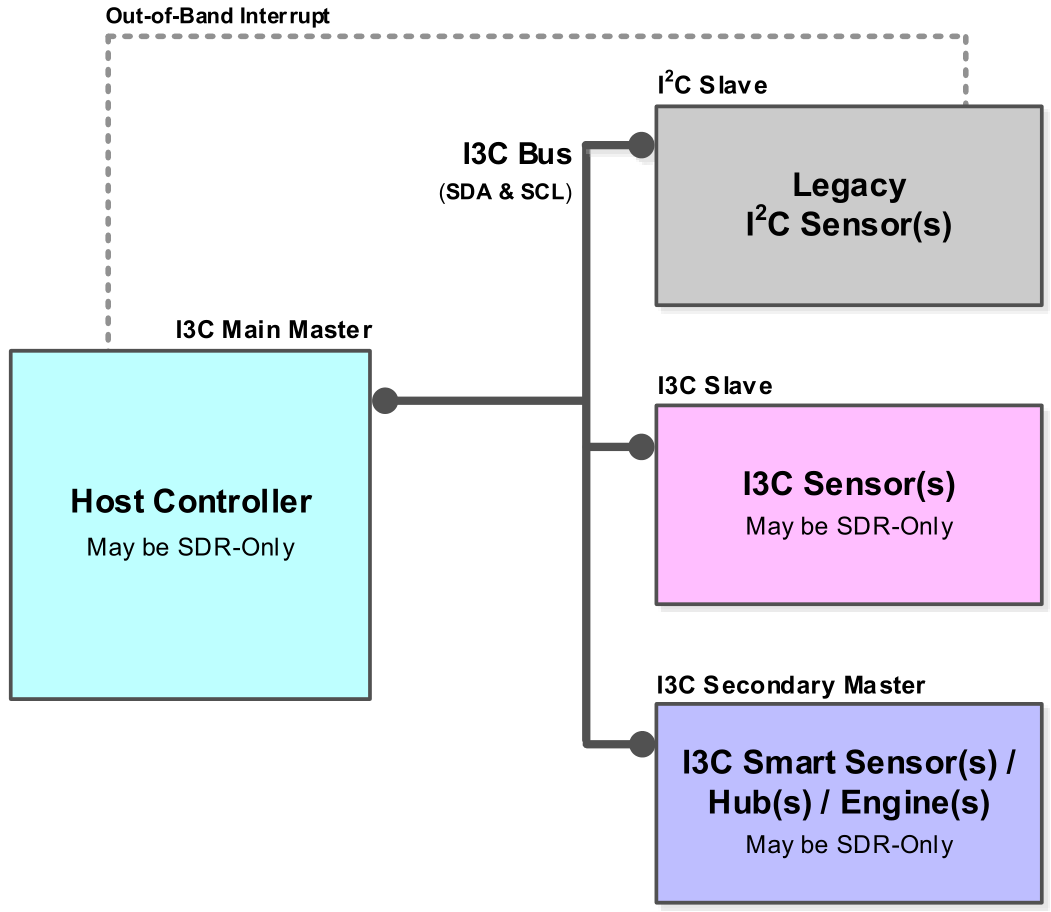

我2 C 支持

I3C 支持与 I 2 C 目标设备的通信。为了能够进行通信,I 2 C 目标必须:

有一个7位地址

不延长时钟

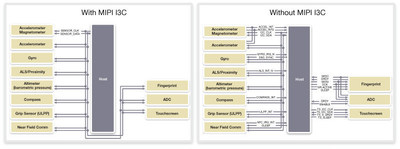

还强烈建议 I 2 C 目标在其输入端包含 50-ns 滤波器。如果满足这些要求,则 I 2 C 目标与 I3C 总线兼容。此外,一些 I3C 设备可以作为 I 2 C 目标运行,直到分配了一个动态地址。在 I 2 C 模式下,I3C 设备有一个用于通信的静态地址。该静态地址不一定与动态地址相同,但如果需要,可以分配相同的地址。I3C 总线的示例如下所示。

图 1该图突出显示了 I3C 总线。资料

I3C通信基础

在 I3C 总线上开始任何通信之前,必须配置总线,并且必须将动态地址分配给目标。

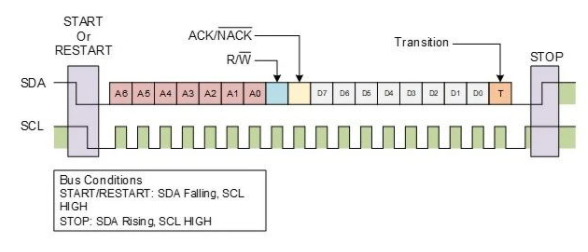

然后,像 I 2 C 一样开始通信。生成 START 条件,然后发送 7 位动态地址,R/nW 位后跟来自目标的 ACK 或 NACK。接下来,I3C 和 I 2 C一样使用 9 位串行传输,但是第 9位的功能位已从 ACK/NACK 更改为转换位或 T 位。T位有两个功能;当控制器写入目标时,T 位是发送数据字节的奇校验位。当控制器从目标读取时,T 位用作数据结束标志。此标志可以由控制器断言,以表示它已完成读取数据,或由目标来断言,以表示它没有更多数据可返回。为完成数据传输,控制器在总线上生成停止或重启条件。请注意,如果使用 RESTART,则报头将以推挽方式传输,因为没有仲裁。

图 2显示了 I3C 中数据传输的简化图,其中包含 1 个数据字节。资料

I3C 的一个重要变化是没有时钟延展。I 2 C 使用时钟延展给目标设备更多的时间来处理返回数据之前。使用 I3C,时钟仅由活动控制器驱动——在单数据速率 (SDR) 模式下。因此,时钟延展只能由控制器在有限的情况下执行。

然而,目标设备可以在总线初始化过程中指示速度限制,以指示工作频率、读写周转时间和其他时序参数。

通用命令代码 (CCC)

通用命令代码 (CCC) 是 I3C 中的一个新概念。主动控制器使用 CCC 来初始化和/或配置 I3C 总线。CCC 可以广播给每个目标,也可以私下针对特定目标。要发送 CCC,首先发送地址 7‘h7E/W。所有 I3C 设备都必须确认并侦听此地址。I 2 C 设备无法匹配此地址,因为根据 I 2 C 规范保留 7’h7E 。接下来,发送 CCC 代码。对于将数据写入目标的 CCC,继续发送数据直到完成。对于读取值的 CCC,发送任何参数(根据需要),重新启动总线,然后开始读取数据。

有太多的 CCC 需要讨论,但这里有一些重要的选择:

输入动态地址分配 (ENTDAA)

Enter Dynamic Address Assignment 通知所有目标,活动控制器正在分配动态地址。如果一个目标已经被分配了一个地址,它将 NACK 这个命令。

设置新的动态地址分配 (SETNEWDA)

Set New Dynamic Address Assignment 用于更改设备的动态地址。

启用事件 (ENEC)/禁用事件 (DISEC)

启用或禁用事件命令指示总线上当前是否允许热加入或带内中断等事件。

重置动态地址分配 (RSTDAA)

Reset Dynamic Address 清除当前分配的地址但不重新分配地址。在 I3C 规范的 v1.1 中,重置动态地址分配的直接形式已被弃用。

设置读取长度 (SETMRL)/获取读取长度 (GETMRL)

设置或获取读取长度指定可以读取的字节数。

设置写入长度 (SETMWL)/获取写入长度 (GETMWL)

设置或获取写入长度设置可以读取或写入的字节数。

设备特性寄存器或 DCR 是指定目标设备类型的寄存器。这方面的一个例子是代码 0xC6,微控制器的代码。I3C 规范定义了 DCR 值。MIPI 联盟提供了这些代码的列表。

获取总线特性寄存器 (GETBCR)

总线特性寄存器或 BCR 是定义目标上存在哪些 I3C 功能的寄存器。该寄存器还用于确定目标是否需要速度限制。

目标休息动作 (RSTACT)

CCC 中的目标重置操作定义了当检测到带内重置模式时目标会发生什么。为产生复位,SDA 保持低电平,同时 SCL 计时 14 次,然后是重启,然后是停止。目标检测带内重置模式并根据分配给它们的内容进行操作。此 CCC 不会触发重置,但会分配目标行为。如果未按照此命令复位,则下一个启动条件将清除分配的操作。

进入高数据速率模式 (ENTHDRx)

,还有高数据速率,或 HDR,Entry CCC。此 CCC 表示活动控制器正在进入四种 HDR 模式(0、1、2 或 3)之一。

高数据速率 (HDR) 模式

I3C 规范目前定义了四种 HDR 模式。

HDR 双倍数据速率 (HDR-DDR) [模式 0]

HDR 三元符号纯总线 (HDR-TSP) [模式 1]

HDR 三元符号传统包含总线 (HDR-TSL) [模式 2]

HDR 批量传输 (HDR-BT) [模式 3]

在 HDR 中,时钟速率不会改变数据编码方式的变化。I3C 基本通信不需要 HDR。不支持 HDR 的设备会忽略通信,直到它们检测到 HDR 退出模式。

硬盘驱动器

HDR-DDR 是一种使用时钟的两个边沿来传输数据的模式。这显着增加了总线的数据速率(但由于协议中的额外开销而不会加倍)。

HDR-TSP 和 HDR-TSL

在 HDR-TSP 和 HDR-TSL 中,数据以三进制传输,三个定义的符号从 SDA 和 SCL 线创建。根据规范,符号的电气定义如下:

只有 SCL 变化

只有 SDA 变化

SCL 和 SDA 都改变

HDR-TSP 和 TDR-TSL 之间的选择基于是否存在I 2 C 目标。HDR-TSP 只能在存在 I3C 目标时使用,而 HDR-TSL 则在存在传统 I 2 C 目标时使用。

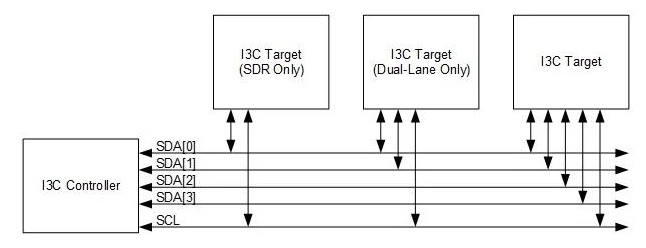

高动态范围蓝牙

HDR-BT 允许同时使用多个数据通道以实现更高的并行性。为了兼容性,只有 SDA 线的有效位或 LSB 用于单数据速率 (SDR) 通信。HDR-BT 支持双线和四线配置。图 3显示了一个示例配置。

图 3该图提供了支持 HDR-BT 的混合 I3C 总线示例。资料

带内中断 (IBI) 和地址仲裁

与 I 2 C 不同,目标可以在总线空闲(或空闲)时为 IBI 生成启动条件。如果在一定时间内没有交易发生,就会发生这种情况。当活动控制器检测到来自目标的启动条件时,它提供时钟信号以完成事务。如果两个目标试图同时通信,寻址仲裁就会发生。

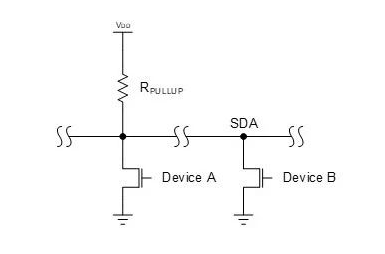

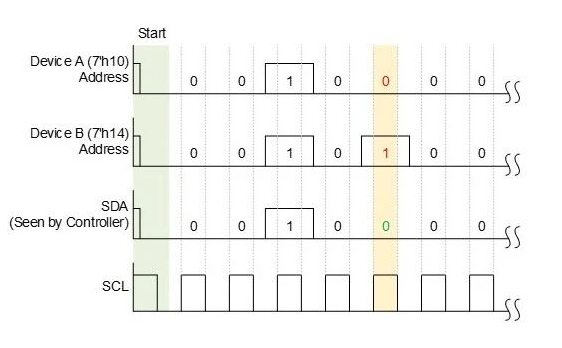

仲裁是确定允许哪个设备与控制器通信的过程。例如,假设两个设备 A 和 B 想同时与活动控制器通信。设备 A 的地址为 7‘h10,而设备 B 的地址为 7’h14。当带内中断产生时,两个设备都会尝试将它们的地址传输到活动控制器。在这种总线状态下,数据线是漏极开路的。在开漏通信期间,线路通过上拉电阻被动返回“1”,并可以主动断言为“0”。这可以防止同时传输 1 和 0 的两个设备发生短路。

图 4 SDA 线的简化视图显示了上拉电阻是如何内置在主控制器中的。资料

仲裁中的获胜地址是控制器收到的地址。跟随图5,首先,从每个设备地址发送两个零。接下来,两者都将释放其地址中“1”的数据线。然后,另一个 0 将由双方传输。此时,两个设备都没有赢得仲裁,因为此时接收到的地址与两者匹配。但是,对于下一位,其中一个目标将释放数据线以发送“1”,而另一个目标将尝试发送“0”。

图 5该示例显示地址为 7‘h10 和 7’h14 的 I3C 仲裁。资料

“1”的发送器将失去仲裁,因为“1”由开漏配置被动驱动,而另一个目标主动断言“0”。完成剩余的传输序列后,您可以看到控制器接收到地址 7‘h10,而不是 7’h14。因此,设备 B 仲裁失败并停止通信。在 I3C 仲裁中,高地址设备总是输给低地址设备。

I3C:一系列新功能

I3C 带来了串行总线带宽的显着增加,以及一系列新功能。本文触及了总线的特性和功能,但它并不是可能的特性和命令的详尽列表。MIPI 联盟提供了有关I3C 规范的更多详细信息。

电子发烧友App

电子发烧友App

评论