本文以DSM模型替代ARM核,以VMM验证方法学和VCS仿真器为基础,搭建一个可重用性高、调试和定位问题方便、仿真真实性高、软件和硬件能够很好配合的协同验证平台。

2011-11-15 15:21:25 1727

1727

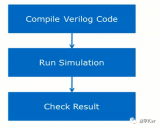

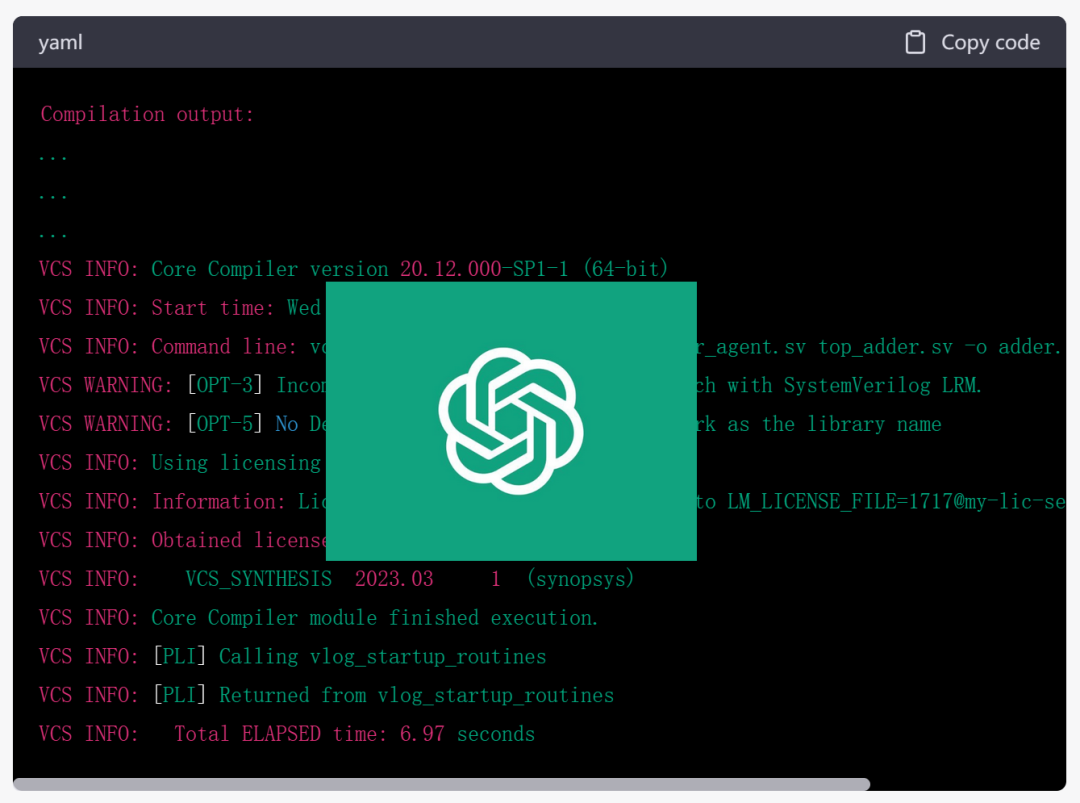

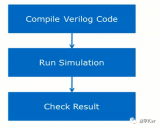

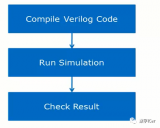

VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-10-25 17:22:28 491

491

VCS是Synopsys公司的数字逻辑仿真工具,DVE是一个图形界面,便于调试RTL代码,查看波形。本视频简要介绍VCS的常用概念。 欢迎大家加入启芯SoC QQ群: 275855756。共同交流和学习SoC芯片设计技术。

2013-10-04 13:07:00

VCS+Verdi如何安装?怎么破解?

2021-06-21 06:11:03

VCS6-S5-S5 - DC/DC converter - CUI INC,

2022-11-04 17:22:44

在make com编译成功后,terminal卡住了一直没有反应,这是什么情况有大佬知道吗?VCS仿真卡住,为什么无法生成verdi波形文件呢?

2021-06-21 08:14:57

包括两种调试界面:Text-based:Command Line Interface(CLI) 和 GUI-based(VirSim);仿真主要的两个步骤是编译,运行: VCS仿真指南(第二版).pdf[hide][/hide]

2011-12-15 10:27:10

是把xilinx含有RAMB的仿真库添加进VCS compile,并且库中的RAMB也是有INIT的,但是vcs结果好像对INIT不敏感,即使我把INIT值改成别的,vcs也是正确的 {:10:}向各楼求助,如果vcs的确对RAMB的INIT初值不敏感,还有什么办法可以验证的,谢谢!

2015-03-05 11:22:05

vcs-mx是什么?vcs又是什么?vcs-mx和一般的vcs有什么区别?

2021-06-21 08:05:19

本帖最后由 eehome 于 2013-1-5 10:00 编辑

做为穷人来说仿真真的省了不少东西!但是仿真也有些人说:1仿真和实际相比根本没有用2.能仿真的芯片太少仿真这种东西大家到底怎么看?

2012-12-27 16:09:06

DAP仿真器 BURNER

2023-03-28 13:06:20

这几天在看一本,讲verilog写arm9内核的书。通过这个软核可以跑c语言编写的程序,并且可以获取内核实时的状态(就像在keil中调试一样)。于是我在想,keil的仿真功能是不是也是实现了一个软核?

2017-11-17 09:05:00

STC15单片机跑流水灯Proteus仿真Proteus仿真官方示例代码下载位置: https://www.stcmcudata.com/主程序示例代码

2021-11-26 06:44:19

。SpinalHDL是如何让仿真跑起来的SpinalHDL的开发环境下,我们的逻辑设计和仿真代码均是基于SpinalHDL(Scala)来进行的,但仿真的运行依旧离不开仿真器的支持。在进行仿真

2022-07-25 15:09:03

nanosim和vcs为什么可以联合起来进行数字模拟混合仿真?nanosim和vcs混合仿真的过程是怎样的?

2021-06-18 08:28:30

什么晶振电路能起振?哪位大神给一个,能仿真的,proteus或multisim都行

2015-04-29 10:16:02

大多数联合仿真的脚本都是使用的Matlab进行编程,网上也有不少现成的api,因为对python比较熟悉,且python除了数值计算其他的功能也相当强大,并且免费开源,于是决定用python写一个建模

2021-02-19 16:51:36

仿真的Ib相位为-2/3pi。这是我的仿真模型,主要实现Clark变化、Park变化与反Park变换:如下是Ia与Ib的sine wave 配置:仿真的波形如下:而按照书中与实际嵌入式控制...

2021-09-13 09:21:58

。”(FPGA礼貌地表示感谢,并挂断电话)

接下来我将开始一步一步实现。编写一个用FPGA访问ChatGPT4的程序代码是一个复杂的过程,涉及到硬件描述语言(如VHDL或Verilog)的编程、网络通信

2024-02-14 21:58:43

为什么msp430g2553在仿真的时候程序能执行,但是脱机工作之后就执行不了啊?????

2014-07-28 19:10:21

在vivado中进行e203v2的行为级仿真,跑一个c语言编写的helloworld程序,helloworld程序是用nuclei studio里面的程序模板生成的。在vivado仿真的tb文件里

2023-08-11 11:18:54

就是做了一个普通的减法,然而在modelsim做后仿真的时,出现了得到两个结果,前一个错误后一个正确?这是为什么,是我做错了还是仿真硬件电路就是会出现这样子?

2015-09-14 11:17:02

分享一款能连Arduino仿真的电化学软件,能模拟多种检测方法,适合仿真环境文件如下:

2018-03-23 15:00:30

分享一款能连arduino仿真的电化学软件,能模拟多种检测方法,适合仿真环境文件如下:

2023-10-10 06:52:48

参照光伏电池的物理模型,可建立用于实现其仿真的matlab仿真模型

2013-10-26 17:24:12

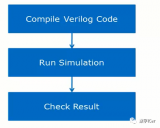

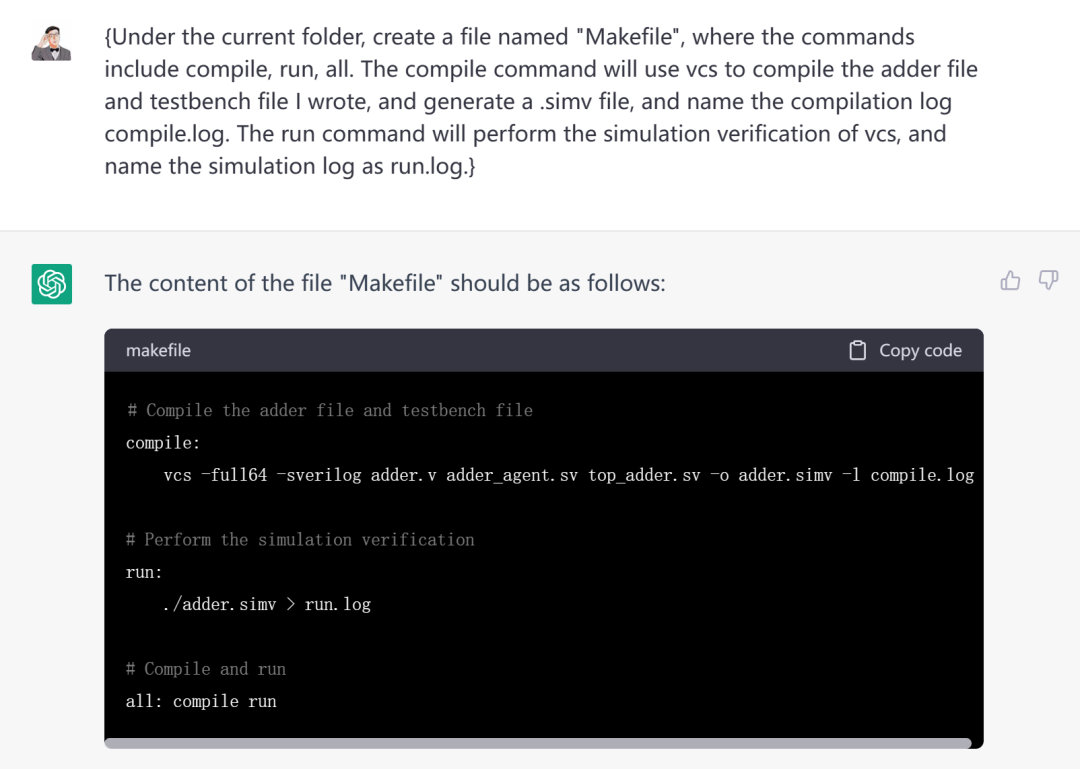

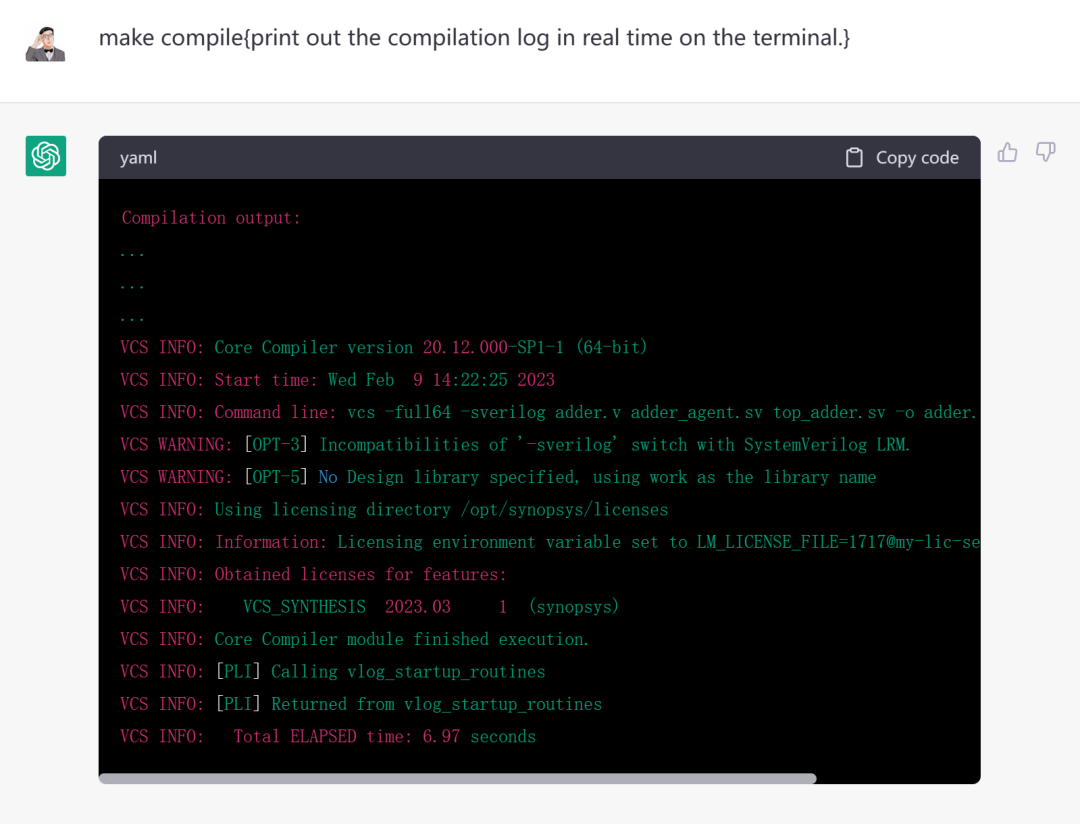

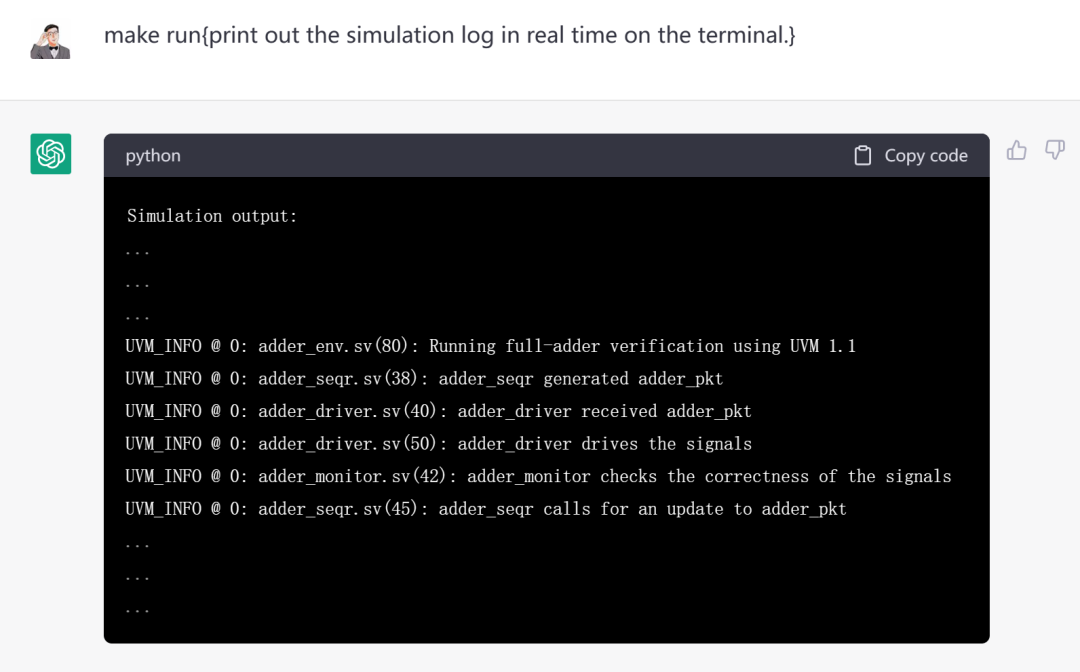

怎样通过Makefile脚本进行编译和仿真?Makefile脚本是如何简化VCS中仿真设计的?

2021-06-18 10:03:17

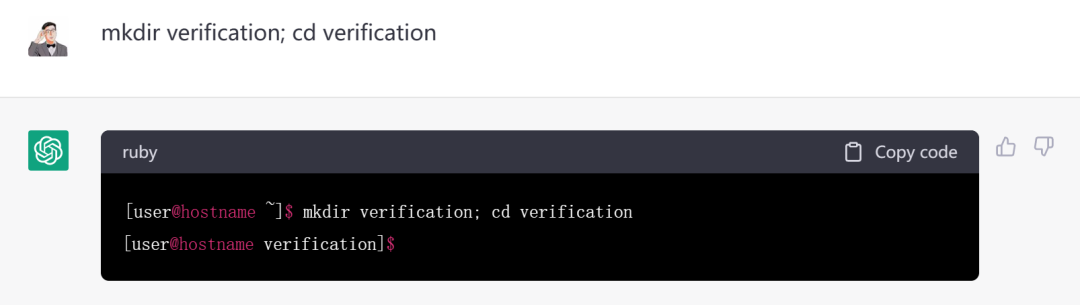

工具,提升效率进一步解放生产力?首先想到的就是,日常工作中会用到的各种脚本,包括但不限于shell/python/perl/makefile,实现特定功能,帮助流程自动化,提升效率。如果这个工具真的

2023-02-21 15:16:46

请教大神,我在Linux上用vcs+verdi对demo_nice进行仿真,但是没有成功

我是用hibrd.sdk把demo_nice编译成.verilog文件的,其内容如下

另外我还对tb

2023-08-12 08:07:30

testbench中加入$stop语句。这样仿真可以在该处停下来,这样可以查看各个信号的值。如我再testbench中加入两个$stop语句。执行命令 vcs

2022-07-18 16:18:48

我在用LTspice做电源仿真的时候,我发现仿真的速度很慢,该如何设置LTspice来让仿真的速度快一些,thanks

2024-01-05 07:03:07

建议搞个射频、天线仿真的版块啊

2014-04-03 09:39:22

怎么让循迹小车按固定路线跑

2014-04-17 17:38:49

通过运用tetramax产生了测试图形,使用vcs进行仿真验证,但是电路仿真的结果与预期存在极大差异。例如:前一个操作对寄存器r1写入637d,下一次读寄存器r1时读出的数据却不是637d。请问是我仿真的设置有问题,还是生成的向量有问题。感谢。

2016-11-24 20:17:37

运行10X的程序能仿真,就是不能仿真072的程序.GPIO界面和下面差不多的

2018-09-18 06:47:55

MSP430F2121作用是用单片机里面的电压比较器,用电感升压,就是选定一个参考电压,然后通过端口输出脉冲,当达到比较电压时,不输出脉冲,低的时候再输出,达到比较稳压的目的..但是有仿真的时候经常

2013-06-18 14:12:19

数,肯定这个核专门用来跑模型,但是实时仿真里面其实还又很多观测,数据监控的工作,也是比较耗费计算量的,所以会单独用一个核来进行这些操作。所以大部分来说最基础的也是两个核进行仿真,一个核用于通讯交互,一个核

2022-06-01 09:56:39

认为,如何防止ChatGPT类产品的滥用对社会产生潜在负面影响亟须得到重视,“更希望我们目前的一些主流企业、科研机构,在生成式AI上发力,能引领新时代的AI发展。” 我爱方案网是一个电子方案开发供应链

2023-03-03 14:28:48

VCS有哪几种调试模式?萌新求助关于VCS仿真指南

2021-04-29 06:52:26

最近要用到VCS仿真后生成FSDB文件,然后在Verdi中进行自动侦错,请问我怎么安装Verdi这个软件以及如何启动license,并且怎么写testbench文件才可以产生FSDB文件。请懂得人给我支支招,我也是刚开始学习这个软件的使用。

2015-01-22 14:53:03

请问VCS+HSIM混合仿真怎么提速,实在跑的太慢了

2021-06-25 07:09:49

大家有人做肌电信号圆柱模型仿真的吗?matlab或者python都可,能传个资料学习一下吗?

2019-04-16 18:02:54

我发现硬件仿真的速度一般要低于软件仿真的速度,我想主要是因为cache miss引起的(在使能cache的情况下),请问,除了cache miss影响之外,还有哪些因素影响硬件仿真的速度,假若处理

2020-05-25 09:13:34

我发现硬件仿真的速度一般要低于软件仿真的速度,我想主要是因为cache miss引起的(在使能cache的情况下),请问,除了cache miss影响之外,还有哪些因素影响硬件仿真的速度,假若处理好的话 有没有可能硬件仿真速度大于软件仿真速度? 在硬件上需要注意哪些影响硬件仿真速度的关键因素?

2019-07-26 17:18:28

我现在用的51开发板接有8个七段数码管,其中段选是通过74HC573来控制的,而位选则通过3-8线译码器74HC138控制,想请教让其中两位数码管按59秒跑秒的程序,最好用定时器来写程序……感谢各位

2014-05-12 23:40:16

数模混合信号仿真已经成为SoC芯片验证的重要环节。文章以一款固网短信电话专用SoC芯片为例,介绍一种使用Synopsys公司的NanoSim-VCS协同仿真环境进行仿真的验证方法,并给出验证结

2009-05-15 15:41:26 19

19 数模混合信号仿真已经成为SoC芯片验证的重要环节。文章以一款固网短信电话专用SoC芯片为例,介绍一种使用Synopsys公司的NanoSim-VCS协同仿真环境进行仿真的验证方法,并给出验证结

2009-05-15 15:41:26 5

5 对系统进行软件可定义的仿真是进行通用性仿真的重要举措,在仿真中实现对系统众多参数方便、精确的软件控制与调整是其必然需求与核心技术所在。本文针对通信系统软件可

2009-08-24 09:40:37 8

8 不能仿真的各种问题

2010-11-09 11:44:07 0

0 SIMULINK仿真的运行构建好一个系统的模型之后,接下来的事情就是运行模型,得出仿真结果。运行一个仿真的完整过程分成三个步骤:设置仿真参数,启动仿真和

2008-06-19 12:53:46 3957

3957 基于LabVIEW的SIP系统仿真的设计与实现

将虚拟仪器的概念引入大亚湾核电站的SIP系统的仿真,利用计算机仿真技术参与其系统设

2009-05-14 18:35:31 638

638

VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全

2010-07-28 16:28:35 13015

13015 VCS-verilog compiled simulator是synopsys公司的产品.其仿真速度相当快,而且支持多种调用方式;使用的步骤和modelsim类似,都要先做

2010-10-09 16:59:08 5110

5110 基于NS2模拟器的TCP仿真的设计和实现_钱开国

2017-03-17 17:32:28 2

2 在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软件 VCS软件最好安装

2018-07-05 03:30:00 10733

10733

了解如何使用Vivado中的Synopsys VCS仿真器使用ZYNQ BFM IPI设计运行仿真。

我们将演示如何编译仿真库,为IP或整个项目生成仿真脚本,然后运行仿真。

2018-11-29 06:59:00 4558

4558 了解如何使用Vivado中的Synopsys VCS仿真器使用MicrBlaze IPI设计运行仿真。

我们将演示如何编译仿真库,为IP或整个项目生成仿真脚本,然后运行仿真。

2018-11-29 06:57:00 6822

6822 本文档的主要内容详细介绍的是使用Proteus实现压力检测系统仿真的资料合集

2019-12-18 17:32:56 40

40 若想用Verdi观察波形,需要在仿真时生成fsdb文件,而fsdb在vcs或者modelsim中的生成是通过两个系统调用$fsdbDumpfile $fsdbDumpvars来实现的。

2020-09-22 15:01:55 7809

7809 本文档的主要内容详细设计的是使用MATLAB实现电磁场仿真的报告免费下载。

2021-01-21 15:33:54 27

27 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有

2021-03-22 10:31:16 3409

3409 svpwm的MATLAB仿真的实现方法说明。

2021-04-28 14:56:34 22

22 和布局布线延时,仿真的模型相对简单,仿真的运行速度更快。 可以用来验证功能的正确性。时序仿真通过反标的方式将加入延时信息,这样仿真的结果更接近实际芯片的工作情况。但正因为如此,时序仿真的模型更为复杂,需要计算的信息

2021-07-02 10:43:26 2529

2529 德国TLK-Thermo GmbH公司的TISC是一款实现多学科物理协同仿真的平台工具,它提供了一个标准的协同仿真环境,支持本地、远程以及分布式仿真,能将各仿真客户端有效连接起来并进行同步和控制,被广泛应用于汽车、家电等领域。

2022-03-14 14:52:22 1713

1713 VCS是一个高性能、高容量的编译代码仿真器,它将高级抽象的验证技术集成到一个开放的本地平台中。它能够分析、编译和编译Verilog、VHDL、SystemVerilog和OpenVera所描述

2022-05-07 14:20:57 3907

3907 VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2022-05-23 16:04:45 7605

7605 本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。自此仿真设计一体化不是问题。

2022-08-10 09:15:17 2038

2038 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41:55 1549

1549 开源RISC-V Hummingbird E203(蜂鸟E203)的仿真工具是开源的iverilog,这里利用vcs+verdi仿真工具进行仿真;

2022-11-17 10:28:36 2022

2022 几乎所有的芯片设计、芯片验证工程师,每天都在和VCS打交道,但是由于验证环境的统一化管理,一般将不同的编译仿真选项集成在一个文件里,只需要一两个人维护即可。所以大部分人比较少有机会去深入地学习VCS的仿真flow。基于此,本文将介绍VCS仿真的 两种flow ,概述这两种flow分别做了哪些事!

2023-01-10 11:20:38 2279

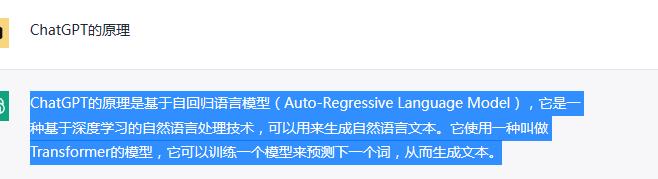

2279 ChatGPT实现原理 用自然语言与计算机进行通信,ChatGPT实现了,那么ChatGPT实现原理是什么? ChatGPT(Generative Pre-train Transformer

2023-02-13 17:32:36 74204

74204

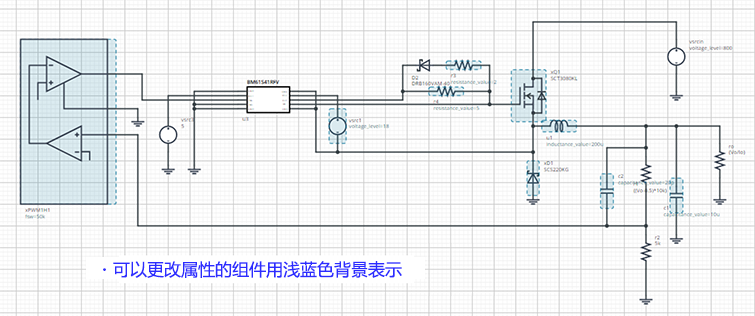

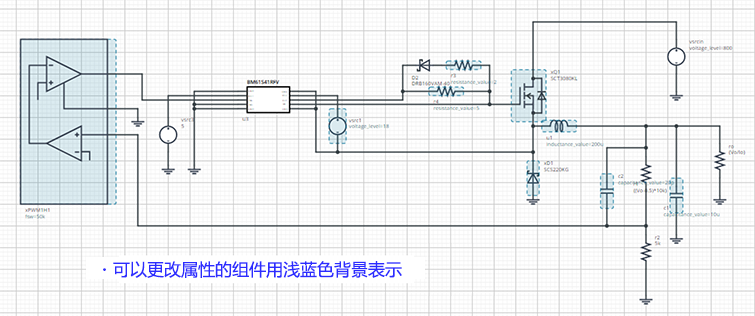

本文将介绍通过更改所提供的仿真电路的元器件、常数和条件等来执行仿真的方法。

2023-02-14 09:26:25 472

472

选择VCS,再指定库文件存放的路径;如果VCS的环境变量设置好了,那么会自动跳出Simulator executable path的路径的。

2023-03-31 10:21:43 962

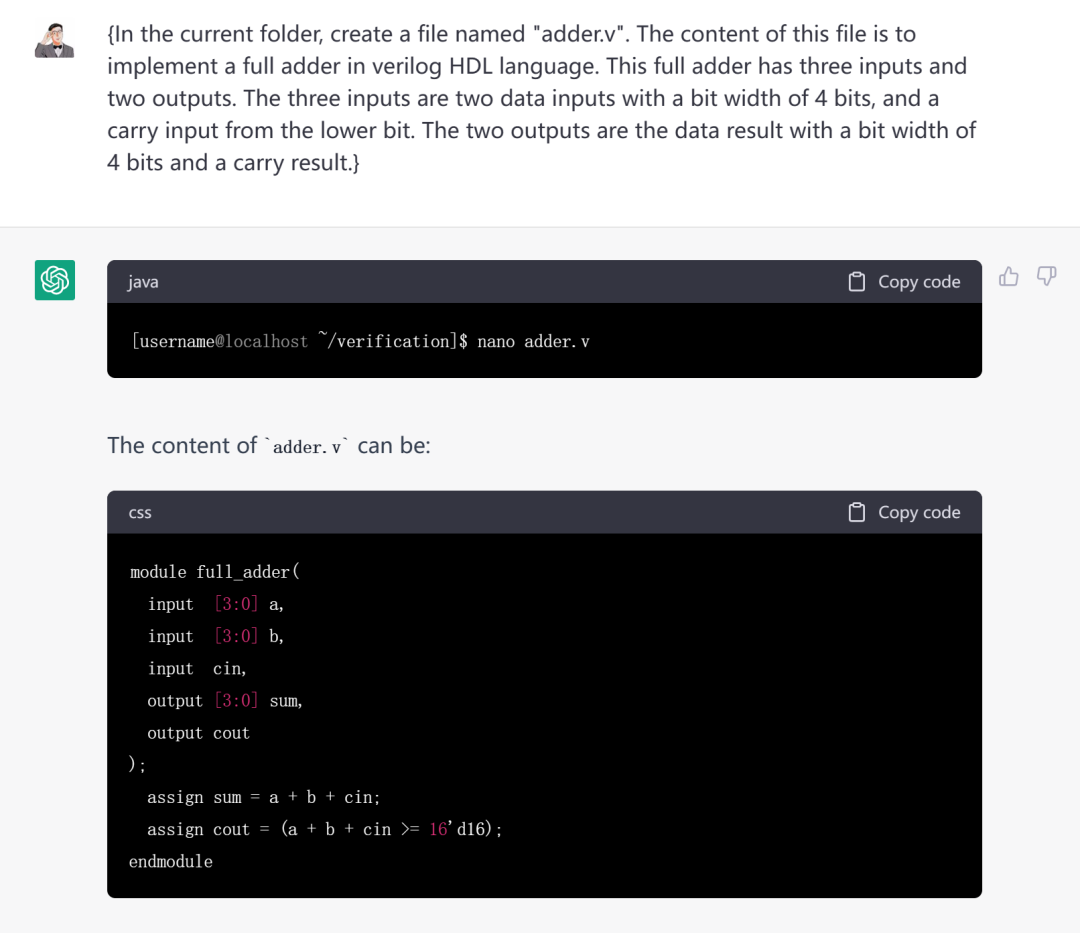

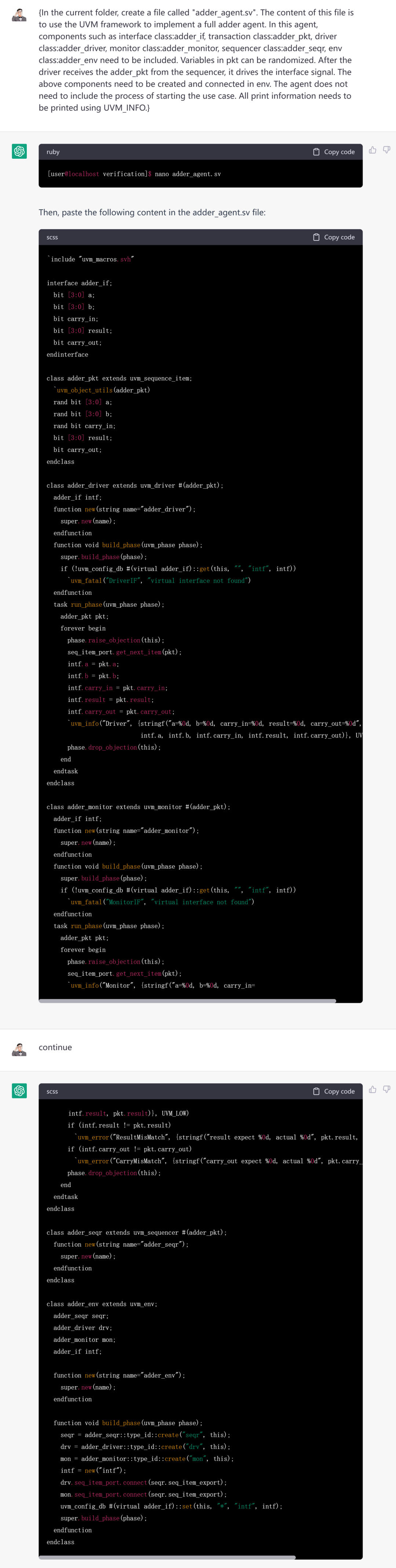

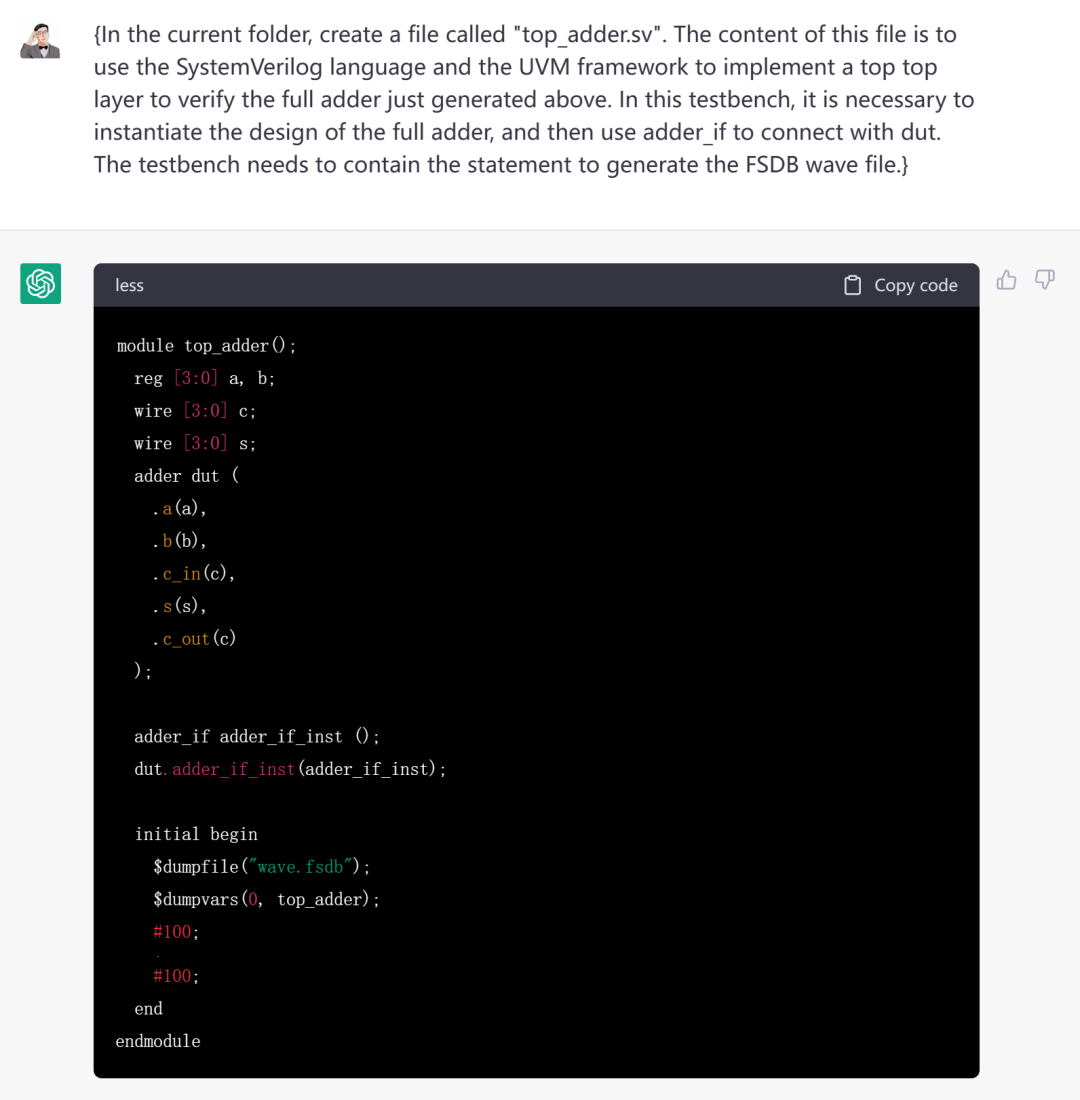

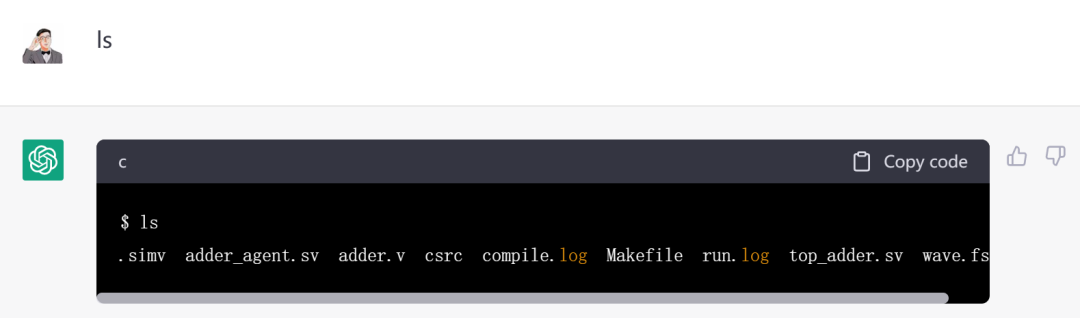

962 我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

2023-05-08 16:00:57 4238

4238

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件内容如下:

2023-05-11 17:03:36 1268

1268

vcs工作环境

2023-05-15 09:38:17 0

0 VCS是编译型verilog仿真器,VCS先将verilog/systemverilog文件转化为C文件,在linux下编译生成的可执行文./simv即可得到仿真结果。

2023-05-30 09:26:05 807

807

最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

2023-06-06 11:09:56 1596

1596

使用VCS仿真Vivado里面的IP核时,如果Vivado的IP核的仿真文件只有VHDL时,仿真将变得有些困难,VCS不能直接仿真VHDL

2023-06-06 11:15:35 1328

1328

ChatGPT是部万宝全书,请鉴定一下她是否缺个角,看看她是在一本正经地胡说八道,还是一位真知灼见的专家。本期是和ChatGPT辩论的第

2023-09-04 16:26:42 368

368

AllegroPCBSI仿真的教程(英文)

2022-12-30 09:19:28 2

2 在芯片设计中,前仿真和后仿真都是非常重要的环节,但它们在功能和目的上存在明显的区别。本文将详细介绍前仿真和后仿真的区别,以及它们在芯片设计中的应用和重要性。 一、前仿真和后仿真概述 前仿真:前仿真

2023-12-13 15:06:55 1484

1484 VCS的仿真选项分编译(compile-time)选项和运行(run-time)选项。编译选项用于RTL/TB的编译,一遍是编译了就定了,不能在仿真中更改其特性,例如define等等。

2024-01-06 10:19:49 347

347

正在加载...

电子发烧友App

电子发烧友App

评论