赋值何时使用阻塞赋值才能设计出符合要求的电路。 他们也不完全明白在电路结构的设计中,即可综合风格的Verilog模块的设计中,究竟为什么还要用非阻塞赋值,以及符合IEEE 标准的Verilog 仿真器究竟如何来处理非阻塞赋值的仿真。 本小节的目的是尽可能地把阻塞和非阻

2021-08-17 16:18:17 6000

6000 Verilog是一种硬件描述语言,用于描述数字电路的结构和行为。与传统的编程语言不同,Verilog更加注重电路的行为和时序特性。

2023-08-01 09:00:07 1722

1722

。由于他们的模拟、仿真器产品的广泛使用,Verilog HDL作为一种便于使用且实用的语言逐渐为众多设计者所接受 。在一次努力增加语言普及性的活动中,Verilog HDL语言于1990年被推向公众

2019-08-12 10:19:13

嵌入式开发Verilog教程(二)——Verilog HDL设计方法概述前言一、Verilog HDL语言简介1.1 Verilog HDL语言是什么1.2前言在数字逻辑设计领域,迫切需要一种共同

2021-11-08 09:30:31

Verilog HDL语言有什么优越性Verilog HDL语言在FPGA/CPLD开发中的应用

2021-04-23 07:02:03

:① 逻辑功能正确,②可快速仿真,③ 综合结果最优(如果是hardware model),④可读性较好。2. 范围本规范涉及Verilog HDL编码风格,编码中应注意的问题, Testbench的编码

2017-12-08 14:36:30

的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构

2020-11-30 19:03:38

Verilog HDL的基础教程.pdf 硬件描述语言 是硬件设计人员和电子设计自动化工具之间的界面其主要目的是用来编写设计文件建立电子系统行为级的仿真模型即利用

2008-05-20 13:07:14

Verilog可综合子集

2013-04-01 12:44:46

在看FPGA的资料,有一个关于Verilog语言的问题突然想不明白~{:16:}关于时序的,Verilog中,判断if成立的条件是当前值(感觉是电平式),还是过去值(感觉是时序)?例如:if(a==2) out

2013-03-25 21:31:58

Verilog阻塞和非阻塞原理分析在Verilog语言最难弄明白的结构中“非阻塞赋值”要算一个。甚至是一些很有经验的工程师也不完全明白“非阻塞赋值”在仿真器(符合IEEE标准的)里是怎样被设定执行

2009-11-23 12:02:57

求,verilog语言1,4,15 位二进制加减法器设计的代码急用,谢谢:)

2011-04-03 21:52:44

可综合模型的结构如果程序只用于仿真,那么几乎所有的语法和编程语句都可以使用。但如果程序是用于硬件实现,那么我们就必须保证程序的可综合性,即所编写的程序能被综合器转化为相应的电路结构。不可综合的HDL

2012-10-20 08:10:13

1,在一个verilog程序里,如果循环是一个循环次数不可定的循环,那么它能被综合工具综合吗2,如果程序里有always @(clock)里面又嵌套了@(clock)这样的控制事件,这个能被综合吗

2015-02-03 15:29:11

,若不是,则只能用于仿真),while, 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

,arrays,memories,repeat,task,while。建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使

2012-02-27 15:01:27

verilog的仿真和综合有什么区别,请具体一点?

2018-06-06 22:41:18

verilog设计练习进。我们可以先理解样板模块中每一条语句的作用,然后对样板模块进行综合前和综合后仿真,再独立完成每一阶段规定的练习。当十个阶段的练习做完后,便可以开始设计一些简单的逻辑电路和系统

2012-08-15 16:29:30

转换成HDL代码,跳过了中间的C语言改写步骤12.常规从算法到硬件电路的开发过程:算法的开发C语言的功能描述并行结构的C语言改写verilog的改写仿真、验证、修正综合、布局布线、投入实用13.C语言

2012-01-12 15:15:21

了中间的C语言改写步骤12.常规从算法到硬件电路的开发过程:算法的开发C语言的功能描述并行结构的C语言改写verilog的改写仿真、验证、修正综合、布局布线、投入实用13.C语言改写成verilog

2017-11-30 09:01:53

可综合的Verilog语法和语义(剑桥大学,影印)

2012-08-06 13:03:57

全球领先的设备软件优化(DSO)厂商风河系统公司(Wind River)宣布推出Wind River Workbench On-Chip Debugging 3.1.1,将这套综合性开发工具的支持

2019-08-28 08:14:28

apex20ke_atoms.v编译到其中。2:在图形界面中的Load Design对话框中装入仿真设计时,在Verilog 标签下指定预编译库的完整路径。(见下图)逻辑综合目前可用的FPGA综合工具

2020-05-15 07:00:00

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:17:54

总的来说,UFS3.0的综合性能,特别是持续读写速度有着秒杀UFS2.1前辈的表现,只是在随机读写和SQLite性能上,却依旧和双通道的UFS2.1持平,有些小遗憾。最后,咱们再来科普一下eMMC

2021-07-22 07:17:09

、固核与硬核:1.3Verilog HDL设计流程:注:Verilog HDL语法的两个部分第一章Verilog基础知识1.1Verilog HDL开发的优势:语法简单,可综合性与系统仿真性能强,支持

2022-03-22 10:26:00

:Verilog HDL程序设计语句和描述方式第四章:Verilog HDL数字逻辑电路设计方法第五章:仿真验证与Testbench编写第六章:Verilog HDL高级程序设计举例第七章:数字集成电路设计流程(测试仿真、综合)超级干货,精选内容不可错过!

2021-03-30 14:31:41

我们以Imagination新发布的两款内核产品为例,来分析不同应用市场对嵌入式AI的综合性能指标。

2021-01-14 06:53:15

肇庆学院光机电一体化综合性实验教学示范中心实验教材之二十六计算机控制技术实 验 教 程肇庆学院电子信息与机电工程学院编二00八年九月内容简介本书主要是基于清华大学出版社出版的由于海生先生所编著

2021-09-01 06:50:57

问题:用vhdl语言和Verilog语言和matlab协仿真同一个程序,在modelsim上跑出来的结果不一样。导致时序有问题。网上查了很多资料没有结果。(调用的.m函数一样即输入信号一样)。例子

2015-04-28 09:12:50

功能仿真:可以验证代码的逻辑性,不加任何的时延信息。仿真工具为modelsim(组合逻辑和时序逻辑都可以功能仿真),modelsim不能综合。在modelsim中添加相应的激励信号,调用

2016-08-23 16:57:06

数字集成电路设计入门--从HDL到版图于敦山北大微电子学系?介绍Verilog HDL,内容包括:–Verilog应用–Verilog语言的构成元素–结构级描述及仿真–行为级描述及仿真–延时的特点

2012-08-03 00:23:48

、可维护性,又可以提高仿真效率,且容易被重用。(绝大部分设计人员将这个阶段的仿真叫功能仿真!)二、综合后门级功能仿真 (前仿真) 一般在设计流程中的第二个仿真是综合后门级功能仿真。绝大多数的综合工具

2018-01-24 11:06:12

`该资料对STM32微控制器作了诠释和指导,STM32的基础实验,进阶应用,硬件描述和综合性实验的详细资料概述包括了实物图和原理图。`

2018-09-04 14:35:45

让大家能够搭建简单的 UT 单元测试环境。Verilog 也有适用于仿真的代码,这些代码是不可以综合的。可以使用Verilog 来搭建基本的单元测试环境。本问介绍了如何编写测试验证程序(test

2023-10-13 08:11:45

描述语言,它主要应用于数字电路和系统设计、数字电路和系统仿真等,即利用计算机和相关软件对VERILOG HDL等硬件语言建模的复杂数字电路设计进行仿真验证,再利用综合软件将设计的数字电路自动综合,以得到

2018-11-05 20:24:23

少部分才是用于电路设计,详细可以参考本书的“可综合逻辑设计”一节。Verilog中用于设计的语法,才是学习的重点。掌握好设计的语法,熟练应用于各种复杂的项目,这是技能的核心。其他测试用的语法,需要

2018-10-08 15:19:23

大神,求51单片机综合性编程题越多越好!

2013-11-04 16:24:05

语言标准的时候,并没有考虑这些代码如何用硬件来实现。换句话说,有些代码写起来简单,实现起来却可能非常复杂,或者几乎不可能实现。三、HDL代码的可综合性现在回到最初的问题上。为什么诸如除法、循环之类

2019-03-27 07:00:00

在本篇里,我们讨论 Verilog 语言的综合问题,Verilog HDL (Hardware Description Language) 中文名为硬件描述语言,而不是硬件设计语言。这个名称提醒我们

2021-07-29 07:42:25

粘土混砂机实验(综合性实验)一、实验内容学生自行用实验用混砂机所带配件组装成一种机型的混砂机,并调整到所选定的工作参数;确定型砂配方,在已

2009-05-14 23:49:33 0

0 实验 译码器及其应用(综合性设计性)

一、实验目的1. 掌握中规模集成译码器的逻辑功能2. 熟悉数码管的使用3. 能使用译码器进行综合性设计二、实验预习

2009-07-15 18:43:09 20

20 Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13 86

86 采用 Verilog HDL 语言在Altera 公司的FPGA 芯片上实现了RISC_CPU 的关键部件状态控制器的设计,以及在与其它各种数字逻辑设计方法的比较下,显示出使用Verilog HDL语言的优越性.关键词

2009-08-21 10:50:05 69

69 分析了模拟硬件描述语言 Verilog-A 的特点及模型结构,根据仿真速度和仿真精度的折衷考虑,设计实现了模拟开关、带隙基准电压源及运放的Verilog-A 行为模型。根据数模转换器

2009-11-21 15:37:55 30

30 LCCT-01A 鲁尔接头综合性能测试仪产品简介LCCT-01A 型鲁尔接头综合性能测试仪是根据“GB/T1962.1-2015(ISO594-1:19)(ISO80369)注射器、注射针

2023-11-23 12:40:54

此综合与仿真设计指南提供了使用硬件描述语言(HDL)设计FPGA。它包括为HDL设计新手提供设计提示,以及为第一次使用FPGA做设计的经验丰富的工程师。在使用综合和仿真设计指南前

2010-11-02 10:06:37 43

43 摘 要:通过设计实例详细介绍了用Verilog HDL语言开发FPGA/CPLD的方法,并通过与其他各种输入方式的比较,显示出使用Verilog HDL语言的优越性。

2009-06-20 11:51:28 1857

1857

基于Verilog的顺序状态逻辑FSM的设计与仿真

硬件描述语言Verilog为数字系统设计人员提供了一种在广泛抽象层次上描述数字系统的方式,同时,为计算机辅助设计工具

2010-02-04 09:32:41 1665

1665

Verilog HDL语言简介

1.什么是Verilog HDLVerilog HDL是硬件描述语言的一种,用于数

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL语言对比

Verilog HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。VHDL是在1987年成为IEEE标准,Verilog HDL

2010-02-09 09:01:17 10317

10317 有许多可综合状态机的Verilog代码描述风格,不同代码描述风格经综合后得到电路的物理实现在速度和面积上有很大差别。优秀的代码描述应当易于修改、易于编写和理解,有助于仿真和调

2011-12-24 00:52:00 30

30 可综合的Verilog语法和语义(剑桥大学,影印):第七版

2012-05-21 14:50:14 27

27 verilog硬件描述语言课程讲义

2012-05-21 15:01:29 33

33 Verilog HDL 数字设计教程【作者:贺敬凯;出版社:西安电子科技大学出版社】(本资料为ppt) 内容简介:介绍了Verilog HDL语言,状态机设计,仿真,还有好几个可综合设计的举例,除了

2012-11-28 13:43:11 489

489 Verilog硬件描述语言参考手册,Verilog语法内容介绍

2015-11-12 17:20:37 0

0 基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计

2015-12-08 15:57:23 0

0 介绍Verilog HDL数字设计与综合的课件

2015-12-23 10:58:54 0

0 VHDL语言编程学习Verilog硬件描述语言

2016-09-01 15:27:27 0

0 ;第4章至第6章主要讨论如何合理地使用Verilog HDL语言描述高性能的可综合电路;第7章和第8章重点介绍了如何编写测试激励以及Verilog的仿真原理;第9章展望HDL语言的发展趋势。

2016-10-10 17:04:40 566

566 Verilog语言练习与讲解2,感兴趣的小伙伴们可以瞧一瞧。

2016-11-10 15:29:36 1

1 Verilog语言练习与讲解1,感兴趣的小伙伴们可以瞧一瞧。

2016-11-10 15:29:36 2

2 Verilog语言入门,感兴趣的小伙伴们可以瞧一瞧。

2016-11-10 15:29:36 5

5 新型离散小波系统的综合性能评价_许凤慧

2017-03-15 09:35:00 1

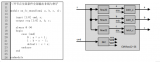

1 基于Verilog HDL语言的电路设计、仿真与综合 (一)顶层模块 本程序采用结构化设计方法,将其分为彼此独立又有一定联系的三个模块,如图1所示:

2017-11-28 14:36:03 16

16 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。而C语言是一门通用计算机编程语言,应用广泛。

2017-12-08 16:43:30 11804

11804 如何应用Verilog语言进行数字电路和系统的设计和验证,从基本概念讲起,井逐渐过渡到编程语言接口以及逻辑综合等高级主题。

2018-12-24 08:00:00 0

0 中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:12:00 3449

3449

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。

2019-09-27 07:09:00 1518

1518

Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需要在编译之前就确定,动态改变循环次数的语句是不可综合的。forever语句是不可综合的,主要用于产生各种仿真激励。

2019-10-13 12:23:00 18103

18103 Verilog HDL简称Verilog,它是使用最广泛的硬件描述语言。

2020-03-22 17:29:00 4355

4355 本文主要阐述了verilog中端口的三种类型及verilog语言入门教程。

2020-08-27 09:29:28 10284

10284 的是硬件描述语言。最为流行的硬件描述语言有两种Verilog HDL/VHDL,均为IEEE标准。Verilog HDL具有C语言基础就很容易上手,而VHDL语言则需要Ada编程基础。另外Verilog

2020-09-01 11:47:09 4002

4002

Verilog是一种流行的硬件描述语言,他是由工业界开发的,1984年,Verilog作为一种私用的硬件描述语言,由Gateway Design Automation公司给出,1988

2020-09-11 17:24:00 12

12 Verilog黄金参考指南是一个紧凑的快速参考指南Verilog硬件描述语言,其语法,语义,综合和应用程序的硬件设计。

2021-02-01 15:37:00 22

22 Verilog标准前,由于Cadence公司的 Verilog-XL 仿真器广泛使用,它所提供的Verilog LRM成了事实上的语言标准。许多第三方厂商的仿真器都努力向这一已成事实的标准靠拢。

2021-02-05 16:24:00 72

72 1、如何使用Verilog HDL描述可综合电路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL语言仅是对已知硬件电路的文本描述。所以编写前: 对所需实现的硬件

2021-04-04 11:19:00 3837

3837

简单介绍Verilog HDL语言和仿真工具。

2021-05-06 16:17:10 617

617 条件语句的可综合性 HDL语言的条件语句与算法语言的条件语句,最大的差异在于: 1.不管条件:当前输入条件没有对应的描述,则该条件为不管条件(Don’t Care)。对应不管条件的信号称为不管信号

2021-05-12 09:12:22 1558

1558

阻塞赋值和非阻塞赋值的可综合性 Blocking Assignment阻塞赋值和NonBlocking Assignment非阻塞赋值,原本是软件进程管理的术语。由于Verilog团队是从C语言发展

2021-05-12 09:45:09 2398

2398

VHDL与Verilog硬件描述语言在数字电路的设计中使用的非常普遍,无论是哪种语言,仿真都是必不可少的。而且随着设计复杂度的提高,仿真工具的重要性就越来越凸显出来。在一些

2021-08-04 14:16:44 3307

3307 知乎上刷到一个问题,问性能最强的编程语言是什么?看到高赞回答到是Verilog,然后在评论区就引发了一场Verilog到底算不算编程语言的争论,我觉得比较有意思,所以就也打算唠唠这个事情。 趁着最近

2021-08-23 14:30:49 5558

5558 综合性CPLD/FPGA软件Quartus 13.0下载

2021-09-12 09:35:13 17

17 Vivado 仿真器支持混合语言项目文件及混合语言仿真。这有助于您在 VHDL 设计中包含 Verilog 模块,反过来也是一样。 本文主要介绍使用 Vivado 仿真器进行混合语言仿真的一些要点

2021-10-28 16:24:49 2774

2774 要想深入理解Verilog就必须正视Verilog语言同时具备硬件特性和软件特性。

2022-07-07 09:54:48 1124

1124 综合工具读入源文件,通过综合算法将设计转化为网表,比如DC。能够综合的特性要求Verilog语言能够描述信号的各种状态(0,1,x,z)、信号和模块的连接(例化)以及模块的逻辑(赋值以及各种运算符)。

2022-07-07 09:53:52 727

727 Icarus Verilog(以下简称iverilog )号称“全球第四大”数字芯片仿真器,也是一个完全开源的仿真器。

2022-08-15 09:11:07 4821

4821 Verilog 是硬件描述语言,顾名思义,就是用代码的形式描述硬件的功能,最终在硬件电路上实现该功能。 在 Verilog 描述出硬件功能后需要使用综合器对 Verilog 代码进行解释并将代码

2023-03-21 10:31:40 663

663

要想深入理解Verilog就必须正视Verilog语言同时具备硬件特性和软件特性。在当下的教学过程中,教师和教材都过于强调Verilog语言的硬件特性和可综合特性。将Verilog语言的行为级语法

2023-05-25 15:10:21 642

642

要想深入理解Verilog就必须正视Verilog语言同时具备硬件特性和软件特性。在当下的教学过程中,教师和教材都过于强调Verilog语言的硬件特性和可综合特性。将Verilog语言的行为级语法

2023-05-25 15:10:44 576

576

建立用于RTL综合的Verilog标准化子集。他是贝尔实验室所开发的ArchSyn综合系统的主要设计者之一。他曾为AT&T和Lucent的许多设计师讲授Verilog HDL语言和Verilog HDL综合课程。

2023-05-26 16:59:30 934

934

Verilog 是一种用于数字逻辑电路设计的硬件描述语言,可以用来进行数字电路的仿真验证、时序分析、逻辑综合。

2023-06-10 10:04:44 786

786

近日,清华大学新闻与传播学院发布了《大语言模型综合性能评估报告》,该报告对目前市场上的7个大型语言模型进行了全面的综合评估。近年,大语言模型以其强大的自然语言处理能力,成为AI领域的一大热点。它们

2023-08-10 08:32:01 605

605

VHDL与Verilog硬件描述语言在数字电路的设计中使用的非常普遍,无论是哪种语言,仿真都是必不可少的。而且随着设计复杂度的提高,仿真工具的重要性就越来越凸显出来。在一些

2023-09-09 10:16:56 721

721

简要分享如何评估所选购焊锡膏综合性能的优劣?

2023-10-23 09:08:41 209

209 Verilog语言是一种硬件描述语言(HDL),用于描述数字逻辑电路和系统。它是一种非常强大且广泛使用的语言,在数字电路设计中扮演着重要的角色。其中, inout 是Verilog中的一种信号类型

2024-02-23 10:15:48 176

176

电子发烧友App

电子发烧友App

评论