在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 这篇文章是探讨对接收端进行时序优化(即ready打拍,或称backward打拍)的方式。

2023-12-04 10:20:55 234

234

Virtex® Ultrascale™ FPGA 所需的所有电源轨设计已经过优化,支持 12V 输入板载加电和断电排序具有输出电压和电流报告功能的 PMBUS 接口电压裕量调节功能

2018-08-29 08:33:47

高速DAP仿真器 BURNER

2023-03-28 13:06:20

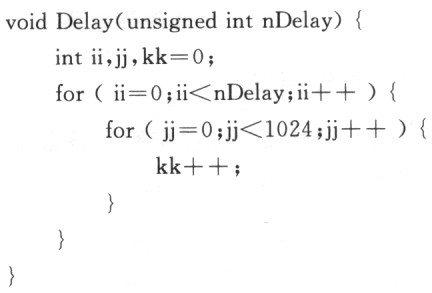

在TMS320LF2407串行接口中的信息传递的高速率。本设计综合考虑速度、工作电压、噪声容限等因素的影响.采用了一种新颖的触发器结构(图4A部分),本文接口电路中大都采用了该触发器的电路设计,工作电压降低到3.3V,大大

2019-06-18 05:00:11

下一代总线,在各自的瓶颈上,时序裕量非常小,设计极为困难。其二,由于技术的发展,大家更多的关注DDR3,关注高速串行总线,共同时钟系统的研究越来越少,相应的总结文章也不常见,就带来很多设计问题,也就

2014-10-21 09:35:50

SERDES结构是怎样构成的?高速SERDES接口在网络方面有哪些应用?

2021-04-28 07:19:38

和远端串扰这种方法来研究多线间串扰问题。利用Hyperlynx,主要分析串扰对高速信号传输模型的侵害作用并根据仿真结果,获得了最佳的解决办法,优化设计目标。【关键词】:信号完整性;;反射;;串扰;;近

2010-05-13 09:10:07

高速电路信号完整性分析与设计—时序计算引入:在数字电路中,从一个芯片发信息A到另一个芯片变成信息B,那么这个数字系统失败;如何保证信息不变?关键点,就是在传输过程的任意点都保持时序的正确性。时序概念

2009-09-12 10:28:42

高速电路的时序分析电路中,数据的传输一般都是在时钟对数据信号进行有序的收发控制下进行的。芯片只能按规定的时序发送和接收数据,过长的信号延迟或信号延时匹配不当都会影响芯片的建立和保持时间,导致芯片无法

2012-08-02 22:26:06

DDR布线在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的裕量。要保证系统的时序,线长又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号

2018-09-20 10:29:55

的保持时间Th 3. 时序裕量SlackSlack :约束文件要求时钟周期与实际布局布线后时钟周期的差值,表示时序裕量的一个称谓,大于零表示满足时序,小于零表示不满足时序1) Setup

2018-07-03 02:11:23

的保持时间Th 3. 时序裕量SlackSlack :约束文件要求时钟周期与实际布局布线后时钟周期的差值,表示时序裕量的一个称谓,大于零表示满足时序,小于零表示不满足时序1) Setup

2018-07-09 09:16:13

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

VGA驱动接口时序设计之7优化本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt最后,再次编译系统,查看时序

2015-08-10 15:03:08

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

EMC优化的高速CAN总线收发器

2023-03-24 15:06:28

容差,设计师可以优化功耗和输出噪声,为敏感型模拟电路打造出高效的低噪声电源。在裕量电压超低的条件下,输入和输出电压的最差条件容差可能对 PSRR 形成影响。在设计时充分考虑最差条件容差可以确保可靠

2018-10-23 17:07:54

最近使用MM32F5270开发板有用到带有SPI接口的液晶屏(驱动型号HX8257)显示一些调试信息,不过使用中发现一个奇怪的现象,MCU的SPI工作在高速下可以对液晶进行正常的控制,但当SPI时钟

2022-09-09 14:45:28

布线在设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,布线,线长匹配的基本原则是:地址,控制/命令信号与时钟

2018-09-20 10:59:44

InTime 利用大数据分析和人工智能,建立时序数据库,无需修改源代码即可优化设计,为工程师推荐最佳工具参数组合。了解更多>>

2017-04-18 14:53:40

Hi,用到TI的电源芯片TPS54329,原理图设计、环路测试结果如附件。 在测试环路稳定性时,将C20分别焊上22pF和68pF。测得结果22pF相位裕量不足,68pF相位裕量较好。但是参考其

2019-07-25 14:08:42

描述此参考设计可轻松实现支持电压裕量调节功能的 USB Type-C™ 电源的系统集成。TPS62136 降压转换器可高效地将电源从常用 9V、12V 或 15V 适配器转换为 USB Type-C

2018-10-26 10:38:28

能够有一些时序问题,我们再通过时序分析的方法对它进行优化。我们这里把原本的100M时钟改成了200M时钟,具体步骤如下: 一:更改时钟之后进行综合,并打开timing analysis 二:通过

2018-08-22 11:45:54

轮的运行后,即击中目标时序,TNS=0。 VXLAN_S57H项目相对需要优化的目标较为简单,容易满足。且工程量较小,整体综合编译布局布线周期较短,无法有力说明InTime带来的优化便利性。工程2工程2

2017-07-05 11:00:48

合成。正弦波的衰减将导致需要传输的信号产生边沿退化、幅度降低等问题,影响传输线的带宽。使用高速板材可以降低单位长度传输线的损耗。所以在线长相同的情况下,高速板材能使传输线带宽更高,信号裕量更大。同理

2019-06-27 18:38:26

在绘制电气CAD图纸的过程中,生成设备表是必不可少的。那么生成设备表的过程中需要统计线缆长度时考虑到实际工程的情况,此时便需要用到浩辰CAD电气软件中的线缆裕度功能了。那么什么是CAD线缆裕度?又如

2021-05-20 09:48:47

/高性能以及高速I/O(输入/输出接口)。伴随着FPGA特征尺寸的缩小,在40纳米/65纳米设计上遇到了与130纳米以前不一样的困难,其中主要包括功率管理和高速接口。 在功耗方面,随着产品逻辑密度和速率

2019-05-20 05:00:10

提出有效的PPA优化方案。其实这一条经验是并不特指高频设计,是做好设计的基本功,缺陷率高同学往往问题就出现在这里。2.建立把代码通过人脑转化成电路的能力。verilog描述的就是电路,时序优化也是在电路

2022-06-23 15:43:18

的工作时钟,通过调整sdram_clk的相位就能调整时序,从而满足建立时间和保持时间的要求。那么sdram_clk如何产生呢?可以通过PLL来产生,PLL可以保证频率相同、相位偏移量,所以该系统的结构

2016-09-13 21:58:50

最近用EPM1270T144C5N 做了一个可编程的延迟脉冲发生器,设计频率100M,在QUARTUS里编译完了之后软件给出时序警告,有些路径setup裕量不足,给出的Fmax仅为84.41M,但是烧到板子里用100M晶振还是可以正常工作,是不是timequest analyzer不靠谱啊。

2014-04-18 15:31:15

关于数Gpbs高速存储器接口设计的分析,看完你就懂了

2021-05-19 06:38:12

分享一份《高速电路(PECL、LVECL、CML、LVDS)接口原理与应用》的讲义

2021-06-22 08:02:28

如SPI接口中,FPGA通过模拟产生时钟和串行数据与一个外部芯片进行通信,其建立和保持时间是有时序要求的,这个时序要求可以通过外部的手册上获得。那么在FPGA中模拟这个接口要如何保证这个时序要求呀

2023-04-23 11:35:02

摘要:RS 232接口是现在最常用的一种通信接口。随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量,提高系统集成度和可靠性。详细阐述

2019-06-19 07:42:37

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于FPGA内部的寄存器都有特殊的意义,不同的时钟周期执行不同的操作

2017-02-26 09:42:48

1、 EMC的产生原因及防护手段在高速无刷电机中,EMC的问题往往是整个项目的重点及难点,从开始整改到整改结束需要花费大量的时间,因此我们需要正确的认识到EMC超标的原因以及其对应的整改方法。EMC

2023-03-13 13:52:27

的建立时间和保持时间。 1、建立时间的分析如图 7所示,建立时间的分析是以第一个launch Edge为基准,在Latch Edge查看结果。建立时间的裕量(T为时钟周期):Setup Stack

2018-04-03 11:19:08

如何满足各种读取数据捕捉需求以实现高速接口?

2021-05-08 09:19:15

如何用低成本FPGA解决高速存储器接口挑战?

2021-04-29 06:59:22

本文将介绍如何通过PCI接口,为MPC5200设计一个基本的高速摄像机接口电路。

2021-05-14 06:46:29

本文将要讲解和实现的内容主要分为两个部分:代码实现IIC接口管理、代码实现IIC时序。IIC接口管理接口管理的目的是想在后期扩展时,一个工程里可使用多个IIC接口。这里暂不考虑使用复杂的数据结构

2020-01-04 07:00:00

今天跟大家分享下浙江大学原创的“高速设计讲义”(如有侵权请告知),内含设计方法、信号完整性、板级高速时序分析!{:19:}

2016-08-17 14:14:57

本文在对Virtex-5 RocketIOTM GTP进行了解的基础上,针对串行高速接口开发中位宽不匹配的问题,提出了一种位宽转换方法,以解决Virtex-5 RocketI0TM GTP无法直接应用于某些串行高速接口开发的问题,并就SATA2.0接口开发中该问题的解决方案进行详细阐述。

2021-05-28 06:21:43

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

Hi,以前在学校的时候就经常遇见时序收敛的问题,尤其是改RTL好麻烦啊。工作以后和朋友们一起做了个时序优化的软件,叫InTime,希望可以帮助有相同问题的朋友。^_^我们搞了免费试用的活动,有兴趣

2017-05-11 10:55:17

验证模拟量ADC高速采集方案 1.目标 验证CH341A+ADC7606芯片实现ADC高速采集的可行性; 查阅CH341芯片并口通信协议DLL API,并口模式切换配置方式,并口操作速度

2023-03-27 11:49:21

浮点运算提高速度,减小代码量有什么方式?

2023-10-16 06:25:04

用于高速数据转换器的串行接口有哪些选择?

2021-04-09 06:55:28

降低效率为代价。优化配电网络可以改善这些参数,同时将噪声降低到必要的水平。本文在阐述高性能信号链中电源纹波的影响的基础上进一步分析。我们将深入探讨如何优化高速数据转换器的配电网络。我们将对标准PDN

2021-07-17 07:00:01

当今高速数字接口使用的数据传输速率超过许多移动通信设备(如智能手机和平板电脑)的工作频率。需要对接口进行精心设计,以管理接口产生的本地电磁辐射,避免接口信号受其他本地射频的干扰。本文探讨了管控高速数字接口EMI的若干最重要技术,说明了它们是如何有助于解决EMI问题的。

2019-07-25 06:26:02

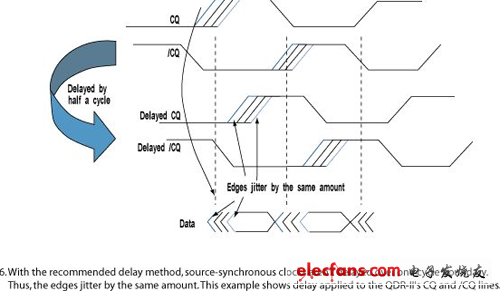

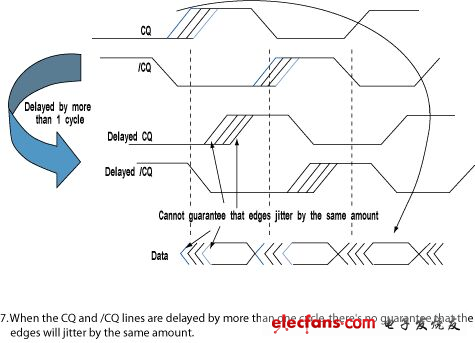

上引起的差异,为了更好地说明这些Skew对时序的具体影响,下面我们还是通过时序图分析的方法来计算一下源同步时钟系统中信号的建立时间裕量和保持时间裕量。首先考虑建立时间裕量:和普通时序分析的方法一下,我们也是从

2014-12-30 14:05:08

紫光的FPGA哪些系列支持高速接口?相关接口有哪些免费的IP可以使用呢?性能怎么样?

2024-03-20 16:58:29

如何收敛高速ADC时序?有哪种办法可以最大化ADC的建立和保持时间?

2021-04-14 06:06:09

为什要提出一种基于FPGA的PXA270外设时序转换接口设计方案?怎样去设计PXA270外设时序转换接口?

2021-04-30 06:25:58

新手,需要对一个工程时序优化,现在只能到110MHZ, 需要到150MHZ以上,跪求时序优化资料或例程。。

2015-12-05 11:22:54

频率30kHz"54kHz,垂直扫描频率50Hz"120Hz,带宽75MHz。基于DSPBuilder的VGA接口设计方法本设计需要完成的功能包括产生VGA时序以及基于VGA接口

2019-06-04 05:00:12

问题:采用单电源供电时,我的运算放大器输出会高度失真。这可能是因为某种裕量问题吗?答案:裕量(headroom)肯定是输出失真的众多原因之一。有些人可能还不熟悉裕量的概念,它用于衡量放大器的输入

2018-10-31 10:23:35

变则通,通则久。事物都有其运行的规律,把握好规律,就能更好的实现人的目的。在数字后端设计中,时序优化一直是关键问题,尤其追求高频高性能的设计中,时许问题常常贯穿始终。大大小小二十几个项目模块后端工作

2020-12-10 07:37:31

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 为解决ARCNET协议器件COM20020应用于列车通信网络时,与中央控制单元(CCU)处理器PXA270之间时序不匹配的问题,提出一种基于FPGA的PXA270外设时序转换接口设计方案。此外,还

2010-12-28 10:29:40 14

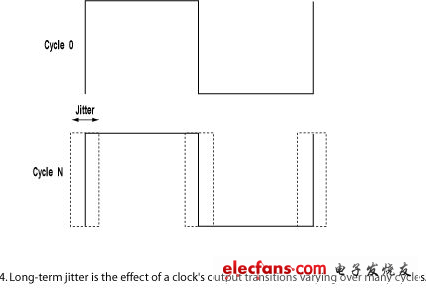

14 摘要:随着高速信号的普及,迫切需要保证这些信号接口能够维持正确时序和保真度的措施。上升时间一般在亚纳秒级,传输延时在纳秒级。系统对时序的要求越来越严格,如果不

2009-05-05 08:30:48 767

767

TMS320F2812慢速外设接口的时序控制

TMS320F2812通常能够实现与常用外围芯片的时序匹配,如RAM、D/A等;但是,当遇到读、写周期十分缓慢的输入/输出设

2009-09-27 16:33:01 2500

2500

更高速的 ADC 在转换器输出和接收机输入之间有严格的时序要求;知道如何利用产品说明书数字来保证无错误数字传输。

最近几年,高速、高精度的模数转换器 (ADC)

2010-07-13 09:59:10 660

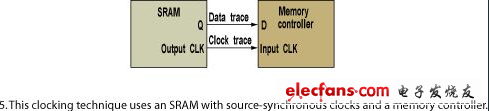

660 一、摘要 从简单SRAM接口到高速同步接口,TimingDesigner软件允许设计者在设计流程的初期就判断出潜在的时序问题,尽最大可能在第一时间解决时序问题。在设计过程的早期检测到时序问题,不仅节省时间,而且可以更容易的实施设计方案。美国EMA公司的设计自动

2011-01-13 16:25:00 103

103 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 本内容详细介绍了高速PCB设计的布局布线优化方法,欢迎大家下载学习

2011-09-27 16:22:33 0

0 对于广大PCB设计工程师而言,提到时序问题就感觉比较茫然。看到时序图,更是一头雾水,感觉时序问题特别深奥。其实在平常的设计中最常见的是各种等长关系,网上流传的Layout Gu

2012-10-22 11:51:56 4104

4104

电子发烧友网核心提示 :RS 232接口是现在最常用的一种通信接口。随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量

2012-11-27 10:28:11 5937

5937 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1169

1169 配置控制器局域网络(CAN)位时序,优化系统性能

2016-01-07 16:18:57 0

0 基于FPGA的高速固态存储器优化设计_杨玉华

2017-01-13 21:40:36 1

1 基于FIFO的高速A_D和DSP接口设计

2017-10-19 14:10:23 9

9 高速SPI和SCI接口

2017-10-20 10:29:04 10

10 针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 6488

6488

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 与赛灵思FPGA连接的数据转换器正迅速采用全新JESD204B高速串行链路。要使用该接口格式及协议,设计必须考虑一些基本硬件及时序问题。

2018-07-19 13:51:00 5434

5434

因高速问题产生的信号过冲、下冲、反射、振铃、串扰等将严重影响系统的正常时序,系统时序余量的减少迫使人们关注影响数字波形时序和质量的各种现象。由于速度的提高使时序变得苛刻时,无论事先对系统原理理解得多么透彻,任何忽略和简化都可能给系统带来严重的后果。

2019-06-03 15:18:15 735

735 优化高速连接的关键是确保最小的信号丢失量。一旦识别出连接的带宽,就可以进一步探索s参数以完理解连接的本质。

2020-05-29 10:37:15 799

799 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 17

17 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 19

19 高速电路信号完整性分析与设计—时序计算

2022-02-10 17:16:41 0

0 1、如何降低功耗?

(1) 优化方向:

组合逻辑+时序逻辑+存储

(2) 组合逻辑:

(a)通过算法优化的方式减少门电路

(b)模块复用、资源共享

(3) 时序逻辑:

(a)尽量减少无用

2022-02-11 15:30:36 2

2 Interline CCD 图像传感器的垂直时序优化

2022-11-15 20:36:34 0

0 使用STM32高速缓存优化性能和能效

2022-11-21 17:07:40 0

0 本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列文章的第1部分)。本文探讨了模拟前端时序、ADC时序和数字接口时序中的信号链考虑因素。

2022-12-13 11:20:18 1057

1057

本应用笔记介绍了与DS80C320以外的Maxim高速微控制器的外部存储器接口。使用这些微控制器的系统设计人员必须了解不同器件系列的多路复用地址/数据锁存要求和锁存参数。讨论了EPROM和SRAM参数,以确保微控制器和外部器件之间的正确匹配。

2023-03-01 13:56:28 715

715

在现代电子设计中,高速信号的传输已成为不可避免的需求。高速信号传输的成功与否,直接影响整个电子系统的性能和稳定性。因此,PCB设计中的高速信号传输优化技巧显得尤为重要。本文将介绍PCB设计中的高速信号传输优化技巧。

2023-05-08 09:48:02 1143

1143 电子发烧友网站提供《基于MC33771C和MC33772C的系统时序优化.pdf》资料免费下载

2023-08-17 14:13:06 1

1 电子发烧友网站提供《嵌入式系统外围接口的时序分析与电路设计.pdf》资料免费下载

2023-10-09 16:50:13 1

1 德索工程师说道设计是提升M12 5芯接口性能的关键环节。首先,应对接口的整体结构进行优化设计,减小插针与插孔之间的接触电阻和电感。这可以通过精确计算插针和插孔的几何尺寸,优化接触面积和接触压力来实现。同时,还需要考虑接口的热设计,确保在高速传输过程中能够有效散热,防止因过热而影响性能。

2024-03-21 15:02:38 26

26

电子发烧友App

电子发烧友App

评论