摘 要: 在进行非真实感渲染(NPR)处理时需要大量的计算,这对高帧率、高分辨率的视频做实时的NPR渲染是一个难题。根据FPGA以并行运算为主的特点,对传统的NPR算法做了改进和简化,最终设计了一种基于FPGA的实时NPR系统。实验结果表明,该系统对高帧率、高分辨率的视频做实时NPR处理具有运算速度快、系统稳定等特点,同时还具有体积小、便于携带等优点。

0 引言

非真实感渲染(NON-photorealistic rendering,NPR)是计算机图形学的一类技术,主要模拟艺术形式的画面风格,也用于发展新的绘制风格。与传统的追求真实感的计算机图形学不同,NPR受到油画、素描、技术图纸和动画卡通的影响。它已经以卡通造影的形式出现在电影和电子游戏中。非真实感绘制技术从20世纪80年代开始兴起,当时的研究进展缓慢。直到90年代中期,尤其是EUROGRAPHICS和SIGGRAPH上关于这方面的几篇论文才确立了这一领域的雏形[1]。近年来,NPR越来越多地被应用到各个领域,例如视频通信、视频游戏、精密程度较高的医学和科学插图[2],由此可见高分辨率、实时的NPR系统越来越凸显出重要的地位。

目前实现NPR处理主要有两种途径:一种是在PC机上进行处理[3-7];另一种是在嵌入式系统中进行处理[8]。参考文献[3]和参考文献[4]主要在PC上针对单幅图片做了NPR处理,参考文献[5]利用OpenCV API在计算机上对图片和视频实现了抽象处理,参考文献[6]和[7]则在PC上用特征流法和光流法等特定算法对视频做了抽象处理。在NPR系统中,图像滤波、边缘检测、色彩变化等都需要大量复杂的运算。因此在PC上很难对分辨率稍大或者帧率稍高的视频做到实时处理。又由于PC机体积较大,不方便系统的移动,所以在嵌入式系统上做NPR是必然的趋势。参考文献[8]则是在一个以Xilinx Virtex-2 FPGA为核心的平台上对单一图片做了油画处理,但是由于其平台的限制,并未实现对视频的实时处理。

本文在以Xilinx Virtex-5 FPGA为核心的自行设计的高速图像处理平台上,实现了对Camera Link接口相机采集到的视频做实时的NPR渲染,并输出到显示器上进行显示。本文首先对NPR算法进行讲解,然后对系统和NPR算法的硬件结构做出具体分析,最后给出实验结果及结论。

1 算法描述

虽然NPR渲染的具体实现方法多种多样,但是它们的处理流程大致相同。经过大量的文献查阅,主流的NPR渲染流程都要经过边缘增强、扩散滤波、量化光照信息三个步骤。本文也采用这种流程进行处理,每个步骤所采用的具体方法将在下面进行介绍。

1.1 边缘增强

当检测到边缘点之后,把边缘点的RGB分量全部置为0,即可达到边缘增强的效果。目前主流的边缘检测方法有差分边缘检测、Roborts算子、Prewitt算子、Kirsh算子、Laplace算子、LOG算子和Canny算子,考虑到在FPGA上实现的复杂性及资源利用率,本文采用的是Prewitt算子。

通常情况下,边缘检测每次只对图像中3×3的图像块进行处理,如图1(a)所示。图像块的第一行和第三行的差近似x方向的导数,第三列与第一列之差近似于y方向的导数[9]。如下所示:

Gx=(z7+z8+z9)-(z1+z2+z3)(1)

Gy=(z3+z6+z9)-(z1+z4+z7)(2)

上面就是Prewitt算子,Prewitt算子只有简单的加减法,非常适合于FPGA实现。Prewitt算子模板如图1(b)和(c)所示。

1.2 扩散滤波

NPR的另一个重要步骤是扩散滤波,它能模糊较小的不连续和突出的边缘,并且达到图像色彩扩散的效果。处理速度较快的经典图像滤波算法有邻域平均法和中值滤波法等。由于要实现扩散滤波的效果且要兼顾FPGA的运算特点,本文决定采用邻域平均法。邻域平均法是把相邻像素的相应分量值的平均值作为中心点像素相应分量值。若输入图像中某点的各分量值为f(j,k),以其为中心,取N×N的窗口像素组成的点集用A表示(其中N=3,5,7…)。经邻域平均法滤波后,像素f(j,k)对应的输出为[10]:

此算法的优点在于算法简单,适于在FPGA上实现,而且能达到色彩扩散的目的。

1.3量化光照信息

抽象效果的特点是原始输入图像中的很多细节信息被忽略,大块区域的颜色比较接近或均匀[3]。因此,对图像进行亮度信息量化操作是必要的步骤,以此来实现分块化效果。式(4)是量化的计算公式:

由于此计算公式需要进行正切计算,对FPGA来说复杂度较高,所以本文只是将RGB各颜色分量的低位置1,只保留高3~4位的有效信息,这样也能达到忽略细节信息的目的,让以前颜色基本相同的区域都保持一致。

2 硬件设计

2.1 系统结构

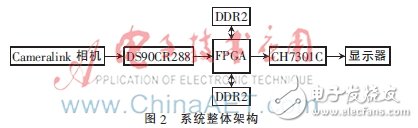

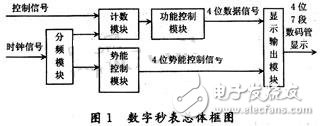

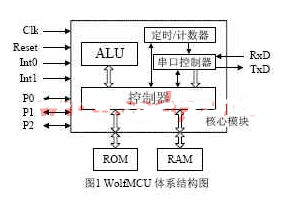

系统的前端采用的是一个Camera Link接口的工业相机,用于视频采集。相机分辨率为767×576,帧率为60 f/s,相机时钟为36.15 MHz。视频数据通过Camera Link线缆传到图像处理平台上,然后由一个接收芯片DS90CR288将收到的差分信号转换成24位RGB图像数据,再将数据传到FPGA中。系统使用的处理器是Xilinx公司V5系列的一款FPGA芯片xc5vlx110t。FPGA利用两片DDR2内存对图像进行缓存、处理,最后控制DVI芯片CH7301C进行实时显示。系统的整体架构如图2所示。

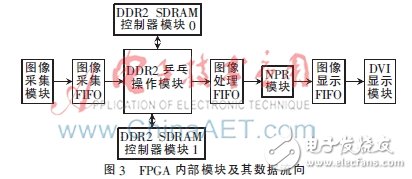

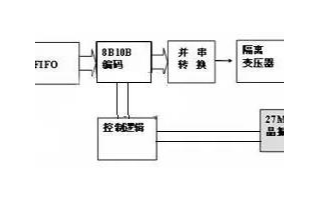

FPGA内部首先由图像采集模块将图像传到图像采集FIFO中,然后由乒乓操作模块将图像采集FIFO中的数据进行乒乓操作暂存到DDR2里面,实现前后速度的匹配,再将数据输出到图像处理FIFO。NPR模块读取图像处理FIFO中的数据进行处理后输出到图像显示FIFO,最后DVI显示模块读取图像显示FIFO中的数据进行显示,FPGA内部模块及其数据流向如图3所示。

2.2 NPR模块

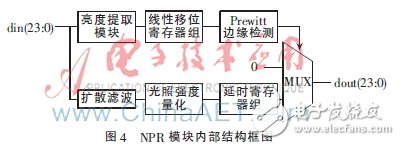

经过DDR2乒乓缓存过后的24位RGB图像数据输出后会通过NPR模块。在NPR模块中,图像数据分成两路:一路数据进行边缘检测,首先通过亮度提取模块进行亮度提取,然后进入一个行缓冲模块,进行三行完整图像的缓存,最后进入边缘检测模块,进行水平和垂直方向的边缘检测。另一路数据主要进行色彩滤波和光照强度量化,以及为了达到时序匹配而做的延时。最后由选择器进行选择输出,若是边缘则输出黑色,否则输出另一路处理过后的图像数据。NPR模块整体结构如图4所示。

2.2.1 亮度分量提取

通常情况下,边缘检测是对灰度图像进行的,由于相机采集到的图像是RGB图像,所以必须进行彩色图像到灰度图像的变换,即提取亮度分量。亮度分量Y和RGB的转换公式是:

Y=0.229×red+0.587×green+0.114×blue(5)

考虑到FPGA中更适合于做加减及移位运算,所以将式(5)做如下的近似变形,这样用简单的移位运算就可以轻松地实现亮度分量的提取:

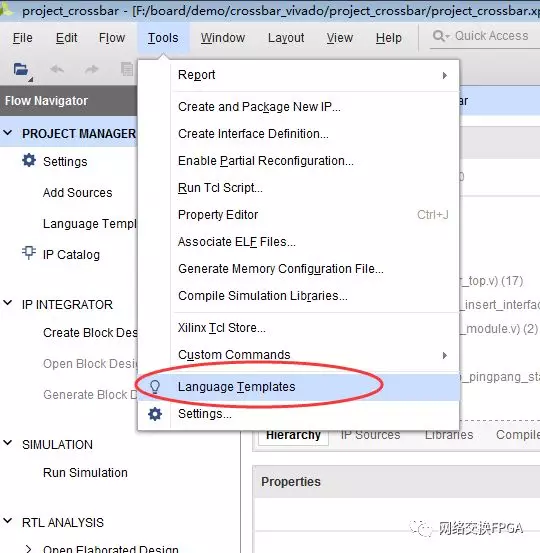

这样既能获得较好的提取效果,又能将浮点运算和乘法运算转化为简单的移位运算。最后的硬件结构如图5所示。

2.2.2 边缘检测

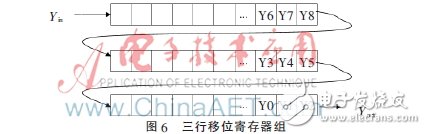

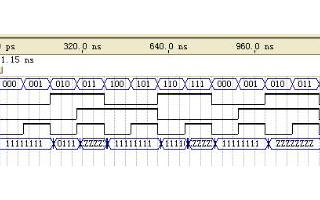

用Prewitt方法进行边缘检测,本质上就是将上面介绍的Prewitt算子分别与灰度图像做卷积,然后用梯度计算公式计算该点的梯度值。要实现图像与模板的卷积,必须同时获得三行图像的数据,为了达到这个目的,本系统使用一个三行移位寄存器组,用来存储前一步得到的亮度信息,效果如图6所示。

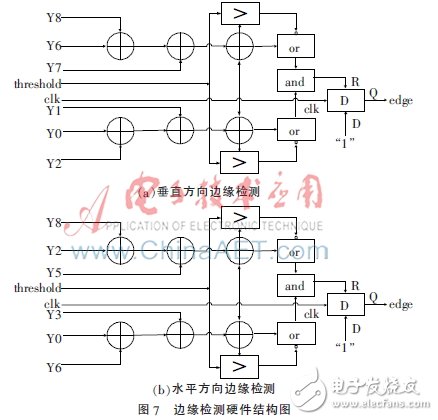

每次将这三行的前三个点组成的一个3×3矩阵分别与模板作卷积,就能分别得到垂直与水平方向的梯度。为了避免开方运算,直接将垂直与水平方向的梯度与门限做比较,只要任一方向的梯度高于门限值,就认定这个点是边缘点,上述操作虽然要求得到梯度值的绝对值,但与典型开方近似运算JPL算法相比,减少了3个时钟周期并且降低了算法复杂度。经过多次实验对比验证,本系统最后选定了一个固定的门限值30。其垂直与水平方向的边缘检测硬件结构图分别如图7(a)和(b)所示。

2.2.3 扩散滤波

视频中的图像帧通常带有时域和空域的噪声,因此,首先需要对其进行平滑去噪处理。通常情况下使用的是双边滤波,双边滤波是结合图像的空间临近度和像素值相似度的一种折中方法,离得较远的点不会对边缘上的像素值造成太大影响,具有简单、非迭代、局部的特点,可以实现边缘保存,而维纳滤波和高斯滤波都会有明显的模糊边缘。本文采用一种和双边滤波的局部特点相似的方法,将图像分成2×2的小块,同时进行时域和空域的均值滤波。

首先进行时间域滤波。这个模块会把当前像素点的值与过去该点的值做平均计算,其中过去的值存储在一个FPGA上的block ram模块里面,因为系统最后会把低位全部置为1,所以低位并没有必要做处理,因此每个像素点只存RGB的高4位。本文决定使用4帧图像来做平均值计算,因为这样系统只需要将当前值的1/4与过去值的3/4相加即可,而过去值的3/4可以表示为1减去1/4,这有利于FPGA实现,将除法运算变成了简单的移位运算。公式如下所示:

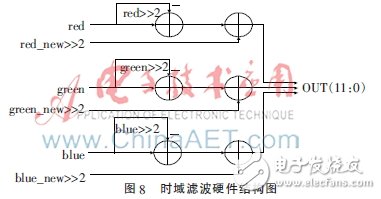

硬件实现如图8所示。

然后进行空间域的均值滤波。本文将图像划分为2×2的小块,每次滤波都以这种小块为基础,这个特点类似于双边滤波器的局部特性,有利于做到边缘保持。具体做法是:先设计两个计数器,用来模拟图像的行计数Y与列计数X,然后将X与Y方向坐标的最低位移除以产生block ram模块的地址,这样就使相邻的4个点都参考block ram模块的同一个点。使用此方法可以减少FPGA上实现block ram模块的资源大小,节约资源。由于block ram模块的读和写各需要一个时钟周期,如果要做滤波,每个时钟周期都需要从block ram模块里面读出一个旧值,同时还要存入前一个时钟变化后的值,这就导致了一定的时序问题,但是由于系统是以2×2的块进行滤波,相邻的四个点参考同一个点,因此系统就可以用一个时钟读出block ram模块里的数据并做处理,处理后的数据暂存在寄存器中,第二个时钟周期到来的时候就可以将刚才寄存器中的数据拿来参加计算而不必重新从block ram模块中读出数据。与此同时,利用列计数X的最低位来控制将变化后的数据存进block ram模块,以达到时序的匹配。至此,滤波结束。整个流程的硬件结构如图9所示。

2.2.4 量化光照信息

由于量化光照信息算法复杂度较高,不利于在FPGA上实现,本文只简单地将红绿蓝通道低位全部置1。而人眼对绿色分量变化敏感,所以对绿色通道保留高4位的有效信息,红和蓝通道只保留高3位的信息,这样做可以忽略色彩变化不明显的区域,达到量化光照信息的目的。

3 实验结果

、

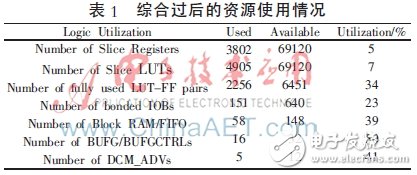

由于相机分辨率限制,本文只对分辨率为640×480、帧率为60 f/s的视频进行验证。由于NPR模块需要缓存三行数据,处理时钟为64.8 MHz,所以总延时t可由式(8)计算得30 ?滋s,达到了实时处理的效果。由前面的算法分析知本系统采用流水线结构,时延小,完全可以对分辨率更高、帧率更高的视频做实时NPR渲染。本系统在ISE下综合之后的资源利用率如表1所示,系统仅消耗了整个FPGA slice资源的5%。但是由于要在FPGA上暂存1/4帧的图像以及三行完整的图像数据,所以消耗了39%的Block RAM资源。如果图像更大,可以考虑在FPGA外围加上SRAM芯片,这样可以避免占用太多FPGA片上的Block RAM资源。

4 结论

非真实感渲染技术越来越多地被应用到各个领域中。本文使用VHDL语言设计了基于FPGA的实时NPR系统,该系统在自行研发的以Virtex-5 FPGA为核心的高速图像处理平台上得到了实现,并且具体分析了NPR算法的硬件实现流程及方法。由实验结果可知,该系统实时性好、体积小、便于携带,具有较强的工程应用价值。

电子发烧友App

电子发烧友App

评论