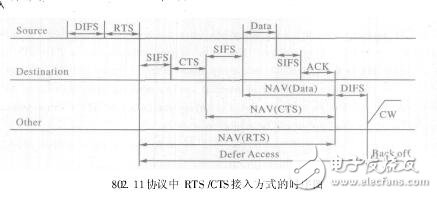

在RS232 中本来 CTS 与 RTS 有明确的意义,但自从贺氏(HAYES ) 推出了聪明猫(SmartModem)后就有点混淆了,不过现在这种意义为主流意义的,各大芯片制造厂家对 UART

2021-05-17 11:35:41 7384

7384

时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 1283

1283 ,我只需要把芯片的RX和TX连接到PSoC,对吗?在UART PSoC上没有CTS和RTS可用吗?谢谢你

2019-10-29 09:52:04

ClockTree Synthesis,时钟树综合,简称CTS。时钟树综合就是建立一个时钟网络,使时钟信号能够传递到各个时序器件。CTS是布局之后相当重要的一个步骤,在现如今集成了上亿个晶体管

2019-01-18 17:35:57

我对从 ESP32-S2-WROOM 到我的主机设备的 UART 接线非常困惑。主机设备需要 RX、TX、RTS 和 CTS。由于我使用 UART0 进行编程,因此我想使用 UART1 在我的主机

2023-03-01 06:33:14

: uart7_sleep_mx-0 { pins {pinmux = , /* UART7_RX */, /* UART7_TX */, /* UART7_RTS */; /* UART7_CTS

2022-12-28 08:53:58

逻辑电路分为组合逻辑电路和时序逻辑电路。第四章已经学习了组合逻辑电路的分析与设计的方法,这一章我们来学习时序电路的分析与设计的方法。在学习时序逻辑电路时应注意的重点是常用时序部件的分析与设计这一

2018-08-23 10:28:59

这种时序图第一次见,不会分析。1.希望技术支持或者哪位大神从编程的角度分析一下这个时序。2.上面的线为什么是曲线,代表什么意思?3.CLK正负的产生源可否是由DSP的引脚产生,经反相器,通过电容,形成两路互补的信号?附件图像 1.png35.7 KB

2018-12-03 09:15:27

请告诉我有关 CY7C65223-24LTXI 的引脚处理的信息。

不使用流量控制功能时,RTS 和 CTS 引脚是否应处于打开状态?

2024-03-07 07:54:55

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多的问题。(特权同学,版权所有)言归正传,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序

2015-07-09 21:54:41

首先是背景。我正在做一个USB到串行转换器,相当于一个老学校RS232模拟调制解调器。(后端是唯一的,但是前端使用RS232端口(TX、RX、RTS、DTR、CTS、DSR、RI和DCD)中正常的8

2018-12-11 15:01:43

配置为我的项目输出系统时钟的DCM。自定义此IP后,我有以下问题:Spartan-3 DCM需要哪些约束(用于时序分析),它们是否会自动放置在我的项目中的某个位置?

2019-08-02 09:54:40

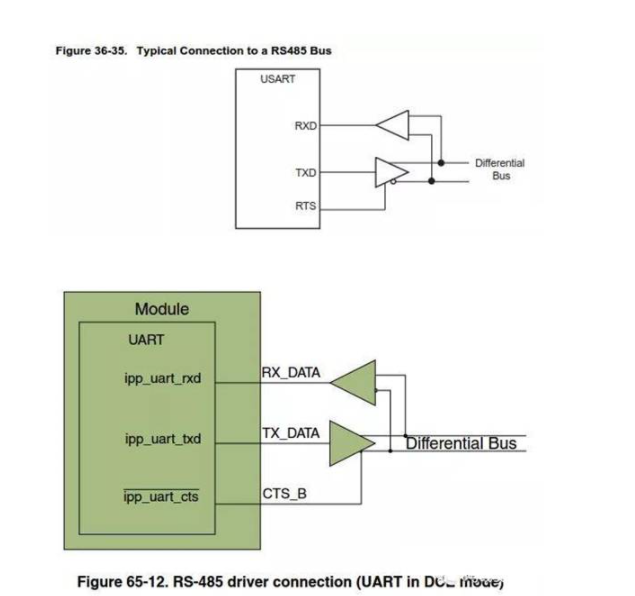

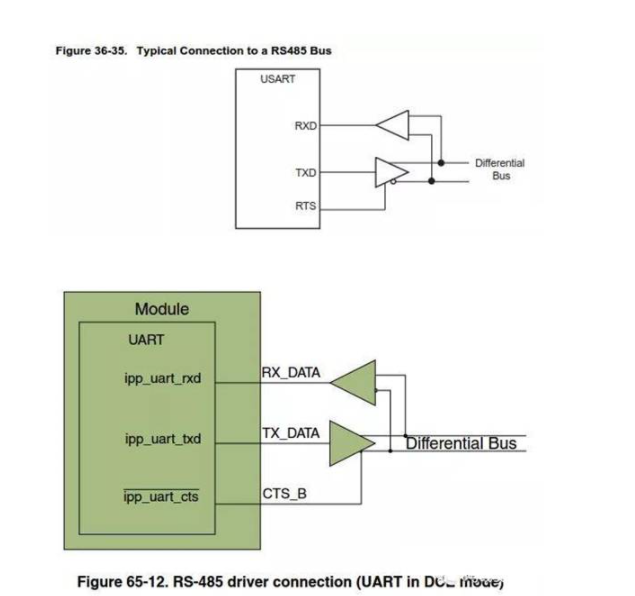

UART中的硬件流控RTS与CTS最近太忙了,没时间写对Ucos-II的移植,先将工作中容易搞错的一个知识点记录下来,关于CTS与RTS的。在RS232中本来CTS 与RTS 有明确的意义,但自从贺

2021-08-11 09:06:46

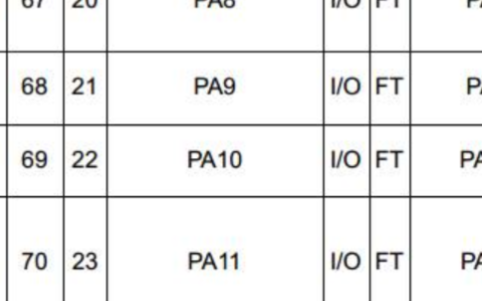

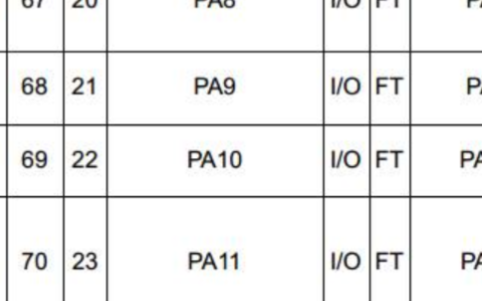

用的是STM32F407,如果我配置的时候不用USART2的硬件流控,那PA1这个脚能用作ADC1_IN1的功能么,USART2_RTS和ADC1_IN1都在PA1上。USART已启用情况下,如何将RTS和CTS引脚当做通用IO使用?

2018-12-10 17:38:47

以下是USB底层信号的一些定义及时序图,虽然很简洁,但能理解后,对后续的USB学习是很有帮助的,特推荐给大家!BTW,本月(4月20号周六)在深圳有一场很接地气、很容易入门的USB线下、小型技术交流

2019-04-08 16:30:26

自己做了一个工程,静态时序分析的结果CLK信号的SLACK是负值(-7.399ns),书上说该值是负值时说明时序不对,但是我感觉时序仿真的结果是对的。是不是时序仿真波形正确就不用管静态时序分析的结果了?请高手指点

2010-03-03 23:22:24

小弟接触串口通讯不深,试过max232串口电路三线制可以成功传输数据;现在想使用max3232进行通讯,参考电路如下: RS232端有四根信号线,TX\RX\RTS\CTS,在max232电路中三

2012-11-15 17:51:39

跟大家分享一下 u***转串口 9针 引脚定义:1 DCD载波检测2 RXD 接收数据3 TXD 发送数据4 DTR 数据终端准备好5 SGND 信号地线6 DSR 数据准备好7 RTS 请求发送8 CTS 清除发送9 RI振铃提示可以通过短接2、3 判断电脑串口是否正常,如图:

2016-03-27 14:06:18

芯片管脚有两组UART,一组UART_TX,UART_RX。一组 UART_CTS,UART_RTS,这有什么区别?都是作为I/O口,有其他用途? 请说说看法,以及言外...

2019-01-23 11:23:48

:一类用于片内各功能部件的控制,它们是芯片设计师关注的问题,对用户没有什么意义。另一类用于片外存储器或I/O端口的控制,需要通过器件的控制引脚送到片外,这部分时序对分析硬件电路的原理至关重要,也是软件

2018-07-21 16:38:31

定义:我从文档中推测,MAX3160Cap TTL端管脚定义MAX3160 TTL 管脚定义TXD:8RXD:16RTS:7CTS:152,MAX3160 RS232管脚定义:

2020-02-14 11:25:57

Ds1302Read(uchar addr);void Ds1302Init();void Ds1302ReadTime();这几个函数,是根据时钟芯片时序图定义的还是你自己想象出来而定义的?如果是根据时序图定义那时序图又要怎么看呢,哪些该写哪些不该写?

2016-06-10 10:39:48

你好

我正在使用 CYBT-343026 (CYW20706) 上的 PUART 向具有 CTS/RTS 流量控制的主机 MCU 发送/接收数据。 主机 MCU 有时会通过长时间拉高 CYBT

2024-03-01 11:31:04

哪里有讲stm32的USARTx_RTS和USARTx_CTS硬件流控制的,看了很多例子都是不用硬件流控制的

2017-03-24 13:44:29

可以通过程序框图中的VISA属性节点(Property Node)中的Modem Line Settings里的属性来读、写串口中的DTR和RTS等控制线。LabVIEW 6.x, 7.x请根据

2019-07-01 14:13:15

挑战。本文主要介绍了逻辑设计中值得注意的重要时序问题,以及如何克服这些问题。最后介绍了利用Astro工具进行时序分析的方法。关键词:ASIC;同步数字电路;时序;Astro引言 随着系统时钟频率的提高

2012-11-09 19:04:35

只能分析一些简单的时序图,稍微复杂点的就感觉力不从心啊,求讲解

2023-11-10 07:43:21

时间称为时钟抖动,如图 2所示。一般情况下的时序分析是不考虑时钟抖动,如果考虑时钟抖动,则建立时间应该是Tsu+T1,保持时间应该是Th+T2。 2.时钟偏斜时序偏斜分析图如图 3所示。时钟的分析起点是源

2018-04-03 11:19:08

以时钟芯片DS1302为例子来分析时序图并写出代码

2021-04-02 06:00:39

://forums.xilinx.com/t5/PicoBlaze/PicoBlaze-FAQ-Can-the-UART-support-CTS-RTS/td-p/636但我不明白如何实现流量控制的CTS和RTS信号。这些信号是否必要

2019-08-23 09:38:03

如何看时序图,如何用时序图?求一些详细的资料。

2013-01-21 12:29:00

电脑上软件的硬流控怎么配合板子上的CTS,RTS,以及板子上的CTS,RTS 和代码里的流控配置做配合,还是不太理解。我现在板子上的CTS和RTS用跳线帽连上了,然后我PC端上的流控开和关都能收到

2015-11-12 10:14:14

问个问题,拿过来一个芯片datasheet,怎么由它的时序图把程序写出来? 我看过一些芯片的时序图,懂是可以懂得,但再看程序,里面定义了很多函数,向I2C总线结构的程序,还有开启和关闭I2C,类似这种。。。能否只从时序图直接写出它的程序? 路过的朋友可以探讨下并留下你的宝贵建议,谢谢。

2013-12-17 10:10:57

IOMUXC_GPIO_AD_B0_09 引脚需要设置引脚,并且可以通过使用“fsl_iomuxc.h”中的“IOMUXC_GPIO_AD_B0_09_LPUART1_RTS_B”定义来实现。在这种情况下,我可以

2023-05-05 09:52:21

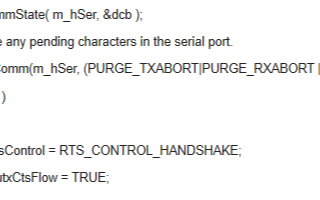

大家好,求助一个问题,有偿,会给你冲手机话费,问题如下:我在使用FT232时,上位机又是会连续发一些指令,这时下位机不能接收上位机的信息时就会对CTS置1,但是上位机检测CTS的代码如下,但是好像

2016-10-27 08:06:17

请教如何做时序分析

2013-06-01 22:45:04

连接MCU 的UART,但仅使用 TX,RX,请问RTS,DSR,CTS,RI,DTR,DCD,ACT等管脚应该如何处理(悬空?上下拉?)以及电源管脚的连接,是否有个不带流控的典型应用电路图

2022-07-05 06:46:13

哪位朋友用过ST的UARTS CTS/RTS,STM32F4 discovery USART CTS/RTS怎么设置?有官方提供的例子吗?

2018-09-04 09:38:09

想做个板子, 想把串口模块的线都接出来, 以供学习用(不管功能和作用怎么样), 其中RTS和CTS都能在9针串口定义中找到定义, 但没找到UART_CK, 问下这根线应该接在9针串口的哪个位置??再

2020-03-11 02:27:06

在库函数里的操作就是开启CTS RTS 或者是NONE可是真的体验和操作是怎么样才可以感觉得到的呢?

2018-10-15 08:54:23

请问串口的SR寄存器里的状态位为什么只有CTS判断的,没有RTS,在CR寄存器里也没有位是对RTS进行操作的,难道是要直接对GPIO置1和0进行操作吗?

2019-02-26 08:00:36

请问串口的SR寄存器里的状态位为什么只有CTS判断的,没有RTS,在CR寄存器里也没有位是对RTS进行操作的,难道是要直接对GPIO置1和0进行操作吗?

2015-11-15 14:45:37

电脑上软件的硬流控怎么配合板子上的CTS,RTS,以及板子上的CTS,RTS 和代码里的流控配置做配合,还是不太理解。我现在板子上的CTS和RTS用跳线帽连上了,然后我PC端上的流控开和关都能收到

2019-02-25 06:04:43

蓝牙模块的TX、RX、RTS、CTS和51单片机应该怎么连接嘞????求高人指导啊

2019-01-21 06:35:44

的周期。Duty cycle:高电平持续时间(正相位)和低电平持续时间(负相位)。Edge times: 上升沿和下降沿的时间。时钟约束通过定义时钟, 所有内部时序路径 ( 触发器到触发器路径 )都将

2023-04-20 16:17:54

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 特性

Programmable Auto-RTS and Auto-CTS

In Auto-CTS Mode, CTS Controls Transmitter

2010-09-09 22:18:03 7

7 !!好货 CTS60 CTS60 CTS 60 CTS-60 数字无线测试仪 谭艳飞13543805887欧阳’S现货中山市华仪通电子仪器有限公司联系人:谭艳飞(经理)手机:13543805887 电话: 0760-226808

2008-08-19 10:37:53 601

601 %$!二手 CTS65 CTS 65 CMD55 CTS60 综合测试仪 谭艳飞13543805887欧阳S

中山市华仪通电子仪器有限公司

联系人:谭艳飞(经理)欧阳婧(特助)

手机

2008-09-09 23:10:37 567

567 !!疯狂/甩卖 CTS60 CTS60 CTS60 数字无线测试仪 谭艳飞/李13543805887

2008-10-14 09:06:08 610

610 %$!二手 CTS65 CTS 65 CMD55 CTS60 综合测试仪谭艳飞13543805887欧阳S中山市华仪通电子仪器有限公司联系人:谭艳飞(经理)欧阳婧(特助)

2008-10-14 11:02:21 535

535 !!供应CTS55 CTS55数字无线综测仪CTS55 小兵/李小姐

东莞市银通电子仪器有限公司联系人:欧阳小兵/李小姐手机:13332662998/13790420385电话:0769-87912629传真:0769-87912842MAIL

2008-11-17 15:19:50 393

393 !销售/回收CTS60 CTS60数字无线测试仪CTS60.小兵/李S

东莞市银通电子仪器有限公司联系人:欧阳小兵/李小姐手机:13332662998/13790420385电话:0769-87912629传真:0769-87912842MAI

2009-01-17 16:05:35 534

534 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

定义了时钟单位阶跃信号C(n) 提出了一种利用带相对时钟坐标的逻辑方程表示逻辑信号的方法通过对所设计的DDR SDRAM控制器的读写时序的分析建立了控制器主要信号的时序表达式并利用

2011-09-26 15:34:12 39

39 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 _静态时序分析(Static_Timing_Analysis)基础及应用[1]。

2016-05-09 10:59:26 31

31 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 静态时序分析基础及应用

2017-01-24 16:54:24 7

7 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

!大量收购/回收CTS60综合测试仪CTS60 孙峰/何S:13549469921 东莞市宏达电子仪器有限公司 联系人:孙峰/何S(销售工程师):13549469921 客 服QQ

2018-03-27 05:11:01 1107

1107 STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。

2018-04-03 15:56:16 10

10 本文档的主要内容详细介绍的是UART中的硬件流控RTS与CTS的知识点详细资料说明。最近太忙了,没时间写对Ucos-II的移植,先将工作中容易搞错的一个知识点记录下来,关于CTS与RTS的。

2019-05-31 17:53:00 10

10 中低端路由器上使用disp interface 查看相应串口状态信息,其中DCD、DTR、DSR、RTS及CTS等五个状态指示分别代表什么意思? DCD ( Data Carrier Detect

2019-04-25 18:28:00 7

7 最近太忙了,没时间写对Ucos-II的移植,先将工作中容易搞错的一个知识点记录下来,关于CTS与RTS的。在RS232中本来CTS 与RTS 有明确的意义,但自从贺氏(HAYES ) 推出了聪明

2019-04-24 18:29:00 3

3 静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

ESM335x系列工控主板支持5路高速串口,其中COM2口支持硬件RTS/CTS流控功能,其RTS/CTS分别与ESM335x的GPIO1/GPIO0复用,应用程序可以独立设置是否使能RTS/CTS

2020-02-04 11:22:47 1273

1273

STM32的USART中RTS、CTS的作用和意义

2020-03-20 11:11:35 7101

7101

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 CTS7-100与CTS7-200的主要区别说明。

2021-05-09 10:21:49 5

5 方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

UART中的硬件流控RTS与CTS最近太忙了,没时间写对Ucos-II的移植,先将工作中容易搞错的一个知识点记录下来,关于CTS与RTS的。在RS232中本来CTS 与RTS 有明确的意义,但自从

2021-12-09 12:21:11 16

16 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095

正在加载...

电子发烧友App

电子发烧友App

评论