利用74LS00二输入与非门实现“与电路”、“或电路”、“或非电路”、“异或电路”、“同或电路”,要写出以上各电路的逻辑表达式和真值表,画出用二输入与非门实现的逻辑图并在实验箱上加以验证

2020-11-04 17:04:17

逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能,看!

2019-07-23 07:03:30

近期在做labview串口通讯程序,自己摸索的异或校验程序,进行分析,请指正!

2020-02-26 15:39:33

一款Proteus非门仿真供大家参考

2013-10-31 20:34:10

。

非门电路相当于一个求反电路,有且只有一个输入端。最多只有两种情况:1=0,0=1。

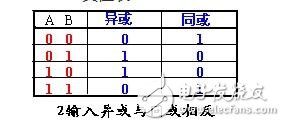

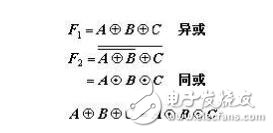

异或门电路的逻辑关系比较特殊,有且只有两个输入端。最多只有四种情况:0+1=1,1+0=1,0+0=0,1+1=0。

与非门电路则是将与门的结果求反,或非门电路则是将或门的结果求反,异或非门电路则是将异或门的结果求反

2016-05-17 22:42:06

74LS125 1块双全加器 74LS183 1块实验报告要求1. 画出实验逻辑图, 列出实验数据表格, 填入实验结果, 并写出各种门电路的逻辑函数表达式或逻辑功能。2. 叙述在与非门、或非门、异或门、三态门实验中用示波器观察方波波形的结果,并说明原因。

2008-09-25 17:28:34

组成的逻辑门电路,可实现2输入或3输入的AND,OR,NAND,NOR,EXOR操作。与非门或非门或门与门异或门三输入与非门三输入或非门三输入与门三输入或门

2019-07-08 10:36:28

个1个1个1个布尔表达式Q = A + B读为A或B得出Q反相逻辑门逻辑与非门符号真相表乙一种问001个01个1个1个01个1个1个0布尔表达式Q =A。乙读为A和B不会给出Q逻辑或非门符号真相表乙

2021-01-27 08:00:00

一、逻辑与或非基础理论:逻辑与或非,运算对象是布尔值(1或0,真或假),类似于数字电路的与门,或门,非门。与关系运算符配合,一般用于选择语句与循环语句中1、逻辑与符号为&&。 参与

2022-01-24 06:30:51

。此外,其他较为常见的二项运算逻辑门还有与非(NAND)门、或非(NOR)门、异或( EXOR)门等。与非门用来计算逻辑与的否定,或非门用来计算逻辑或的否定,而异或门用来计算异或逻辑。表3列出了这些

2020-12-23 17:25:49

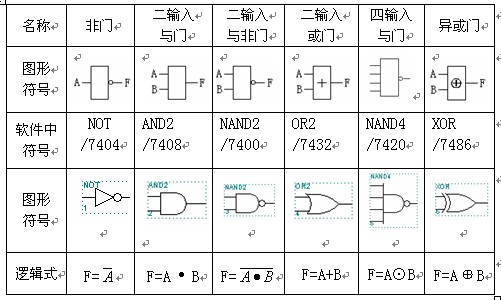

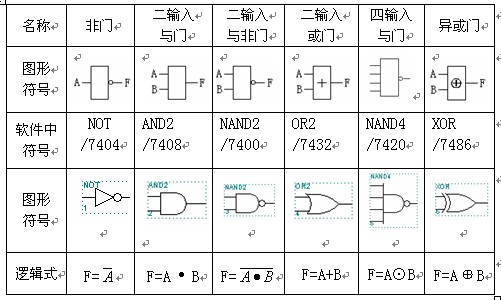

逻辑门电路电子教案 逻辑门电路:用以实现基本和常用逻辑运算的电子电路。简称门电路。 基本和常用门电路有与门、或门、非门(反相器)、与非门、或非门、与或非门和异或门等。 逻辑0和1: 电子电路

2009-09-16 16:10:39

FPGA中一个或门的延时有多少?求高手解答,会不会大于350ps?

2023-04-23 14:29:48

FPGA中等效逻辑门概念数的计算方法有两种,一是把FPGA基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA基本单元的等效门数,然后乘以

2012-08-10 14:05:35

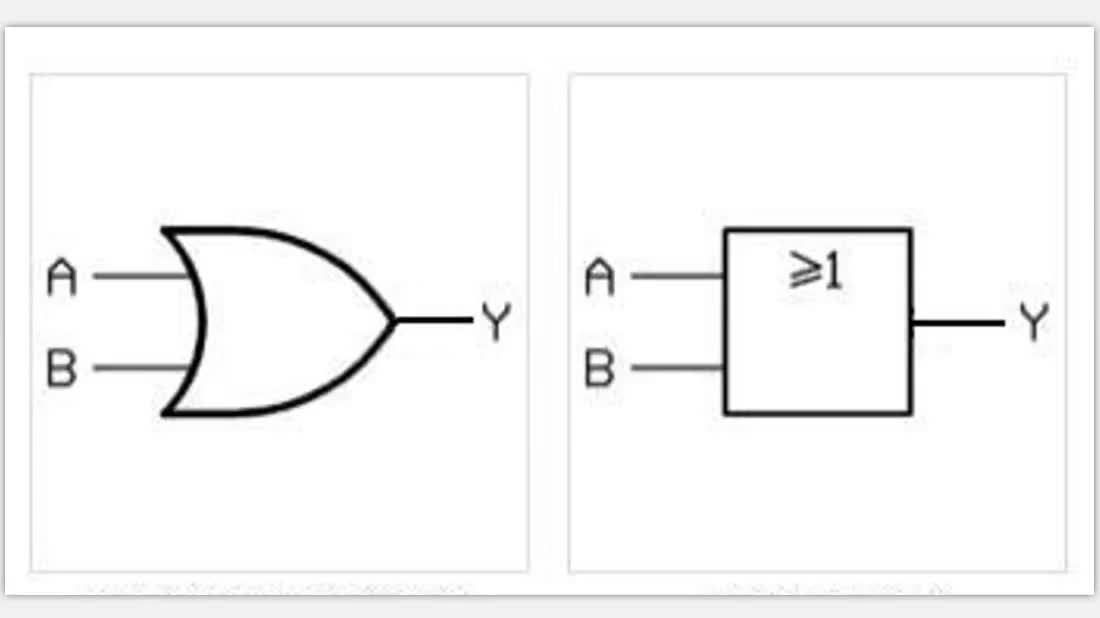

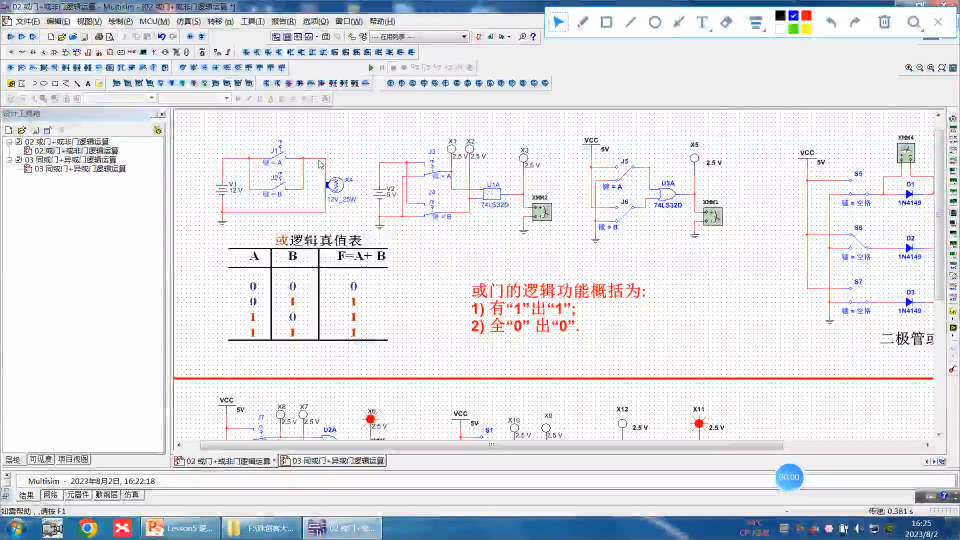

。输入x和y进行或运算后得到结果z。或运算的原则就是“遇1则1,全0则0”。图3.7 或门符号和真值表在与、或、非这三种最基本的逻辑门基础上进行一些扩展,就产生了一些常见的逻辑门如与非门、或非门

2015-01-22 21:46:14

进行或运算后得到结果z。或运算的原则就是“遇1则1,全0则0”。图3.7 或门符号和真值表在与、或、非这三种最基本的逻辑门基础上进行一些扩展,就产生了一些常见的逻辑门如与非门、或非门、异或门、同或门,其

2021-08-18 14:45:34

FPGA小白一枚,个人理解的FPGA本质上或者核心就是查找表(LUT),即将所有的函数/方法 转换为固定的查找表(使用DSP除外)。但是为什么所有的文章提到FPGA全部都注重逻辑门呢?其实FPGA本身内部也没有多少物理的逻辑门吧?

2019-05-30 10:53:46

GetHex计算异或值的软件,对十六进制的字符串进行异或校验,输出结果

2018-01-23 11:18:29

单片机逻辑与或异或指令,这几条指令的关键是知道什么是逻辑与。这里的逻辑与是指按位与ANL A,Rn ;A与Rn中的值按位'与',结果送入A中ANL A,direct ;A与direct中的值按位

2011-11-16 11:54:18

TTL逻辑门与普通逻辑门的区别在哪里为什么引入OC门?

2021-03-29 07:23:21

非门、与门、与或非门、或非门、或门和异或门等;为了改变两个以上门的输出间不能线与的的弊端,引入了集电极开路门;为了改进集电极开路门丢失了原有电路的图腾柱输出(速度快、输出阻抗低)特点,又引入了三态逻辑门

2018-08-24 16:30:23

请问各位,在异或运算时,如果两个输入端,一个有信号,一个没有信号,是不是就无法进行异或运算了?

2014-12-26 16:44:38

请问大家,pspice的逻辑门模型,比如说与门7408,该怎样修改其参数?我想修改7408的延迟时间,输出电平等等,怎么弄?关于右键点击然后edit pspice model的方法,我试过,只是出来

2014-06-24 10:09:17

的值(41H)相与,结果为(25H)=11H在知道了逻辑与指令的功能后,逻辑或和逻辑异或的功能就很简单了。逻辑或是按位“或”,即有“1”为1,全“0”为0。例:10011000或 01100001结果

2011-12-14 10:02:23

如图所示,或门的一个引脚会有一个一次性的50ms脉宽的脉冲,另一个输入与输出相连接,并用1KΩ的下拉电阻接地。同时或门的输出通过1个100Ω的电阻和一个发光二极管连接,驱动二极管发光。请问这种设计有

2018-03-14 21:14:15

输出上给出逻辑“ 1”,否则为逻辑电平“ 0”。然后,这种类型的门在输入“逻辑上相等”或“相等”时给出并输出“ 1” ,这就是为什么“异或”门有时称为“等效门”的原因。异或非门的逻辑符号只是在其输出

2021-01-25 09:20:33

加法器,因为它给出两个二进制数的总和,因此,其设计比其他基本类型的逻辑门更复杂。真值表,逻辑符号和2输入异或门的实现如下所示。数字逻辑“异或”门2输入异或门符号真相表2输入异或门乙一种问00001个1个

2021-01-23 08:00:00

端“或”门,输入直接连接到晶体管基极。对于Q的输出,两个晶体管都必须饱和为“ ON” 。逻辑或门可使用数字电路产生所需的逻辑功能,并带有一个符号,其形状表示或门的逻辑操作。数字逻辑“或”门类型2输入

2021-01-20 09:00:00

端“或”门,输入直接连接到晶体管基极。对于Q的输出,两个晶体管都必须饱和为“ ON” 。逻辑或门可使用数字电路产生所需的逻辑功能,并带有一个符号,其形状表示或门的逻辑操作。数字逻辑“或”门类型2输入

2021-01-21 08:00:00

具有两个或更多逻辑输入的“与”或“或”门。商用非门IC可在单个IC封装中的4个或6个单独的门中使用。上方非门符号结尾处的“气泡”(o)表示输出信号的信号反相(互补)。但是该气泡也可能出现在栅极输入端,以

2021-01-21 09:00:00

的逻辑的逻辑或布尔表达式NAND门的是,对逻辑加法,这是相反的AND门,以及它执行对互补的输入端。逻辑与非门的布尔表达式由单点或句点符号(。) 表示,在表达式上带有线或上划线(‾‾),以表示与非门的非或

2021-01-22 08:00:00

直接连接到晶体管的基极。两个晶体管都必须截止为“ OFF”,以在Q输出。逻辑或非门可使用数字电路产生所需的逻辑功能,并被赋予一个符号,其形状为带有圆圈的标准或门的形状,有时在其输出处称为“反转气泡”,以

2021-01-22 09:00:00

的是或门,我们要用三极管来打造一个或门。或逻辑门或门实现了布尔分离,能让我们找出两个输入中的最大值。或门符号或门的电路符号入上,其中弯曲的一端为输入端,尖锐的一端为输出端。或门遵循的逻辑很简单,如果有一个

2019-11-15 11:13:55

条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去.因此,需要一种新的与非门电路--OC门来实现“线与逻辑”.OC门主要用于3个方面:1、实现与或非逻辑,用做电平转换,用做驱动器.由于OC

2016-08-23 21:39:46

组成。 逻辑与运算对应逻辑门为与门;逻辑或运算对应逻辑门为或门;逻辑非运算对应逻辑门为非门;除此之外还有较为常见的 与非门(NAND)、或非门(NOR)、异或门(EXOR)等。当然目前主流的LSI技术

2019-12-10 20:32:03

门电路是由哪些元件组成的?TTL与非门的外特性及其参数有哪些?上拉电阻R对NMOS逻辑门电性能有何影响?

2021-11-05 09:08:47

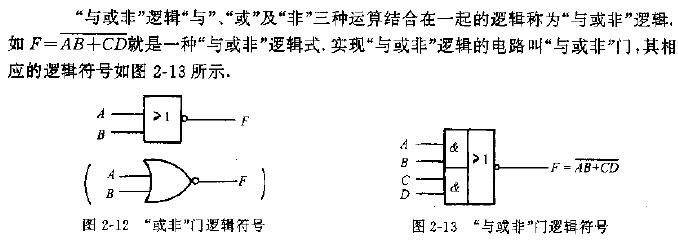

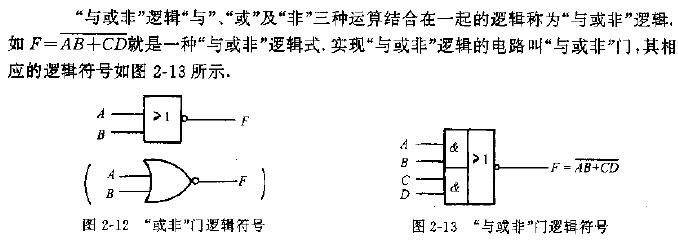

与或非门逻辑符号

2019-10-29 09:12:12

有与门电路,或门电路,非门电路等。 与门电路与门电路是指只有在一件事情的所有条件都具备时,事情才会发生。与门电路的基本结构和逻辑符号见下图在与门电路功能示意图中,只有在开...

2021-07-05 06:10:52

三态门和OC门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑,这种门电路

2008-05-26 13:01:37

从FPGA或PLD转换到门阵会遇到哪些时序问题?如何去避免这些问题的发生?

2021-04-30 06:54:18

和真值表在与、或、非这三种最基本的逻辑门基础上进行一些扩展,就产生了一些常见的逻辑门如与非门、或非门、异或门、同或门,其符号和真值表分别如图3.8、图3.9、图3.10和图3.11所示。图3.8 与非门

2017-11-20 21:26:46

的值(41H)相与,结果为(25H)=11H在知道了逻辑与指令的功能后,逻辑或和逻辑异或的功能就很简单了。逻辑或是按位“或”,即有“1”为1,全“0”为0。例:10011000或 01100001结果

2018-06-14 18:22:42

在上一教程中,我们研究了通常称为反相器的数字“非门”,发现“非”门的输出状态是其输入信号的互补,相反或反相。因此,例如,当非门的单个输入为“ HIGH”时,其输出状态将为“ HIGH”。当其输入信号

2021-01-26 09:16:58

网上看到有用二极管实现与或非的,想知道同或异或有没有可能实现。看到了一个说可以用三极管实现的,如下图

2017-09-18 16:37:36

1、集成逻辑门及其基本应用介绍本实验涉及到的基本逻辑门有“与门”、“与非门”、“或门”、“或非门”、“异或门”和“同或门”,功能简单,实验时使用2个拨动开关模拟逻辑门的输入信号,通过LED灯的点亮或

2022-07-01 15:18:51

本帖最后由 乐乐leles 于 2019-6-5 11:07 编辑

常用与、或、非逻辑门芯片引脚图一、或门:74LS32四路二输入或门74HC27 三路三输入或非门 二、与门:74LS21二路四输入与门 74LS11 三输入与门 三、非门:74LS04

2019-05-24 08:49:59

三态门高阻态时,同或门输出状态怎么判断?F的 逻辑表达式

2015-12-15 10:59:57

如何利用可用的软件方案以简化或避免昂贵的编程?

2021-05-11 06:23:36

你好。我是在FPGA上设计系统的初学者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想计算基本15位2输入加法器的逻辑延迟。如果我能检查AND门或OR门的延迟等

2020-05-25 07:28:24

嵌入式硬件(三)数字逻辑电路一、组合逻辑电路1.非门2.与门3.与非门4.或门5.或非门6.异或门7.三态门二、时序逻辑电路1.触发器(flip-flop)(1)RS触发器(2)D触发器2.锁存器

2021-07-26 08:02:44

输入端是15—35VDC直流三路,想通过这个或门芯片输出1路5VDC/0,手册里没有参考电路,请大神指导一下电路原理图

2022-01-21 15:48:44

),从而连接在一起或连接至固定电压。这些未使用的输入绝对不能随意浮动。上拉电阻确保数字逻辑门和电路的输入不会自偏置和浮动的最常见方法是将未使用的引脚直接接地(0V)以得到恒定的低“ 0”输入(或门或或非门

2021-01-28 08:00:00

有与门,或门,非门,与非门,或非门和异或门等。本次实验重点讨论其中的几个逻辑门用Verilog在Robei软件中的设计和仿真。以常见的与门为例,如图2-1-1所示,通过其真值表可以看出,只有当两个输入

2015-04-03 11:18:25

,输出为0,输入为1,输出为1;可以提高输入信号的能力缓冲门的图形符号A为缓冲门的输入,F为缓冲门的输出表达式为F=A非门:是仅有逻辑非功能的基本门电路,仅有一个输入端口,也有一个输出端口功能:将输入端口的信号电平取反后,再搬移到输出端口,输入为逻辑0,输出为逻辑1非门的图形符号A为非门的输入

2021-07-29 08:04:47

我有一个hex文件,我用labview把它打开之后转换成bin文件,现在需要对数据进行异或,数据如下其实这些都是十六进制的,这些是字符串正常显示的数据但是我给下位机发送数据的必须要求十六进制显示,也就是这些数据怎么进行异或呢?

2016-01-07 15:04:38

现在我需要一个逻辑门器件,与门和或门。要求是在输入时间为100ns的脉冲信号(可调),两个输入,一个输出。然后通过这个逻辑门器件之后可以用示波器检测到。。。新人也不懂 啊,需要什么型号的器件呢?

2018-09-17 16:01:36

更多信号,并且仅在所有输入关闭时才打开输出。下面是逻辑门的真值表和绘图。 也不或非门用于接收 2 个或更多信号,并且仅在所有输入关闭时才打开输出。下面是逻辑门的真值表和绘图。 异或异或门用于接收 2 个

2022-09-08 07:42:05

比较器/逻辑门输出地“高电平”单片机检测不出来,说短路,怎么解决?有图如图,我用两个比较器,然后接一个“或门”或门输出高低电平正常,单片机置低,当或门和单片机端口连接起来之后,就显示黄色(短路)了,或门的高电平不能把单片机引脚置高什么原因?这样的高电平怎么检测?(电路图)各自正常连接起来显示黄色的

2011-05-13 09:38:16

上一节我们讲了由NMOS与PMOS组成的CMOS,也就是一个非门,各种逻辑门一般是由MOSFET组成的。上图左边是NMOS右边是PMOS。上图两图是非门两种情况,也就是一个CMOS,输入高电压输出

2023-02-15 14:35:23

/topic-dianyabjq.html构建逻辑门只不过是将二极管逻辑与一些电阻组合起来,以实现必需的逻辑功能。图2给出了实现了逻辑“与(AND)”和逻辑“或(OR)”功能的简单电路,以及略为复杂的逻辑“异或(XOR)”功能的电路。图中

2011-12-23 11:49:06

组成的逻辑门电路,可实现2输入或3输入的AND,OR,NAND,NOR,EXOR操作。与非门或非门或门与门异或门三输入与非门三输入或非门三输入与门三输入或门

2018-10-11 17:44:32

列出4中能做非门的逻辑门(非门除外)

2010-04-29 18:54:58

异成门逻辑符号图/同或门逻辑符号图

2019-10-23 03:49:43

嗨,我是PSoC平台的新手,在我的游戏中,我遇到了影响逻辑门或定时器输入的需要,但是不能用软件来做。我的例子是使用XOR来屏蔽UART,抑制它的输出一段时间。这或触发闩锁。是否有可能从软件中写出类似

2019-06-27 10:25:40

“^”是按位异或那异或的符号是什么呢?

2014-05-25 18:56:53

钟控传输门绝热逻辑电路和SRAM 的设计本文利用NMOS管的自举效应设计了一种新的采用二相无交叠功率时钟的绝热逻辑电路---钟控传输门绝热逻辑电路,实现对输出负载全绝热方式充放电.依此进一步设计了

2009-08-08 09:48:05

?答:异或门是一种相斥或门,只有当它的输入有一个为1,另外一个为0时,它的输出才为1,否则输出为0。恒等式写为A○+B=L,其中“○+”表示异或。逻辑符号如图2-8所示。 189.

2009-10-20 09:49:27

“门”电路是什么?是门里的电路吗? 并不是哦,门电路是一种逻辑关系电路,用来实现基本的逻辑运算和符合逻辑元素的单元电路。所以像平时听见的与门,或门,非门,与非门,异或门都是门电路。 (图

2023-04-13 17:44:29

这样逻辑关系的电路叫做“异或”门。其逻辑图如图 1-6。其逻辑表达式为 其真值表为表 1-6。 7.“异或非”门(“同”门) 当两个输入端 A、 B 的状态相同时, 输出端 C 为“1” , 而当不同时, 输出

2019-12-25 17:04:35

集成逻辑电路、组合逻辑电路实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法

2008-12-11 23:36:32

单电源 2 输入异或 (XOR) 门逻辑电平转换器 Technology Family LV1T Bits (#) 1 High input voltage (Min

2022-12-12 15:22:52

4 通道、2 输入、2V 至 6V XOR(异或)门

2022-12-13 15:45:58

与非门逻辑符号

2009-04-06 01:12:18 2477

2477 与非门逻辑符号图

2009-04-06 23:13:21 42760

42760

或非门逻辑符号图

(a) 逻辑符号 &nb

2009-04-06 23:23:53 26563

26563

异或门电路

异或门和同或门的逻辑符号如下图所示。

2009-07-16 07:55:17 19882

19882

逻辑门电路符号图(与门或门非门异或门同或门)

2009-07-16 08:17:00 136737

136737

与或非门逻辑符号

2009-07-28 09:17:32 59106

59106

电子发烧友App

电子发烧友App

评论