、意法半导体(ST)、赛普拉斯(Cypress),以及戴乐格(Dialog)半导体等业者,皆竞相于今年推出蓝牙低功耗系统单芯片(SoC)解决方案,让市场竞争战火急遽升温。

2013-11-11 10:06:58 1084

1084 2019年5月25日下午,由Arm中国主办,Mentor和上海移知信息科技有限公司协办的Arm SoC芯片低功耗设计分享会在深圳成功举办,此次线下沙龙以嘉宾分享和现场互动交流为主,旨在帮助芯片设计工

2019-05-28 09:35:00 1369

1369 随着SOC越来越复杂,包含的IP越来越多,单个SOC上实现了CPU、射频模块、DDR控制模块、外设等等功能。各种功能,多种IP也带来了多档电源的需求。同时为了满足低功耗的要求,SOC通常被分为多个

2021-10-28 09:45:05

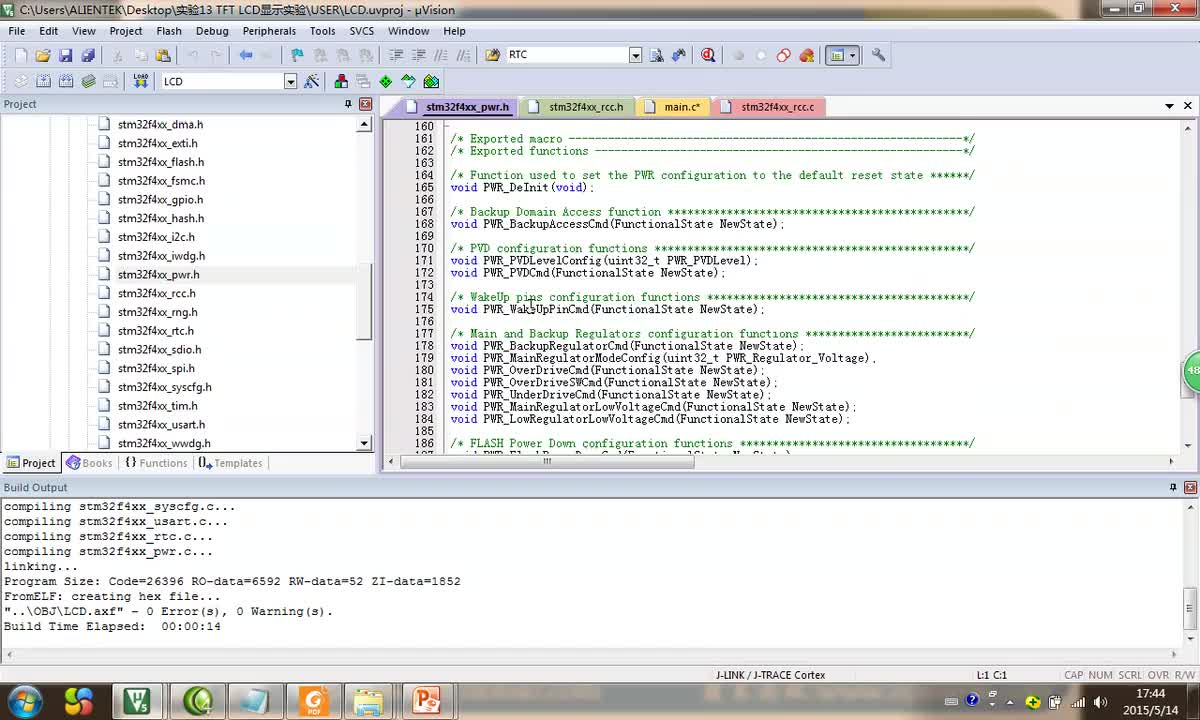

本帖最后由 gk320830 于 2015-3-8 17:16 编辑

SoC低功耗设计SoC低功耗设计

2012-08-13 16:21:38

、SoC验证技术、可测性设计技术、低功耗设计技术、超深亚微米电路实现技术,并且包含做嵌入式软件移植、开发研究,是一门跨学科的新兴研究领域

2016-05-24 19:18:54

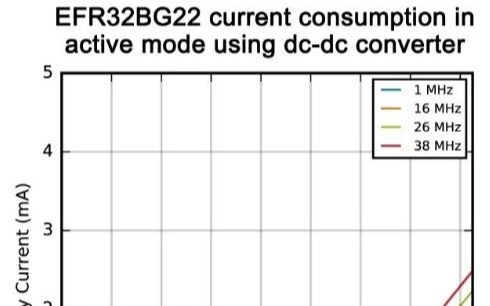

当今的系统设计人员受益于芯片系统(SoC)设计人员在芯片级功耗管理上的巨大投入。但是对于实际能耗非常小的系统,系统设计团队必须要知道,实际是怎样进行SoC功耗管理的。他们必须对整个系统进行功耗规划

2014-09-02 14:51:19

数据透传是选择低功耗WiFi模块还是低功耗蓝牙模块好?

2021-01-04 06:55:35

的设计瓶颈,也成为产品设计的关键技术之一。当然,功耗的问题本身是一个系统的问题,要想有效地降低整体功耗,不但需要在硬件上要充分考虑,而且在软件的设计上更需要认真对待。一个真正高效的低功耗系统,软硬件的相互配合和优化才是极为关键的。

2019-09-02 07:55:40

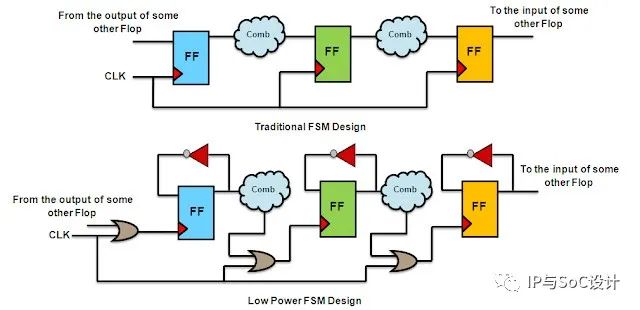

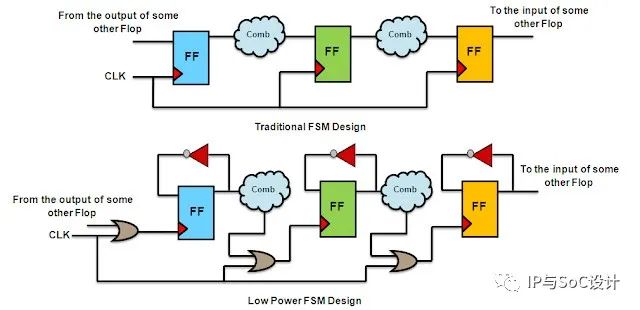

低功耗电路设计方法时钟门控技术频繁的信号翻转会造成很大的短路电流,以及对负载电容进行频繁的充放电,即增大所谓的内部功耗(InternalPower)和切换功耗(SwitchPower)。在现代

2021-07-26 06:01:33

``什么是低功耗?如何界定* 平均工作电流为 uA 级* 峰值电流不超过 15mA* 采用纽扣电池供电,电池寿命可达数年 在很多低功耗应用场景中,是采用纽扣电池来供电的,采用纽扣电池来供电是低功耗

2018-02-06 15:32:54

更加智能的家电设备,通过智能手机对小家电进行开关、预约等各种控制,给生活带来不一样的体验。智能医疗健康低功耗蓝牙为医疗保健应用提供了一个理想的解决方案。可以大规模的使用高集成、小体积、集成微处理器SOC

2019-03-18 02:25:12

如果原本的系统时钟为60MHZ,系统进入低功耗模式-睡眠模式(Sleep):主 LDO 关闭,由超低功耗 ULP-LDO 维持 PMU、内核和基本外设供电。请问这个时候,系统时钟是什么?Fsys是自动切换到32K,还是说需要提前手动切换到32K?

2022-08-15 07:37:57

程序使用定时唤醒采样方式,每隔一段时间唤醒,进行AD采样。问题在于,如果不使用内部2.5V基准电压,进入低功耗时候,电流在20uA左右;使用内部2.5V基准电压,进入低功耗前关闭(ADC12CTL0

2018-06-21 14:54:10

0.18um嵌入式闪存uLL/HDR「high data retention」制程,可协助系统单芯片(SoC)设计人员进一步降低功耗漏损,幅度可达0.18um G实作的10倍。

2019-07-22 07:00:02

`云间半导体针对智能手表推出的Clouder X SOC芯片,它内部集成了Bolt CPU内核,主频1.2G,Bolt内核是我们专门为可穿戴设备市场定制的高性能低功耗CPU。Clouder X同时也

2015-01-29 00:09:02

IC 空中完全兼容; 支持包括蓝牙低功耗、ANT 和专有 2.4GHz 等协议的非并行和并行操作; 场强RSSI。 nRF51 系列 SoC 大大地降低平均电流,使单芯片适用于各种无线应用。它

2012-07-16 13:52:16

本帖最后由 qq2355239039 于 2020-6-6 15:11 编辑

PAN1020是一款集成了射频收发器和蓝牙低功耗基带处理器的BLE SoC收发器,可以用作应用程序处理器以及完全

2020-06-06 15:08:58

RS13100无线MCU超低功耗双模SoC器件

2020-12-21 07:37:19

本帖最后由 hzeeng 于 2023-12-1 00:40 编辑

Si3262是一款高度集成的低功耗SOC芯片,其集成了基于RISC-V核的低功耗MCU和工作在13.56MHz的非接触式

2023-10-08 16:01:27

。CC2541 SoC 的推出,将进一步践行TI 为制造商提供低功耗易部署蓝牙低功耗解决方案的一贯承诺。我们的最新 CC2541 SoC 进一步丰富了 TI 全面的系统解决方案,该器件旨在简化蓝牙智能传感器

2012-03-02 16:48:33

nRF52832低功耗蓝牙(Bluetooth® low energy) (前称为蓝牙智能)系统级芯片(SoC)的晶圆级芯片尺寸封装(WL-CSP)产品,占位面积为标准封装nRF52832器件

2017-08-16 10:43:56

本书内容

选材不错

在众多的Linux技术书籍中,专门讲低功耗这一部分细分技术的书籍非常少,本书专注于该部分技术分析,从内容看是一本值得一看的书。物联网行业尤其对功耗敏感,所以本书的众多实现技术

2023-09-08 23:38:15

本帖最后由 缪靠斯兔 于 2023-10-18 12:51 编辑

花了一些时间阅读完了这本《SoC底层软件低功耗系统设计与实现》,收获良多,行业前辈的SOC底层软件的设计和调试经验,着实可贵

2023-10-18 03:27:48

余年经验总结,底层软件低功耗领域里程碑作品(2)系统剖析SoC底层软件低功耗系统的设计、实现与定制化,全面讲解低功耗的知识点以及各种低功耗问题的定位和优化

《SoC底层软件低功耗系统设计与实现

2023-07-28 11:09:40

低功耗设计是芯片设计的关键技术,本视频简要介绍了SoC芯片设计中常见的低功耗设计技术,验证难点。欢迎加入启芯QQ群:275855756。 学习芯片设计,可以参考:启芯SoC芯片设计系列课程

2013-11-03 08:44:06

爱都科技ID205可穿戴设备使用Nordic nRF52840 SoC提供处理能力和无线连接位于深圳的智能可穿戴设备开发厂商爱都科技选择使用Nordic的nRF52840低功耗蓝牙技术

2019-09-11 11:51:30

对于当今的各种电子设备尤其是嵌入式系统来说,功耗是一个非常重要的问题。系统部件产生的热量和功耗成比例,为解决散热问题而采取的冷却措施进一步增加了整个系统的功耗。为了得到最好的结果,在设计初级阶段就要尽可能地考虑低功耗问题。

2019-09-19 06:18:34

今天更新一篇数字IC低功耗设计方法总结,内容参考的是郭炜老师的书:《SoC设计方法与实现(第3版)》,希望能给大家带来帮助~

2021-07-29 06:38:58

上面的多个要求,然而现实中很难做到:同时满足高速处理、低功耗和价格?ARM高速,但是功耗而价格高; 同时满足高速处理和小封装?希望封装面积小到3×3mm,又要不牺牲速度;同时满足小封装和SOC?需要

2017-05-25 14:49:03

适合高温环境的16位、600 kSPS低功耗数据采集系统

2021-04-06 07:57:00

摘要:随着芯片集成度的提高,对一些功能复杂的系统芯片功耗的管理,已经引起大家越来越多的重视,如何控制好SoC的功耗将成为芯片能否成功的重要因素。本文提出一种通过动态管理时钟的策略,达到降低整个So...

2021-04-22 06:00:43

单片机低功耗如何减低整个系统功耗?从两个方面下手:软件? 硬件?软件:减少外设使用(不需要的就关掉),减低时钟频率,尽量选择低功耗模式。硬件:尽量使用低功耗的器件,注意电源到电阻到接地的电流,低功耗

2021-11-10 08:04:40

单片机的低功耗设计技术单片机应用系统中的低功耗设计主要注意的问题

2021-04-20 06:27:23

TISimpleLink™ CC2640R2F-Q1+TCAN4550-Q1 :在低功耗 Bluetooth® PEPS 系统中添加 CAN 节点

2021-02-04 06:10:13

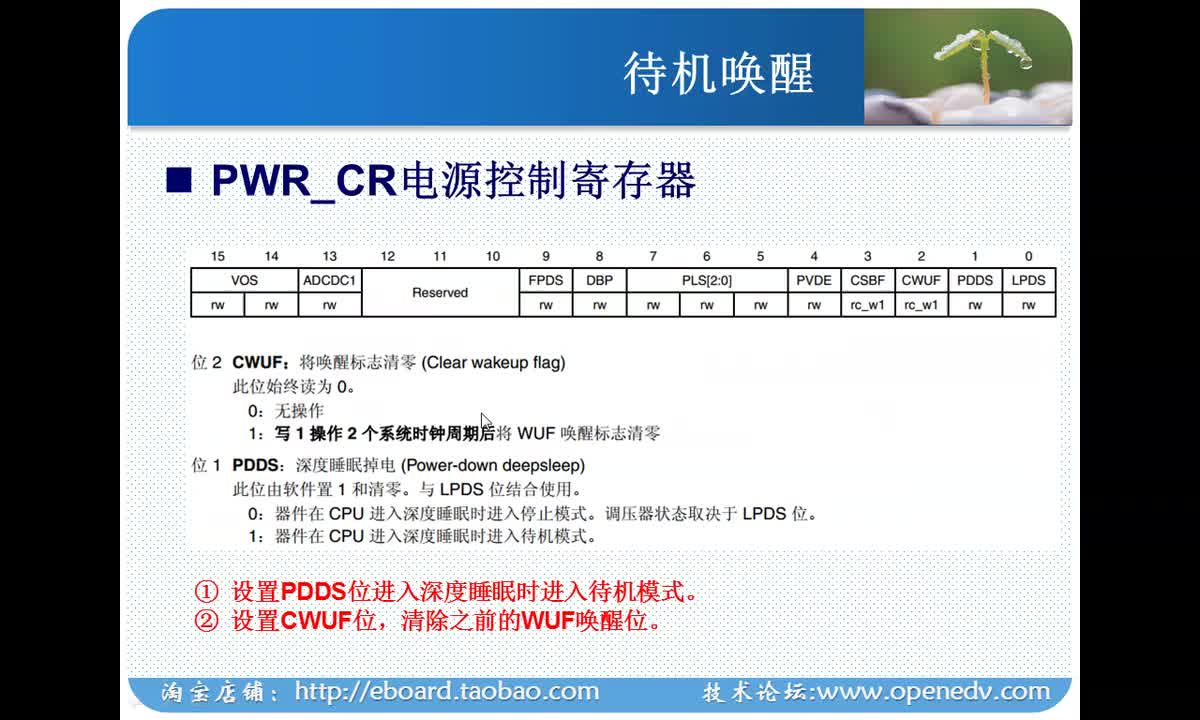

ST的低功耗有3种模式,看了参考手册发现这三种低功耗的唤醒方式都是中断和事件唤醒,裸机情况下可使用任一外部中断来唤醒。在操作系统情况下,一般会把低功耗放在空闲线程IDLE的HOOK函数中去执行,在

2020-07-24 08:01:28

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。本文将讨论减小动态和静态功耗的各种方法,并且给出一些例子说明如何使功耗最小化。

2019-07-12 06:38:08

和每立方厘米的能量不断增长。然而,物联网应用在成本和空间方面的限制更高,因此,物联网芯片系统 (SoC) 设计师不能仅依赖更昂贵或更大的电池来延长设备使用时间。本文介绍了设计师如何在低功耗工艺技术上使用Foundation IP(逻辑库和嵌入式存储器)来减少物联网设计的功耗。

2019-07-26 07:01:11

SoC。该设备的主要特点是:无线运动感应 - 电池供电的运动感应与无线数据传输低功耗蓝牙 (BLE) 连接 - 通过 BLE 通告运动事件由 CR2023 电池供电 - 电池寿命长达 10 年运

2022-08-24 07:08:17

许多物联网应用依靠小型电池运行,或者至少在一段时间内依靠收集的能量而运行,因此,这些应用在能耗方面的预算非常严格。针对物联网市场的系统系统 (SoC) 设计人员面临着独特的挑战,包括提供市场需要的日益增多的特性,以及维持应用所需的低功耗。

2019-08-12 07:33:34

选用Nordic nRF52832和nRF52810 SoC,为物联网应用提供低功耗蓝牙BLE无线连接

2021-06-15 07:08:56

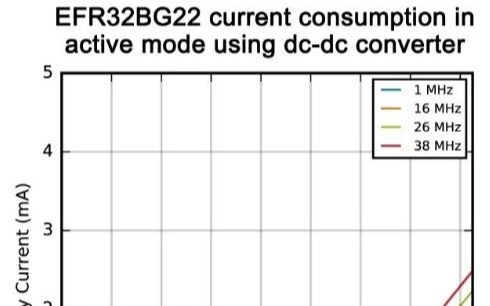

超低功耗。这4个字在半导体行业随便滥用,特别是当涉及蓝牙低功耗功能的无线电系统单芯片(SoC)。然而,根据无线电SOC的特点和目标应用的需求,声称“超低功耗”可能并不总是准确的或适用的。那么系统级

2018-10-31 09:15:37

如何去设计SoC中的低功耗RF收发器?

2021-05-25 07:04:51

通过使用通信总线进行通信。 图 1:车内的低功耗蓝牙 PEPS 架构卫星节点内部那么卫星节点内部是什么?图 2 所示为低功耗蓝牙卫星模块的典型方框图。该模块有一个低功耗蓝牙片上系统 (SoC)(如

2022-11-09 08:13:26

如何设计具备更强功能和更低功耗的片上系统?怎么实现多端口1Gbps和10Gbps TCP/iSCSI协议处理任务?

2021-05-07 07:07:34

通常说来,SoC相对于传统MCU而言能支持更多低功耗模式。其原因在于SoC集成度高,有更多片上组件和多种电源配置,以支持不同的工作需求。

2019-10-30 07:18:33

在设计初始阶段 ,如何选择正确的低功耗蓝牙SoC?

2021-03-11 06:18:48

在物联网的推动下,业界对各种电池供电设备产生了巨大需求。这反过来又使业界对微控制器和其他系统级器件的能源效率要求不断提高。因此超低功耗MCU与功耗相关的很多指标都不断得刷新记录。在选择合适的超低功耗

2020-12-28 07:12:40

超低功耗内存专家sureCore正在招聘在内存设计方面拥有10年或以上经验的工程师。其嵌入式 SRAM IP 面向服务于可穿戴和物联网 (IoT) 应用且对功耗、散热和电池寿命敏感的片上系统

2021-12-14 07:54:06

随着手机、智能穿戴、医疗电子等新兴产品的兴起,嵌入式系统的设计也成为各位软硬件工程师越来越关心的话题。 在嵌入式系统设计中,Low Power Design(低功耗设计)是许多设计人员必须面对

2014-01-21 11:22:57

目前,无线通信技术已经成为一大热点,而系统设计的微型化、低功耗成为发展的必然趋势。在保证系统工作可靠性的前提下,如何实现系统低功耗是无线数据传输系统亟待解决的一个主要问题。本文利用MSP430超低功耗

2019-08-01 07:08:45

码低功耗接收模块由天线输入匹配回路,SOC 射频片上系统,本振晶体,学习对码用LED 指示灯,学习对码用小尺寸轻触按键等几部分构成。在正常接收状态处理数据时,射频RF 处于稳态接收模式,电压范围建议

2019-02-22 18:23:05

终端节点关闭低功耗模式和开启低功耗模式,功耗有何区别?功耗相差多少?

2018-05-22 08:42:02

行业最低功耗蓝牙SoC NCV-RSL10有什么优势?会给汽车行业带来什么影响?

2019-08-05 06:16:39

,使其低于采用独立MCU和分立外设的情况。本系列文章共分三部分,在第二部分中,我们将介绍SoC以及如何提高其效率,从而有利于系统设计,降低功耗。

2016-07-29 15:25:00

硬件低功耗设计软件部分的设计基于μC/OS-II内核扩展接口的低功耗模式FM电台手持式测试仪的低功耗设计

2021-04-26 06:29:29

stm32进入低功耗模式,必须用中断来唤醒,现在就是不用这种模式,如何通过程序来降低功耗啊

2019-05-06 18:43:22

翱捷科技(以下简称ASR)正式发布国内首款、采用超低功耗LoRa集成的单芯片SoC - ASR6501。该芯片集成低功耗LoRa Transceiver和低功耗MCU,超小尺寸,超低功耗,集成

2021-09-30 11:26:30

的厚度减小)。 今天,我们已经拥有在单芯片上实现完整系统/子系统高度集成的SoC。除了集成度之外,就功耗而言,这些SoC也有助于降低平均功耗,使其低于采用独立MCU和分立外设的情况。 本系列文章共分三部分,在第二部分中,我们将介绍SoC以及如何提高其效率,从而有利于系统设计,降低功耗。

2020-08-20 12:30:00

GW8811系列低功耗蓝牙4.2 SoC,基于32位ARM® Cortex®-M0处理器,工作主频64MHz, Flash 512KB , SRAM 24/32KB;集成高性能

2020-11-04 16:07:23

在系统设计中,低功耗系统或低功耗协同设计系统并没有作为一个整体在当前的研究中得到充分的重视。本文阐述在系统级设计中功耗的重要性,综述硬件低功耗、软件低功耗和通

2009-05-15 14:29:50 12

12 功耗问题正日益变成VLSI 系统实现的一个限制因素。对便携式应用来说,其主要原因在于电池寿命,对固定应用则在于最高工作温度。由于电子系统设计的复杂度在日益提高,导致系

2009-05-16 13:23:55 14

14 本文描述了SOC平台体系结构之低功耗高性能的数字信号处理的应用。这个平台是基于AMBA SOC总线协议,它结合了新颖的互连规范,为了能让高性能的DSP IP核集成到SOC平台中,这个规范

2010-02-01 13:58:40 14

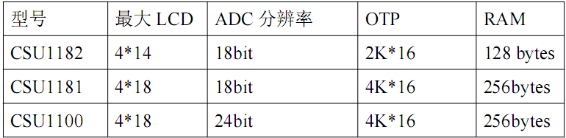

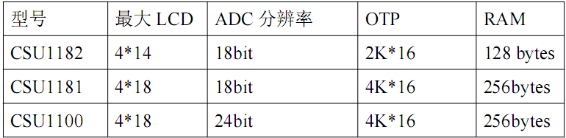

14 芯海科技最新推出CSU11xx系列超低功耗衡器SoC芯片

芯海科技最新推出CSU11xx系列超低功耗衡器SoC芯片,可用于降低电子衡器、精密测量及控制系统的待机功耗与工作功耗

2010-02-16 15:29:33 1000

1000

芯海科技开发出低功耗SoC衡器计量芯片

深圳芯海科技公司近日宣布推出低功耗SoC衡器计量芯片CSU11xx系列,包括CSU1182、CSU1181、及CSU1100三款产品。可降低电子

2010-02-22 10:10:26 1059

1059 德州仪器 (TI) 宣布推出其最新 CC2541 蓝牙 (Bluetooth®) 低功耗片上系统 (SoC),以充分满足消费类医疗、运动健身、安全、娱乐以及家庭自动化对蓝牙智能传感器的应用需求。

2012-01-18 08:53:37 2173

2173 nRF51822 是功能强大、高灵活性的多协议 SoC,非常适用于 Bluetooth® 低功耗和 2.4GHz 超低功耗无线应用。

2014-01-23 15:02:07 9173

9173

低功耗单片微机系统设计

2017-09-22 09:21:32 7

7 在芬兰举行的国际SoC会议上,Catena Radio Design公司的CTO Kianush做了主题演讲:SoC中低功耗RF收发器的设计策略,它涉及到当前的一个问题即高度集成对数字电路来讲很有

2017-11-24 07:18:40 232

232 在芬兰举行的国际SoC会议上,Catena Radio Design公司的CTO Kianush做了主题演讲:SoC中低功耗RF收发器的设计策略,它涉及到当前的一个问题即高度集成对数字电路来讲很有

2017-12-07 18:44:11 191

191 在芬兰举行的国际SoC会议上,Catena Radio Design公司的CTO Kianush做了主题演讲:SoC中低功耗RF收发器的设计策略,它涉及到当前的一个问题即高度集成对数字电路来讲很有

2018-05-24 10:32:00 1403

1403 芯片,已不能再只考虑它优化空间的两个方面速度( pe r fo rrnance)和面积(cOst),而必须要注意它已经表现出来的且变得越来越重要的第三个方面功耗,这样才能延长电池的寿命和电子产品的运行时间。 SoC中CMOS电路功耗有:一是静态功耗,主要是由静电流、漏电流

2018-02-06 11:27:40 1

1 面向便携式设备的SoC设计,不仅仅要求性能高、体积小,更要求功耗低。一般而言,SoC的静态功耗很小,而对负载电容充放电的动态功耗很大。 SoC内部,总线上挂着很多功能设备,导致总线的电容负载很大

2018-02-07 14:29:09 1

1 在CES 2018盛会上面,高通宣布推出全新的低功耗蓝牙系统级芯片(SoC)QCC5100系列,这套方案能够帮助紧凑无线耳机、蓝牙耳机、蓝牙头戴耳机增加续航表现,提升整体的使用体验。

2018-02-12 17:19:33 1602

1602 ST公司的BlueNRG-1是非常低功耗的蓝牙低功耗(BLE)单模式系统级芯片(SoC),包括有160KB可编程闪存,24KB静态RAM存储器,以及SPI,UART,I2C标准通信接口,多功能定时器

2018-04-22 13:13:00 11234

11234

该C1110FX/C1111FX是一个真正的低功耗子- 1 GHz的片上系统(SOC)设计的低功耗无线应用。该C1110FX/C1111FX结合了先进的射频收发器cc110与业界标准增强型8051

2018-08-08 17:29:36 5

5 cc2541是一种功耗优化的真正的片上系统(SOC)解决方案,用于蓝牙低功耗和专有的2.4-GHz应用。它使Brand网络节点能够以较低的总BIOFF材料成本来构建。cc2541结合了先进的射频

2018-10-22 08:00:00 15

15 许可,在其nRF91系统级芯片(SoC)中部署使用CEVA DSP技术以实现低功耗蜂窝物联网连接。这个多模LTE-M/NB-IoT SoC通过位于核心的CEVA DSP来确保实现所需的超低功耗和高效

2019-01-07 09:05:01 304

304 0V7725,设计并实现了一款基于开源RISC V指令集架构SoC芯片的图像采集控制系统。文中介绍了图像采集控制系统的结构,并详细阐述基于AHB总线的图像采集控制器的设计控制器采用一种改进的异步FIFO来实现不同时钟城的同步设计,具有小面积和低功耗的特点通过Modelsim仿真、DC综合以及FPGA验证

2019-09-24 08:00:00 0

0 物联网产品高级营销总监Emmanuel Sambuis特别制作一篇技术应用文章,说明如何为您的产品设计选用正确的低功耗蓝牙SoC。 优化Bluetooth LE应用以实现最小能耗运行是一项挑战。了解

2020-10-23 14:27:08 4358

4358

低功耗电路设计方法时钟门控技术频繁的信号翻转会造成很大的短路电流,以及对负载电容进行频繁的充放电,即增大所谓的内部功耗(InternalPower)和切换功耗(SwitchPower)。在现代

2021-10-22 16:51:04 1

1 都导通时所引起的功耗。低功耗设计方法对于系统是在低功耗下提高性能,还是高性能下降低功耗,这对采样什么样的低功耗技术很关键。下图是基于低功耗反馈的前向设计法,如图,可以看出五个层次下对系统的功耗进行优化,自顶向下分别对应系统级、行为级、RTL级、逻辑级和物理级。下图说明了各层次的具体优化方法和优化效果,可以看到层次

2021-11-06 15:51:01 18

18 英尚微简单介绍EB5REB1低功耗蓝牙SOC芯片(BLE5.0)的片上系统,并为客户提供足够多的能将SOC集成到产品中的信息。 伟凌创芯EB5REB1是一款符合蓝牙5.0规范的,完全集成的低功耗

2023-07-25 15:34:26 610

610 瑞萨DA16200超低功耗Wifi Soc产品简介

2023-10-10 17:59:58 0

0 低功耗设计是当下的需要!这篇文章:低功耗设计方法论的必要性让我们深入了解了现代设计的意图和对功耗感知的需求。在低功耗方法标签下的时钟门控和电源门控的后续文章中,讨论了一些SoC低功耗设计的方法。在这篇文章中,我们将考虑一个这样的低功耗设计的FSM,可以推广到任何低功耗时序电路的设计。

2023-10-17 10:41:13 309

309

全芯片UPF低功耗设计(含DFT设计)

2023-12-29 11:43:50 243

243

全球半导体解决方案供应商瑞萨电子近日宣布推出新款低功耗蓝牙(LE)片上系统(SoC),即DA14592。这款产品凭借其超低功耗和微型尺寸,成为瑞萨电子系列中功耗最低、体积最小的多核(Cortex-M33、Cortex-M0+)低功耗蓝牙产品。

2024-01-19 16:18:15 322

322 全球半导体解决方案供应商瑞萨电子(TSE:6723)今日宣布推出DA14592低功耗蓝牙(LE)片上系统(SoC),成为瑞萨功耗最低、体积最小的多核(Cortex-M33、Cortex-M0+

2024-01-19 16:37:30 586

586

正在加载...

电子发烧友App

电子发烧友App

评论