程序存储器当EA引脚接高电平时,CPU将使用内部程序存储器,若程序超过内部程序存储器空间时,则CPU会自动从外部程序存储器重读取超过部分的程序代码。 数据存储器51的程序存储器和数据存储器是独立分开

2018-07-19 03:19:33

毕设题目 :75mhz双路时钟缓冲器,求助

2021-02-27 21:45:00

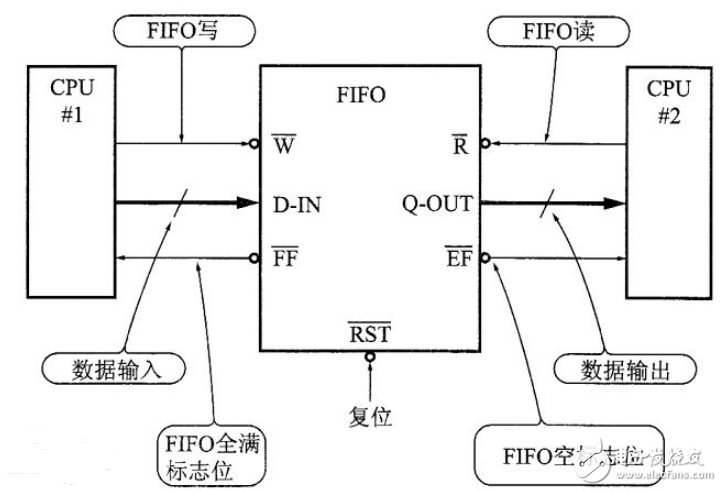

FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;2)数据集中起来进行进栈和存储,可

2022-01-18 10:03:06

存储器扩展方式是什么?IO扩展方式是什么?

2022-01-17 08:24:15

存储器接口生成器(MIG)解决方案---Virtex-4 存储器接口和Virtex-II Pro存储器解决方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

存储器映射是什么意思?其映射过程是怎样的?

2022-01-21 07:39:51

感谢Dryiceboy的投递据市场分析数据,DRAM和NAND存储器价格近期正在不断上扬.许多人认为当前存储器市场的涨价只不过是暂时的供需不稳所导致的;有些人则认为随着存储器价格3D NAND制造

2019-07-16 08:50:19

存储器的分类存储器是计算机系统中的记忆设备,用来存放程序和数据,从不同的角度对存储器可以做不同的分类。1、按存储介质分半导体存储器(又称易失性存储器):体积小,功耗低,存取时间短,电源消失的时候,所存的信息也随之消失。磁表面存储器(...

2021-07-26 08:30:22

帧存储器AL440B具有什么特点?AL440B的典型应用是什么?

2021-06-04 06:19:17

单端模式下,AD7328模拟输入端是不是必须加缓冲器,缓冲器选什么型号

2023-12-06 06:52:14

描述ADC缓冲器/混频器

2022-06-29 06:14:05

加起来肯定是填不满的。一般来说, 0X00000000依次开始存放FLASH——0X00000000,SRAM——0X40000000,BOOTBLOCK,外部存储器 0X80000000,VPB(低速

2014-03-24 11:57:18

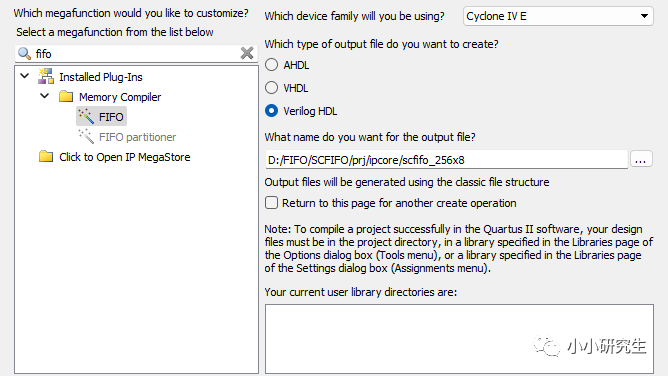

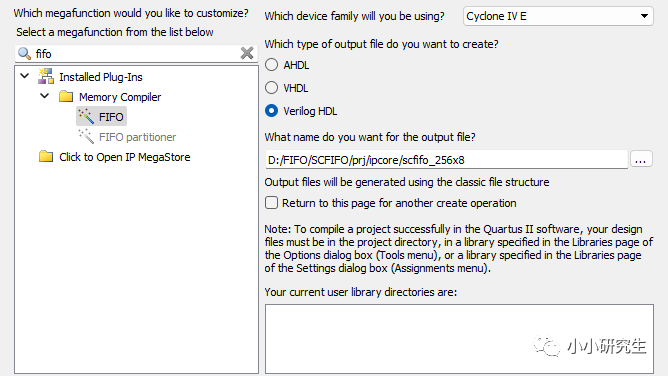

Cyclone® IV 器件具有嵌入式存储器结构,满足了 Altera® Cyclone IV 器件设计对片上存储器的需求。嵌入式存储器结构由一列列 M9K 存储器模块组成,通过对这些 M9K 存储器模块进行配置,可以实现各种存储器功能,例如:RAM、移位寄存器、 ROM 以及FIFO 缓冲器。

2017-11-13 12:09:48

:视频处理器框图FPGA获取并缓存四个视频源的数据流。这些FIFO缓冲器由DDR3存储器控制器清空并保存在DDR3存储器中。一旦一个完整的视频数据包存储完毕,视频处理器会向DDR3存储器控制器申请数据

2019-05-24 05:00:34

(SLRD)读取不活跃,则缓冲器将是满的,并且不能写入更多的数据。一旦从奴隶FIFO开始读取,缓冲器将干净并准备好下一次传输。我的理解正确吗?我还想用I2S传送短命令到FPGA,但是我找不到这样的固件例子

2019-04-29 07:36:44

问题一:位图都存储在哪了?都在程序存储器里吗问题二:能不能将位图存储到外部内存中?问题三:F429的程序存储器和数据存储器有多大?

2020-05-20 04:37:13

Flash存储器分为哪几类?Flash存储器有什么特点?Flash与DRAM有什么区别?

2021-06-18 07:03:45

完全正交的状态;而且在 XMC 预取缓冲器后可提供判优以对 CorePacs 隐藏存储器组之间的冲突。 此外,XMC 还为数据和程序预取嵌入了多流预取缓冲器。程序预取缓冲器可为来自 L1P 和 L2

2011-08-13 15:45:42

当系统运行了一个嵌入式实时操作系统时(RTOS),操作系统通常都是使用非易失的存储器来运行软件以及采集数据。存储器的选择面很广阔,其中包括电池供电的SRAM(静态随机访问储存器),各种各样的闪存以及串口EEPROM(电可擦的,可编程的只读存储器)。

2019-06-28 08:29:29

1.地址缓冲器在提供给存储器的sa0~sa15地址中加人缓冲器。缓冲器利用74ls244也可以,但因为741ls245布线比较简单,所以才通过74ls245可单向使用。 2.数据缓冲器因为数据

2020-12-10 16:44:18

从三个层面认识SRAM存储器

2021-01-05 07:09:10

中。一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。可访问的存储器空间被分成8个主要块,每个块为512MB。其他所有没有分配给片上存储器和外设的存储器空间都是保留的地址空间。1. FLASHFlash主存储区从0x0800 0000地址开始,不同系列器件有不同大小,这里

2021-08-02 06:06:32

为什么有的电子设备用eMMC存储器 ?而有的用DDR存储器呢?这两者有什么区别吗?

2021-06-18 06:13:25

题目是一个停车场计时系统,用74系列之类的芯片。我们用6116存储器来存地址信号,通过刷卡产生脉冲,经过延时出现两个相邻的脉冲分别代表读和写信号,用来读取存储器中对应车的状态(在不在车库内),再将

2016-07-23 00:01:59

stm32不是有暂存功能吗 为啥做示波器还要接个FIFO存储器。不加行不

2017-12-04 11:12:51

计算机指令以及处理计算机软件中的数据。中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Dat...

2022-02-10 08:00:15

寄存器来实现的。以上的程序中 USART_RX_BUF[t]在USART.C中定义的是一个接收缓冲器,在这里怎么变成了发送缓冲器?再定义一个发送缓冲器USART_TX_BUF[t]不是更好?

2019-07-16 03:32:02

什么是EEPROM存储器?

2021-11-01 07:24:44

`请问什么是音频缓冲器?`

2019-08-23 16:27:28

代码是从哪里开始运行的?从存储器哪一个位置开始读取代码呢?

2021-10-21 09:11:37

的认为就是一条整齐划一的“队列”,操作起来就是一个挨着一个,并且井然有序。FIFO存储器的机理虽然简单,但是作用却异常强大,在多芯片数据交换传输的应用中,往往都会让FIFO存储器来做承前启后的“缓冲器”。 图10.5 FIFO工作原理图示意图

2016-12-23 17:48:03

高速、低功耗数据缓冲器为DDR5 DRAM及存储类内存模块提升速度与带宽

2020-11-24 06:58:15

描述吉他缓冲器Guitar Buffer消除了长吉他电缆造成的信号损失,这是任何踏板的必备品。

2022-07-26 07:14:58

:视频处理器框图FPGA获取并缓存四个视频源的数据流。这些FIFO缓冲器由DDR3存储器控制器清空并保存在DDR3存储器中。一旦一个完整的视频数据包存储完毕,视频处理器会向DDR3存储器控制器申请数据

2019-05-27 05:00:02

,通常可以使用的存储器有片上存储器和片外存储器,其中前者指的是FPGA内嵌的存储器,如片上RAM、FIFO、紧耦合存储器等;后者为FPGA片外存储器,如SRAM、SDRAM等。本文介绍了将片内存储器

2018-12-07 10:27:46

描述ATtiny2313 USBtinyISP DIP基于ladyada设计的带缓冲器的AVR ISP。PCB+展示

2022-08-19 06:45:50

如何利用Xilinx FPGA和存储器接口生成器简化存储器接口?

2021-05-06 07:23:59

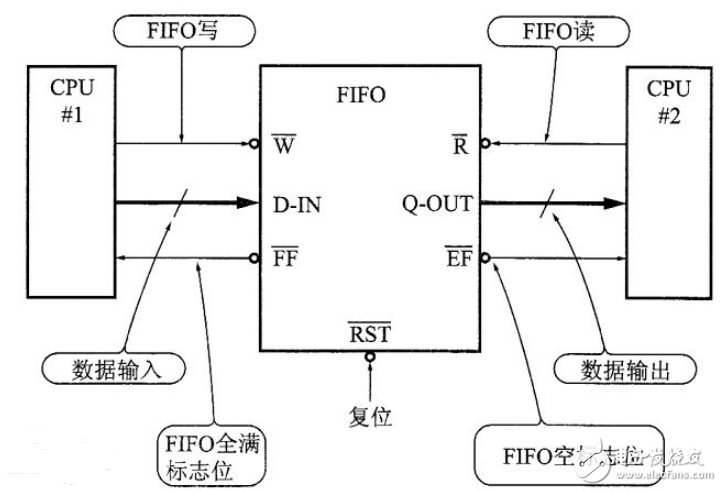

CPU之间怎么进行通信?FIFO的工作原理是什么?如何利用多端口存储器设计多机系统?

2021-05-26 07:04:50

如何去设计MP3播放器视频的输出部分?如何去解决超低功耗缓冲器应用的问题?

2021-04-20 06:02:33

如何去设计轨到轨CMOS模拟缓冲器?怎样对轨到轨CMOS模拟缓冲器进行仿真?

2021-04-23 06:35:57

?我可以只使用内部存储器来存储帧缓冲区,而不是外部存储器,如 QSPI 、带 FMC 的 SDRAM 吗?如果有人对此有任何想法,请帮助我解决这个问题。

2022-12-06 07:24:53

如何实现扩展存储器的设计?

2021-10-28 08:08:51

中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304 扇出缓冲器就是一个很好的例子

2022-11-21 07:25:28

。优势是显而易见的。由于BJT具有较高的电压额定值,泄露尖峰会高出几百伏特,不过仍然处于所要求的开关降额设计范围内。根据尖峰的幅度不同,常常有可能在不使开关过压的情况下完全移除缓冲器。移除缓冲器优点

2022-11-17 07:51:39

能否让低压放大器自举来获得高压缓冲器?

2021-03-16 14:31:58

大家好,我试图使用逻辑分配文件(* .ll)找到一些FF位。我通过ICAP读取配置存储器并将读取帧存储在外部RAM中。我注意到的是,bitset与我的回读中改变的位不匹配。1)我读了1列,其中我有一

2020-06-17 15:25:55

影响存储器访问性能的因素有哪些?DSP核访问内部存储器和外部DDR存储器的时延有什么不同?

2021-04-19 08:32:10

STM32的存储器由哪些组成?怎样去启动STM32存储器?

2021-09-24 07:03:23

怎样去降低H.264 INTRA帧编码的运算复杂性和存储器需求?

2021-04-21 07:17:16

存储器可分为哪几类?存储器有哪些特点?存储器有哪些功能?

2021-10-20 06:46:21

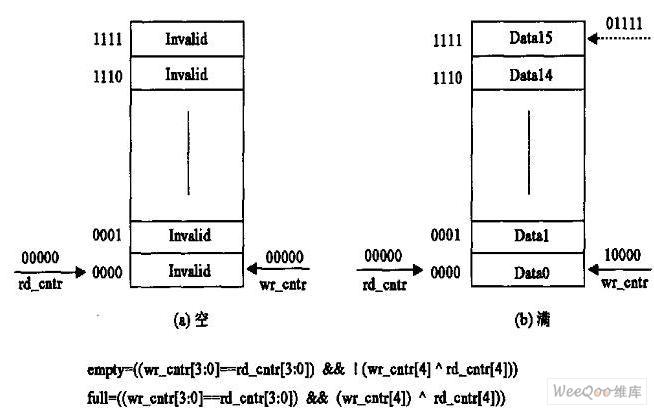

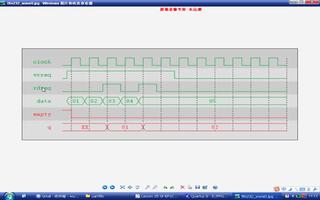

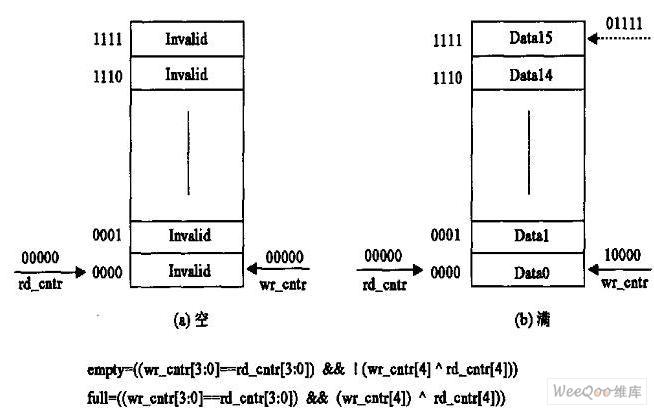

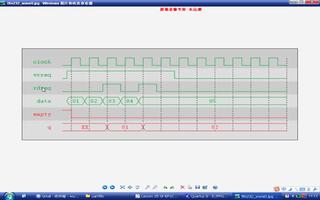

本32X8 FIFO的设计,采用了双体存储器的交替读写机制,使得在对其中一个存储器写操作的同时可以对另一个存储器进行读操作;对其中一个存储器读操作的同时可以对另一个存储器进行写操作。实现了高速数据缓冲,速度比单体存储器的FIFO提高了一倍。

2021-04-26 06:54:22

数据存储器 FLASH程序存储器 FLASH数据存储器 片内RAM数据存储器16M字节外部数据存储器各有什么区别?特点?小弟看到这段 很晕。ADuC812的用户数据存储器包含三部分,片内640字节的FLASH数据存储器、256字节的RAM以及片外可扩展到16M字节的数据存储器。求助高手。解释一下不同。

2011-11-29 09:50:46

求助:数据存储器6116和程序存储器2817怎么搜,在altium designer。貌似不太会用搜索功能。我总是搜不出来不知道为什么,求解答。单片机存储电路里的数据存储器6116和程序存储器

2014-07-22 23:10:03

测量扇出缓冲器中的附加抖动怎么计算?

2021-05-06 07:02:23

解码器需要一个恒速的传输流)。虽然存储器对同步的要求似乎很小,但当涉及到多个码流时它可能很显著。这种同步可以由一个异步FIFO实现。 2) 帧存储: 帧存储在这些地方需要:任何暂时的处理如帧率转换

2011-07-15 09:18:00

单片机中数据存储器片内的地址是00--7FH,程序存储器的片内地址是0000H--0FFFH,请问这两部分是不是有重叠?请具体详解!~{:1:}

2013-01-15 09:01:22

美国ACE小型缓冲器产品分类SC?25 至 SC?190SC?25 至 SC?190上海就瑞机械设备有限公司 销售电话021-56467099*** (微信同号) 刘小姐,QQ2411315092

2018-04-21 17:11:16

你好,我通过我的硬件流一些二进制数据,我想使最新的1000位可用的CPU在任何时间点按需。我想通过DMA不断填充缓冲来实现这一点。因此,我想要一个循环缓冲器或一个能够保持至少1000位的FIFO缓冲器(UIT8BUF(128)),是否可以在硬件中实现?有什么建议吗?

2019-09-11 12:58:18

把信号经过两级放大之后,我要使用ths3201作为缓冲器,那这个缓冲器的作用是什么,如果是为了稳定增益的话,是不是应该把增益设置成0?

2015-08-18 10:56:49

经灵敏放大器后到输出缓冲器中,就完成了读出操作的全过程。显然图1.3 的关键路径就充分反映了这个过程。图1.4 给出了SRAM存储器的读写时序。在读出操作中,访问时间(access time)就是指从

2022-11-17 16:58:07

很多大牛人见过不同的缓冲器,基于比较器的缓冲器,外部带有阻性纠错电路,它能增强高增益放大器的驱动能力,可以驱动像ADC前端电路中使用的开关电容负载。这种纠错机制使用了一个电阻,该电阻与充电路径和纠错

2021-04-02 07:32:16

嗨,当我们在FIFO或GPIF FIFO中讨论FIFO时,FIFO是终结点缓冲器吗?也就是说,如果使用奴隶FIFO,当外部CPU将一个字节写入从属FIFO时,CPU直接将字节写入端点缓冲器中,或者

2019-07-08 11:13:26

我想在一项应用中使用ad8221 ad8221,目的是放大接收自2个电极的不同电位。为消除高频噪声,我在仪表放大器输入前使用了一个RC滤波器,您认为在滤波器和放大器输入之间使用一个电压缓冲器是否会更好。在此情况下,您建议使用哪种模拟器件IC作为电压缓冲器。

2023-11-24 07:19:57

为了减少VDMA调用的数量,我需要一个更大的帧缓冲32.我想扩展它,但我没有找到任何源文档或验证测试平台。有人可以推荐一种方法吗?我还考虑过使用AXI DMA。使用分辨率,我可以缓冲超过32帧,但仍然不够。感谢您的支持!

2020-04-27 08:05:13

与传统的时钟缓冲器相比,高速运算放大器有哪些优势?怎样去设计一个灵活的时钟缓冲器?

2021-04-14 06:35:37

大电流缓冲器

2019-10-31 09:11:09

`请问高速缓冲器是什么?`

2019-08-23 16:32:59

缓冲器,缓冲器是什么?

buffer 中文译名: 缓冲,缓冲器,缓冲液 解释:1、 电信设备。在数据传输中,用来弥补不同数据处

2010-03-08 13:30:11 2253

2253 缓冲器,缓冲器基本原理是什么?

最基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输

2011-09-03 19:10:46 9257

9257 赛普拉斯半导体公司日前宣布推出一款容量高达 72 Mbit 的先进先出 (FIFO) 存储器。该款全新的高容量 (HD) FIFO 是视频及成像应用的理想选择,可满足高效缓冲所需的高容量和高频率要求

2011-06-17 09:42:02 2396

2396 ADI数字加速度计中先进先出(FIFO)缓冲器的使用

2011-11-28 15:08:27 0

0 三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器

2015-11-16 11:59:30 0

0 数字信号处理软件中循环程序在执行时间上占有很大比例,用指令缓冲器暂存循环代码可以减少程序存储器的访问次数,提高处理器性能。在VLIW处理器指令流水线中增加一个支持循环指令的缓冲器,该缓冲器能够缓存

2018-02-02 17:29:29 0

0 本文开始介绍了缓冲器和集成电路的概念,其次阐述了集成电路在各方面的应用,最后对接口集成电路中的缓冲器和集成电路中缓冲器的作用进行了介绍。

2018-03-26 14:12:08 24269

24269 本文主要介绍了fifo存储器芯片型号有哪些?FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作

2018-04-08 16:11:32 23894

23894

本32X8 FIFO的设计,采用了双体存储器的交替读写机制,使得在对其中一个存储器写操作的同时可以对另一个存储器进行读操作;对其中一个存储器读操作的同时可以对另一个存储器进行写操作。实现了高速数据缓冲,速度比单体存储器的FIFO提高了一倍。

2018-12-30 10:29:00 3218

3218

FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个是存储器的输入口,另一个口是存储器的输出口。对于单片FIFO来说,主要有两种结构:触发导向结构和零导向传输结构

2019-12-19 07:01:00 2047

2047

本文档的主要内容详细介绍的是FIFO存储器的尺寸图免费下载。

2019-08-15 08:00:00 2

2 缓冲器分为输入缓冲器和输出缓冲器两种;输入缓冲器的作用是将外设送来的数据暂时存放,以便处理器将它取走,输出缓冲器的作用是用来暂时存放处理器送往外设的数据。 缓冲器的工作原理: 当液压缓冲器受到

2021-08-25 17:31:25 22727

22727 液压缓冲器强度是否能够调节,取决于液压缓冲器的种类,目前市面上较为常用的液压缓冲器包括可调液压缓冲器、不可调液压缓冲器,这两种缓冲器调节强度的实际效果是不一样的。

2023-04-24 16:12:01 2158

2158 FIFO(First In First Out, 先入先出 ),是一种数据缓冲器,用来实现数据先入先出的读写方式。数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线,有一个写端口和一个读端口。

2023-09-07 18:30:11 820

820

正在加载...

电子发烧友App

电子发烧友App

评论