采用FPGA实现四阶IIR数字滤波器,通过两个二阶节级联构成数字椭圆低通滤波器。通带内波纹小于0.1dB,阻带衰减大于32dB。

2014-12-23 10:27:57 1673

1673

Molex 宣布收购 BittWare, Inc.,后者是一家全球领先的计算系统的提供商,专业提供现场可编程门阵列 (FPGA),产品可部署在数据中心的计算应用以及网络数据包的处理应用中。

2018-05-29 10:29:03 6949

6949 嗨,我使用的是virtex 5 FPGA。我正在运行外部10Mhz时钟信号来运行二进制计数器。当我尝试使用DCM时,它表示最低频率为32MHz。可以将此信号运行到FPGA的i / o输入并通过全局

2019-02-21 10:32:51

自行设计,所以对于后续开发 本店也会可与大力的支持与帮助。 目前小店只有6排针 (4i/o口) 不过马上即将 4排针(2i/o口)支持I2C 通信的OLED 就会在本店上架,价格和之前是一样

2013-11-04 19:37:36

的方法是扩展一片8251 或 8250 通用同步/异步接收发送芯片(USART),需额外占用单片机I/O 资源。本文介绍一种用单片机普通I/O 口实现串行通信的方法,可在单片机的最小应用系统中实现与两个

2012-06-07 15:17:42

莱迪思半导体公司CPU 、ASIC和存储器的设计者为了使器件拥有尽可能高的通信带宽,他们在设计过程中充分利用I/O单元中的每一个晶体管来达到这个目标。这些器件常与FPGA相连接。因此,FPGA

2018-11-26 11:17:24

本帖最后由 eehome 于 2013-1-5 09:57 编辑

FPGA实现I2C总线的通信接口的基本原理介绍采用ALTERA公司的可编程器件,实现I2C总线的通信接口的基本原理;给出部分

2012-08-11 17:57:48

新人求助,FPGA如何采用I2S与ARM通信?

2016-06-13 11:24:12

并行处理的方式被普遍采用,它们共享总线以互相映射存储空间,如果再与FPGA通过总线连接,势必导致FPGA与DSP的总线竞争。同时采用总线方式与FPGA通信,DSP的地址、数据线引脚很多,占用FPGA的I

2018-12-04 10:39:29

并行处理的方式被普遍采用,它们共享总线以互相映射存储空间,如果再与FPGA通过总线连接,势必导致FPGA与DSP的总线竞争。同时采用总线方式与FPGA通信,DSP的地址、数据线引脚很多,占用FPGA的I

2019-06-19 05:00:08

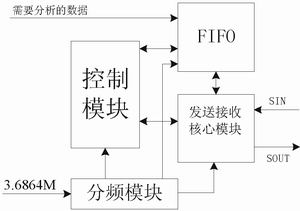

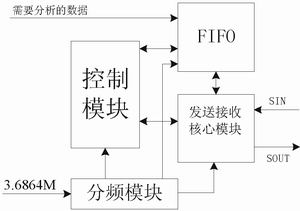

他CPU系统之间的数据通信提到日程上,得到人们的急切关注。本文介绍利用VHDL语言实现 FPGA与单片机的串口异步通信电路。整个设计采用模块化的设计思想,可分为四个模块:FPGA数据发送模块,FPGA

2011-11-24 16:10:01

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA I/O结构中没有包含均衡功能,那么它与DDR3

2019-04-22 07:00:08

。(4)从串模式理解了从并模式,从串模式就不用很多解释了,它的特点就是节约FPGA管脚I/O。(5)多片级联多片模式有两种,一种是采用菊花链的思想,多片FPGA共享一个存储器,另外一个是可以使用其他存储器

2017-11-22 09:35:19

,输入和输出。它实现了用户逻辑。互连提供逻辑块之间的方向以实现用户逻辑。根据逻辑,开关矩阵提供互连之间的切换。用于外部世界的I / O垫与不同的应用程序通信。逻辑块包含 MUX(多路复用器),D触发器

2018-12-14 17:39:44

外设电路(I/O应用)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCttFPGA器件拥有着丰富的I/O资源,它

2019-04-12 06:35:33

FPGA的I/O结构的发展的怎么样了?

2021-04-29 06:12:52

行,速度快。Xilinx Spartan-7 FPGA器件适用于那些成本敏感型应用。它采用小型封装却拥有高比例的I/O数量,单位功耗性价比相较前代产品提升多达四倍,可提供灵活的连接能力、接口桥接和辅助芯片

2018-08-02 09:37:08

这里写目录标题I/O端口原理单片机知识点补充实战1——闪烁LED指示灯I/O端口原理I/O英文全称是 Input/Output,即输入/输出。单片机端口是标准双向口,就是说,单片机的端口既可以

2022-01-20 07:55:51

` 本帖最后由 eehome 于 2013-1-5 09:57 编辑

概述:C2000 MD88为8路干接点数字量输入和8路数字量输出设备.可以通过RS485实现对远程开关量数据的采集.通信

2012-06-13 16:17:09

如下优越性:(1)高性能ACEX 1K器件采用查找表(LUT)和EAB(嵌入式阵列块)相结合的结构形式,可实现复杂逻辑功能和存储器功能,如通信应用中的DSP、多通道数据处理、数据传递和微控制等。(2

2019-06-18 06:05:34

1. 为什么要使用FPGA实现在全控型电力电子开关器件出现以后,为了改善交流电动机变压变频调速系统的性能,科技工作者在20世纪80年代开发出了应用脉宽调制(PWM)技术的变压变频器,由于它的优良

2022-01-20 09:34:26

CAS。我们的设计(图1)采用Altera公司Cyclone III系列型号为EP3C16F484C6N的FPGA作为控制器,以Micron公司生产的型号为MT47H16M16BG-5E(16M

2019-05-31 05:00:05

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-22 07:00:07

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-26 07:00:12

使用LabVIEW FPGA 模块和可重新配置I/O 设备开发测量与控制应用通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将

2009-07-23 08:15:57

效地减小磁性辐射。数据传送解决方案LpLVDS和CTL只提供针对LCD、相机成像器以及基带处理器之间接口的I/O解决方案。只有在采用某些并行至串行数据传送方案时,两者才能发挥其强大功能。借着锁相环路

2019-05-27 05:00:06

使用增强FEC(EFEC),必须采用专用算法进行设计才能确保最大限度的发挥光带宽优势。由于其优异的架构性能,StratixIVFPGA能够处理EFEC功能,是OTN系统算法实现和测试的理想平台。图6显示了

2011-07-13 14:36:03

MSP连接到同一存储区的用户I / O引脚。由于某种原因,与ADC的数字化数据引脚接口的FPGA的一些用户I / O引脚被损坏。我们已经生产了6块FPGA板,所有这些板都在相同的引脚上出现问题。我已经

2020-04-07 12:26:15

嗨, 我想把晶体振荡器的CLK带到FPGA里面的数字设计。该CLK连接到FPGA的I / O引脚。如果我在映射中运行Impliment设计,我将得到错误。所以我将在UCF文件中将网名命名如下。NET

2019-01-29 10:05:43

大家好,我现在在画一块28335的板子,想实现与FPGA之间的通信,但是不知道该怎样设计,包括FPGA与DSP连接的引脚、通过内部什么模块实现数据通信,现在一头雾水,请大家帮忙。谢谢。

2018-12-03 15:55:34

I/O接口的功能是负责实现CPU通过系统总线把I/O电路和外围设备联系在一起,按照电路和设备的复杂程度,I/O接口的硬件主要分为两大类: (1)I/O接口芯片 这些芯片大都是集成电路,通过CPU输入

2015-11-04 11:39:47

测温度用符号扩展的16位数字量方式串行输出。一线式(1-WIRE)串行总线是利用1条信号线就可以与总线上若干器件进行通信。具体应用中可以利用微处理器的I/O端口对DS18B20直接进行通信,也可以通过

2020-04-28 07:37:31

范围- 45℃~+85℃。功能简介YL95 远程I/O模块,可以用来测量五路开关量信号,并有五路继电器输出。1、 开关量信号输入与输出5路开关量信号输入,可接干接点和湿接点,详细请参考接线图部分;五路

2022-04-19 09:32:31

与FPGA的接口电路设计2.1 硬件设计系统中的FPGA输入时钟由外部晶振提供,为20MHz。FPGA的复位信号通过SEP3203的I/O口实现。本系统有2个触发信号:硬件触发信号和软件触发信号。硬件触发

2019-04-26 07:00:06

labview怎么实现像plc一样的通过输入输出I/O量,控制开关量,比如通过I/O点控制继电器的吸合。怎么给I/O量分配地址,怎么在程序里使用这些变量实现一系列有序的动作。希望能附上一份样例程序,让小弟学习领会,请多指教,谢谢。

2016-04-25 00:51:33

i2c_master_bit_ctrl.v 完成位传输的功能。位传输的功能包括数据按位传输的实现和I²C协议各个命令的实现两部分。如图 4-5 所示开始和重复开始命令的产生包括 5 个阶段:idle

2018-10-09 11:43:44

本帖最后由 eehome 于 2013-1-5 10:10 编辑

本节将重点讲解,用FPGA实现按键去抖的方法,在以往的按键去抖中,大部分采用的是单片机去抖方法。这里我们将介绍FPGA的实现

2012-03-19 14:48:40

- 2.5VVCCO_35 - 2.5V连接到I / O bank的一些外部电路在2.5V FPGA电源轨之前上电(这超出了我的控制范围)。这会以奇怪的方式导致2.5V FPGA电源轨斜坡,请参考附图。基本上2.5VFPGA

2020-07-30 09:51:29

前言此实验是通过STM32CubeMX来配置stm32实现按键输入,以此来了解stm32I/O的输入操作及如何使用HAL库来实现I/O输入。本实验中的按键操作使用的是软件中断,并未用到stm32

2022-03-01 06:58:08

电平 ,输出高低电平。就是通过这简单的控制电平来实现大多数的应用控制。1. 什么是 I/O 口?I 表示 IN(输入),O 表示 OUT(输出),所以 I/O = 输入/输出2. I/O 具体能做什么呢?如果你是刚刚步入电子的新手,那你最好要知道一下I/O口具体能做什么。感性的认识对你的..

2021-11-24 06:47:23

美国国家仪器有限公司(National Instruments,简称NI)近日针对PXI平台,推出了一个全新的、开放式的、基于FPGA的产品系列。NI FlexRIO系列产品是工业领域首款成熟商用现成产品,它为工程师们提供了同时结合高速、工业级I/O和NI LabVIEW FPGA技术的解决方案。

2019-10-29 07:03:11

UEFI学习(四)-SuperIo的访问一、什么是Super I/O?二、我们要用SuperIo实现什么三、NCT5581D的访问机制一、什么是Super I/O?Super I/O 芯片也叫 I

2022-01-24 08:12:27

要使用FPGA实现150M的光纤通讯,使用XILINX XAPP244的串行数据恢复功能感觉有些麻烦。使用XILINX的ROCKET I/O 实现150M的光纤通信合适/可行吗?

2013-03-26 16:06:30

芯片中,因为背板机箱中的可重配置FPGA芯片是在RT系统的控制下提供大量的I/O口用于与可热插拔的I/O模块进行通信等功能的,通过这些I/O实现对热插拔I/O模块功能的操作控制,如图1。即

2017-09-23 16:55:58

的功能,而且还可以大大缩短设计时间,减少PCB的面积,提高信号的传输质量,提高系统的可靠性,增加设计的灵活性和可维护性。本文采用FPGA技术实现一个MCU与串行通信外设进行简易通信的平台,一方面了解了计算机的一些控制原理和工作流程;另一方面可以了解利用FPGA进行电子设计的优越性。

2019-07-08 06:28:38

单片机应用系统中,常有用单片机的I/O口来实现自关机(彻底关机)的功能。一般用单片机的一个I/O口控制一个电子开关来实现,因单片机关电后,失去电源,所以在关机时,实现关机的IO口的电平必须用低电平

2017-12-14 20:15:53

您好,我在fpga中采用spi通信读ad9173寄存器时,发现ad9173没有响应。其中spi通信速率为10M完全满足datasheet不大于80M的要求。其中通信方式采用四线制。读取寄存器为

2023-12-01 06:10:50

图2所示。2.2 总线接口设计本设计中采用32bit/33 MHz CPCI总线接口,其传输率可达133MB/s,实现了设备之间的高速通信。通过CPCI连接器,CPCI总线信号与FPGA的I/O口互连

2016-01-14 10:59:18

基于FPGA的光纤通信系统的设计与实现{:soso_e129:}文章下载链接:https://www.elecfans.com/soft/5/2012/20120518272336.html

2012-05-22 22:33:59

于机器视觉、软件无线电、雷达/声呐、医用仪器、光缆普查仪等。下面进入正题:DSP与FPGA通信需要把开发板的拨码开关第5位拨到1,按照IBL NOR模式启动开发板。测试说明:DSP端通过TFTP服务器加载

2018-10-31 14:27:30

的区别。每轮选出的第一层簇头成为第二层簇头的普通节点,在LEACH中这些节点直接与基站通信。由式(1)可以看出,放大器能耗远大于电路能耗,且放大器能耗中与通信距离d有直接关系,因此在产生第二层簇头

2018-11-02 15:19:38

如何采用FPGA实现图像采集卡的设计?

2021-04-29 06:45:55

如何采用FPGA实现视频监视?

2021-04-29 06:24:06

。ECP5 FPGA支持与ASIC、ASSP和应用处理器实现互连,并具备优化的I/O和体系架构。增强的嵌入式DSP块和高度并行的FPGA逻辑架构为计算密集型协处理功能提供了所需的高性能支持。ECP5 FPGA

2020-10-21 11:53:02

如何克服FPGA I/O引脚分配挑战?

2021-05-06 08:57:22

嵌入式测试是什么?如何用FPGA技术去实现嵌入式设计?如何测试FPGA中的高速串行I/O?

2021-04-13 07:03:58

嗨专家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平台线USB II。你能告诉我如何通过JTAG监控PC中FPGA I / O的状态吗?谢谢,V。Prakash以上来自于谷歌翻译

2019-06-18 09:05:14

趋势,而 NI FlexRIO 正是重要的下一步。透过可互换的转接器模组,工程师可确实针对 I/O 需求建立解决方案。再整合 LabVIEW FPGA 与 Virtex-5 FPGA 系统的强大架构,即便是为复杂的设计与测试应用,NI FlexRIO 亦可提供图形化系统设计 (GSD) 的弹性。

2019-04-28 10:04:14

随着现代技术的发展,SPI接口总线已经成为了一种标准的接口,由于协议实现简单,并且I/O资源占用少,为此SPI总线的应用十分广泛。目前,SPI接口的软件扩展方法虽然简单方便,但若用来通信,则速度

2019-08-09 08:14:34

在我的项目中,有两个Straan3A-DSP FPGA,而这两个FPGA需要相互通信。由于Spartan3A-DSP没有Rocket I / O,我使用64位(32位发送和32位接收)并行数据通信

2019-05-24 10:21:47

你好我试图将1PPS从GPS接收器连接到FPGA I / O引脚之一。我希望FPGA在I / O引脚上看到1pps的上升沿时执行一些任务。我正在使用verilog进行hdl。我没有在代码中指出这一点

2019-05-24 08:02:28

数组,将实数数组中大于3的数删除,产生一个新的实数数组;将复数数组的元素都加1+1i,产生一个新的复数数组;5. 将两个新的数组组成一个新的簇。

2016-08-03 11:25:32

of LEACH,多跳LEACH)算法,簇内的节点不是以单跳的方式传输数据到簇首,而是通过簇内其他节点转发。参考文献提出了一个多跳簇首模型,采用从下到上的策略,逐层生成每一层的簇首,最终得到一个多层结构

2018-11-01 15:05:46

大家好,我想检查FPGA功能和I / O引脚功能在我的主板上使用“Selftest application”。在我的Selftest应用程序中,我可以使用哪些方法来检查这些?请提供一些想法。谢谢

2019-04-01 12:33:26

VIRTEX-6 FPGA的I / O支持的最大数据速率是多少?我想在Virtex-6的I / O接收625MSPS的数据。这可以实现吗?

2020-07-13 09:45:20

使用XC7Z020CLG484 FPGA。我使用I / O作为输入。要在i / o上接收任何消息,该i / o所需的最小灌电流是多少?

2020-05-08 08:48:11

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

是整个温控系统的硬件基础,其中涉及到温度采集,与微处理器通信,串口输出,控制数模转换芯片等多个组成部分。本文提出一种高效实用的FPGA接口设计,它能够完成协调各个组成部分有序工作,准确、快速实现数据传输

2020-08-19 09:29:48

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

数784逻辑元件/单元数1862总 RAM 位数25088I/O 数192栅极数40000电压 - 电源3V ~ 3.6V安装类型表面贴装型工作温度0°C ~ 8

2022-04-19 09:45:33

摘 要:本文主要介绍了基于FPGA技术实现与PC串行通信的过程,给出了各个模块的具体实现方法,分析了实现结果,验证了串行通信的正确性。引言串行通信即

2006-03-24 13:31:51 4660

4660

什么是通信量控制/管理器

通信量控制器CC(Communication Controller):CC是用以对数据信息各个阶段进行控制的设备。

2010-03-26 15:52:15 847

847 随着云计算技术的发展,采用FPGA 作为协同加速成为其发展的一个趋势,如何设计与实现FPGA 片间的高速通信是该研究方向的一个热点。研究了FPGA 万兆通信的物理层、MAC 层的实现机制,在通信

2017-11-18 08:13:01 15054

15054

在基于FPGA芯片的工程实践中,经常需要FPGA与上位机或其他处理器进行通信,为此设计了用于短距离通信的UART接口模块。该模块的程序采用VHDL语言编写,模块的核心发送和接收子模块均采用有限状态机

2017-11-18 11:33:01 5152

5152 FPGA diy实现八位拨码开关控制8位LED输出

2018-06-20 14:15:00 8400

8400 FPGA diy作业实现8位LED花样灯加拨码开关控制

2018-06-20 14:08:00 3965

3965

近日,基于现场可编程门阵列(FPGA)的数据加速器件和高性能嵌入式FPGA(eFPGA)半导体知识产权(IP)领导性企业Achronix半导体公司,与Molex旗下的一家领先企业级FPGA加速器产品供应商BittWare今日联合宣布:推出一类全新的、面向高性能计算和数据加速应用的FPGA加速卡。

2019-10-31 15:11:33 737

737 Achronix半导体公司与Mo-lex旗下FPGA加速器产品供应商BittWare联合推出全新的、面向高性能计算和数据加速应用的FPGA加速卡,可实现云计算与边缘计算加速,助力高带宽应用。

2019-11-08 15:07:23 562

562 Molex旗下的 BittWare 公司是一家领先的企业级 FPGA 加速卡产品的供应商,产品适合各种高要求的计算、网络及存储应用使用,公司宣布已经与 Achronix 半导体公司达成战略协作关系

2019-11-19 15:03:11 657

657 4月19日消息,NEC开发了一种装置“NEC AI加速器”,可以减少物连网(IoT)中的通信量。7月开始提供使用。

2020-04-20 17:35:47 3251

3251 Molex旗下BittWare 公司是企业级 FPGA 加速器产品领域一家领先的供应商,现推出全新的TeraBox™ 200DE边缘服务器。TeraBox 服务器产品系列是专为数据中心提供的领先产品

2020-04-21 15:17:32 3471

3471 贸泽将开售采用英特尔®和Xilinx® FPGA技术的BittWare高端板卡级解决方案。

2020-10-14 14:44:00 2709

2709 基于FPGA的光纤通信系统的设计与实现的讲解。

2021-05-25 16:26:19 26

26 基于FPGA的无线通信系统设计与实现

2021-06-16 09:59:29 44

44 Molex莫仕公司旗下的BittWare是致力于边缘计算和云计算应用企业级加速器的领先供应商,宣布扩展其采用IntelAgilex FPGA的IA-系列FPGA加速器。BittWare的IA系列

2021-06-25 17:58:50 3163

3163 BittWare 在之前发布的 IA-840F 企业级 FPGA 加速器中添加了两款基于英特尔 Agilex FPGA 和 SoC FPGA 的新加速器产品(详见此前报道)。 全新的 IA-420F

2021-06-30 10:48:07 2089

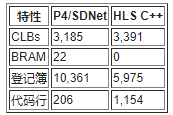

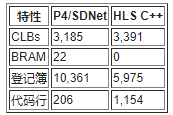

2089 BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一个数据包解析器/分类器,它可以从数据包中提取协议字段。通过这篇白皮书,我们不仅要描述我们的Parser,还要解释如何使用HLS来构建和配置它,从而获得比使用P4语言更好的实现。

2022-08-02 08:03:33 681

681

正在加载...

1673

1673 1673

1673

6949

6949 6949

6949 电子发烧友App

电子发烧友App

评论