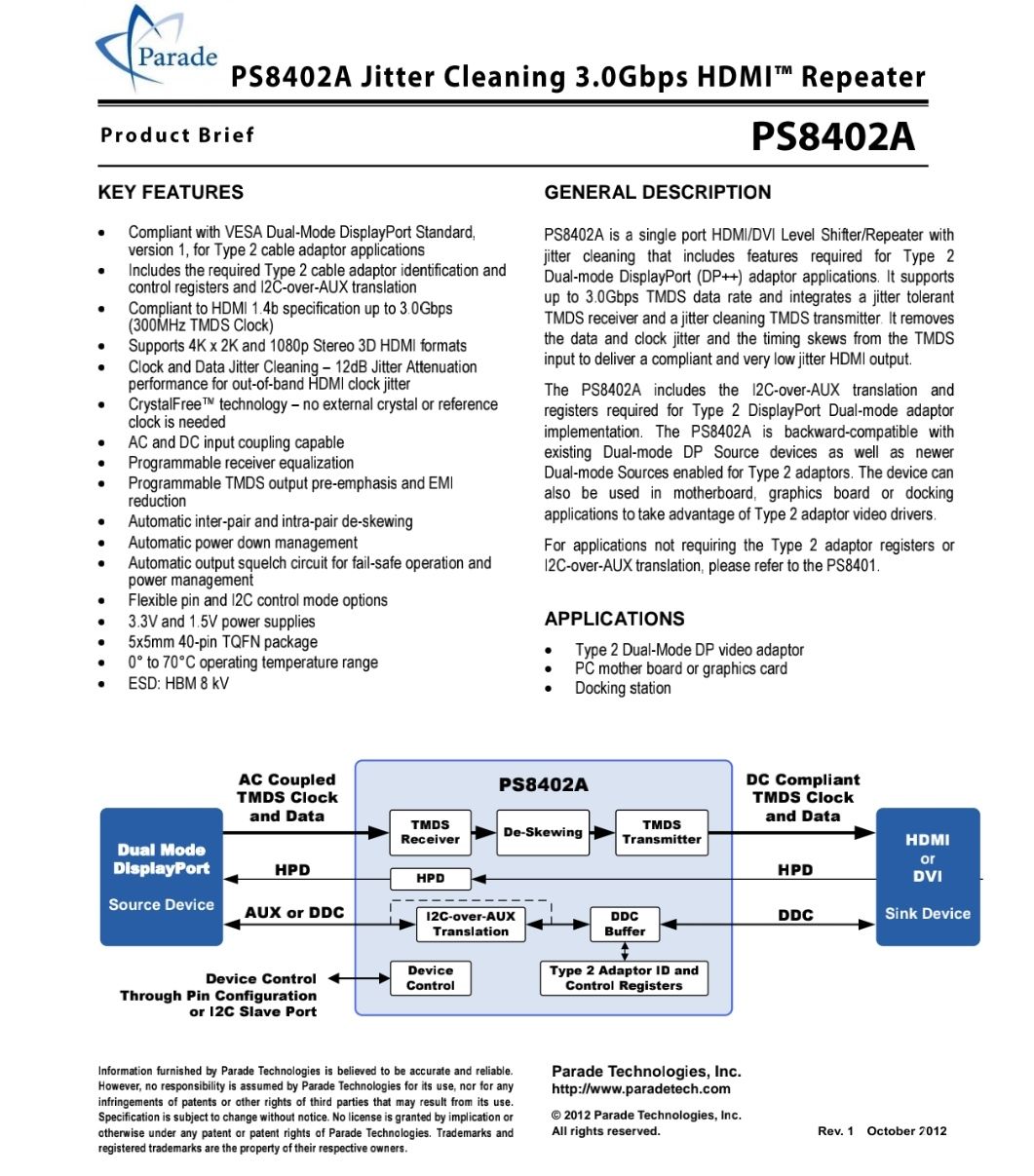

随着消费类电子功能需求的增加,HDMI作为新一代的数字音视频接口越来越多的应用到消费类电子产品上。带HDMI功能的电子产品大量问世,HDMI的接口数量也随之增加。数字电视作为音视频表现的一种载体,其HDMI接口的应用主要作为数字音视频数据的接收端。为了能使数字电视连接更多的HDMI设备,许多集成电路设计公司都适时推出了三选一或四选一的HDMI开关,用于满足HDMI接收端多接口的需求。本文主要介绍基于Parade公司的一款三选一HDMI开关PS321的应用设计。

硬件设计

1 芯片选型

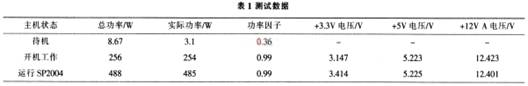

PS321作为一款三选一的HDMI开关,与其他厂商相类似的产品相比较具有较多优势。将PS321与另一款通用的三选一HDMI开关进行比对,结果如表1所示。

从以上比对中可以看出PS321具有以下优势。

● 在数据传输率、HDMI线传输距离、节能以及ESD(防静电)方面具有优势;

● 支持I2C控制,方便设计者使用;

● 内置EDID缓存,无须在HDMI接口上外加用来存储EDID数据的E2PROM,从而降低电路成本;

● 内置均衡器,可调节增益,用来弥补HDMI信号在线路上的传输损失。

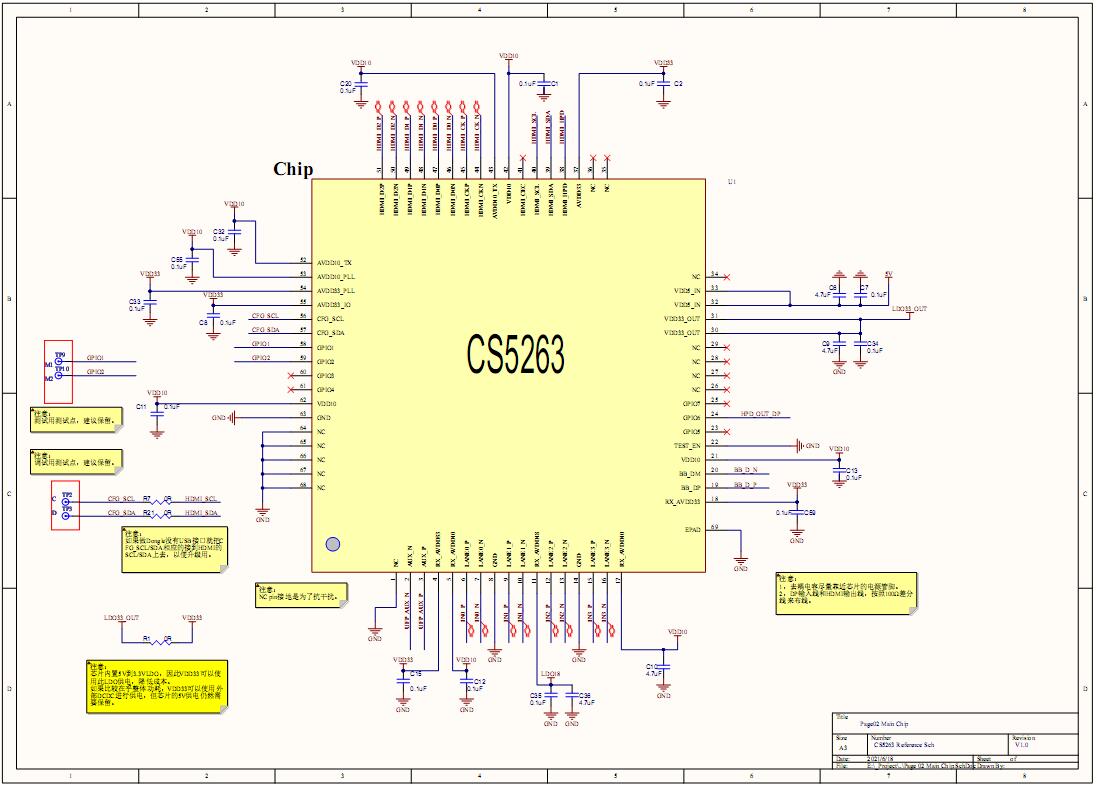

2 电路设计

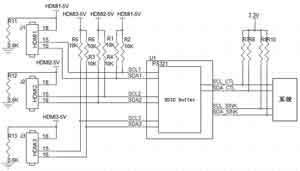

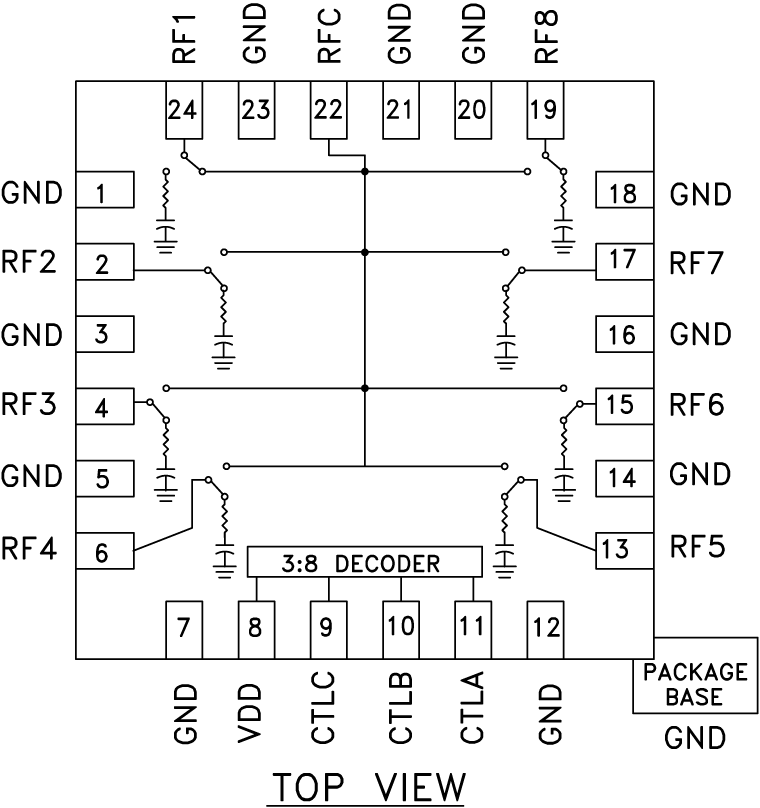

①DDC接口电路设计

DDC(显示数据通道)主要用于HDMI源端设备(Source)与接收端设备(Sink)之间进行EDID数据及HDCP密钥的交流。通过EDID交流,源端设备可以了解到接收端设备音视频的接收能力;通过HDCP Key的交流,可以实时的进行数据流的内容保护认证,从而达到数据内容保护的目的。DDC的电路方式与I2C电路相同,因此在DDC电路设计中,设计者要考虑到DDC线路的电平。按照HDMI 1.3a规范,HDMI源端DDC的上拉电阻最小为1.5kΩ,考虑到HDMI认证中DDC电平的要求(在 4.5~5.5V之间),将DDC信号均通过10kΩ的电阻上拉到HDMI接口的第18引脚(HDMI源端5V电源),如图1所示。经计算,源端与接收端的DDC总上拉电阻的最小值为R总上拉min =1.5kΩ‖10kΩ=1.3kΩ。经测试,接收端DDC的电平约为4.68V,因此满足HDMI认证要求;而DDC总上拉电阻的最小值 1.3kΩ也满足I2C的规范。

图1 DDC接口电路图

由于PS321的DDC内部有弱上拉,当HDMI接口未接HDMI源设备时,DDC内部的上拉电平会通过10kΩ的电阻传递到HDMI接口的第18引脚,导致HDMI接口的第18引脚电平大于1.5V,不满足HDMI认证要求。因此需要将HDMI接口的该引脚接一个3.6kΩ的电阻到地。经测试,当HDMI接口未接HDMI源设备时,HDMI接口的第18引脚电平约为0.5V,满足HDMI认证要求。

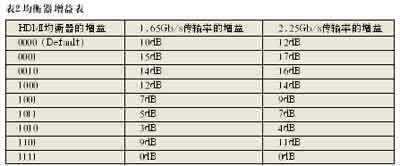

②均衡器设计

均衡器设计主要是针对弱信号做必要的信号整形,以保证HDMI数据传输的完整性。在I2C工作方式下,可通过寄存器来设置均衡器的增益大小。3个HDMI输入端口的均衡器增益大小可以分开调节,如表2所示。设计者可以通过3个HDMI输入端口信号的损失情况来决定采用哪一挡。

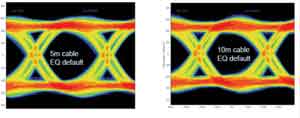

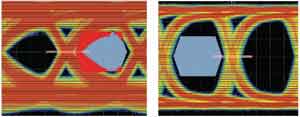

进行如下测试:准备两根HDMI线,一根长5m,一根长10m,在均衡器增益均为默认值下同样传输2.25Gb/s数据率的信号,得到如图2所示的数据眼图。经比对,10m长的传输眼图的面积比5m的小,但还不影响传输信号的完整性。设计者在使用均衡器设计时,需要判断信号的强弱以决定采用哪一挡的增益。目前在电视设计中经常遇到需要一个侧置的HDMI接口,而HDMI开关通常在主板上,离侧置的HDMI接口有一段距离。当然此距离一般不会超过1m,采用标准的HDMI线不会影响到信号质量,但是如果采用普通的连接线就可能造成信号失真。此时需要通过适当提高均衡器的增益大小,以保证信号传输的完整性。如图3所示。左侧为PS321输入端采集的普通连接线的传输信号,可以看到眼图面积变小,信号的损失很大;右侧为经过PS321提高均衡器的增益后采集的传输信号,可以看到信号经整形后恢复完整性。

图2 2.25Gb/s数据率的传输眼图

图3 提高均衡器的增益以保证信号传输的完整性

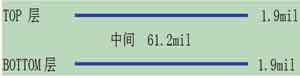

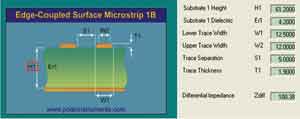

③TMDS信号的PCB设计

HDMI数据流以TMDS信号形式传输,包括三对差分数据线和一对差分时钟线。根据HDMI 1.3a规范,要求TMDS差分阻抗为100Ω±15%。如果按照两层PCB来设计,如图4所示。经计算,两层PCB的厚度为61.2+1.9 +1.9=65mil,约为1.6mm;PCB板材的介电常数为4.2。根据TMDS差分阻抗为100Ω的目标要求,将以上参数带入差分阻抗计算软件 Polar Si9000中计算,将得到PCB设计的指导参数,如图5所示。

图4 双层PCB架构

图5 差分阻抗计算

从图5中可以得出以下PCB设计参数:差分走线宽度为12.5mil;差分线间距为5mil;差分阻抗约为100Ω。

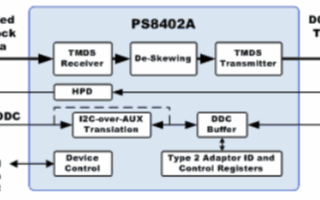

软件设计

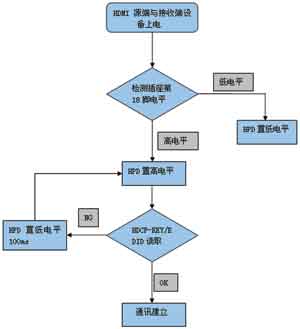

1 HPD操作设计

HPD(Hotplug热插拔)操作设计是HDMI接口软件设计的一个重要环节,它是由接收端设备(Sink)发出的,在与HDMI源端设备(Source)之间建立正式通信的前奏信号。HPD信号电平为高时表示接收端设备已经准备好了,允许源端设备访问接收端设备。

在HPD操作的软件设计中,要考虑如下两个因素。

一是HDMI源端设备输出的电源脚(HDMI接收端插座的第18引脚)的检测。如果HDMI接收端插座的第18引脚为低电平,表示HDMI源端设备未准备好,此时接收端设备应把HPD信号置低电平;如果HDMI接收端插座的第18引脚为高电平,表示HDMI源端设备已准备好,此时接收端设备根据自身的情况可以有选择的将HPD信号置高电平,以通知HDMI源端设备,表明接收端设备也准备好。

二是源端与接收端通信失败下的模拟HPD操作。当HDMI源端与接收端的通信刚建立时可能出现HDCP-KEY读取失败或EDID数据读取错误的情况,造成HDMI工作不正常,此时为了恢复正常的通信,需要进行模拟的HPD操作,即由接收端设备将HPD信号从高电平拉为低电平,HPD低电平持续100ms左右,再拉回高电平,这样源端设备会检测HPD信号的跳变,重新发起读取操作,为建立正常通信做进一步的尝试。这种软件模拟HPD的操作可以在不需要人为热插拔操作的协助下以模拟硬插拔的方式来重建HDMI的正常通信,从而可以消除通信不稳定引起的故障。考虑到以上两个因素,设计者可以很容易地掌握HPD操作的软件设计流程,如图6所示。

图6 HPD操作的软件设计流程

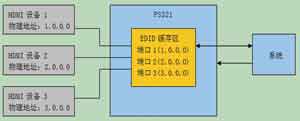

2 CEC操作设计

CEC(消费类电子控制)操作是HDMI接口的一个重要扩展功能,它采用“一线”(One Wire)通信方式,将HDMI的设备连通起来,使HDMI设备之间的操作简单化。如果PS321采用内置的EDID缓存区来配置,那么PS321的CEC操作设计主要是CEC物理地址的分配,如图7所示。

图7 CEC物理地址分配

CEC物理地址的分配有两种方式:硬件方式和软件方式。

①硬件方式

当HDMI接收端设备上电后,系统通过I2C将EDID数据包括HDMI端口1的物理地址写入PS321的EDID

缓存区,HDMI 3个端口的物理地址分配如下:端口1默认为1.0.0.0;端口2和端口3的物理地址由PS321

以硬件方式在端口1默认地址的基础上实现“自动加一”操作获得,因此端口2为2.0.0.0;端口3为3.0.0.0。

以硬件方式获得的CEC物理地址是固定的,不能改变,因此HDMI端口2和端口3的物理地址是不能改变的。

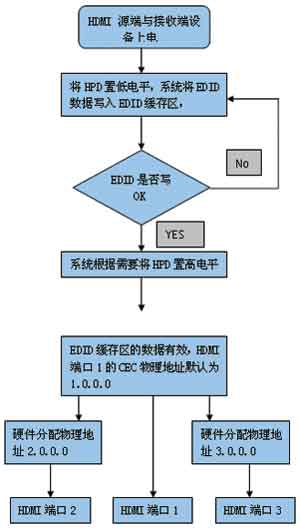

硬件方式设置CEC物理地址的流程如图8所示。

图8 硬件方式设置CEC物理地址的流程图

②软件方式

HDMI端口1的物理地址来自EDID缓存区,是由系统通过I2C将EDID数据包括HDMI端口1的物理地址写入PS321的EDID缓存区,这一点与硬件方式相同。HDMI端口2和3的物理地址存在专门的寄存器中,调用时将其映射到EDID缓存区。以软件方式设置的CEC物理地址可以更改。软件方式设置CEC物理地址的参考流程代码如下:

Set HPD Low

//将HPD信号设为低电平

WriteREG(Page0.0x10,0x01)

//激活软件方式设置CEC物理地址

Load EDID to PS321 EDID Buffer for HDMI1

//将EDID数据包括HDMI端口1的物理地址写入EDID缓存区

Load CEC Physical Address location to Page0.0x17

//将CEC物理地址的位置写入寄存器0x17

Load CEC Physical Address&checksum for HDMI2 to Page0.0x11~0x13

//将HDMI2物理地址及校验码写入寄存器0x11~0x13

Load CEC Physical Address&checksum for HDMI3 to Page0.0x14~0x16

//将HDMI3物理地址及校验码写入寄存器0x14~0x16

WriteREG(Page0.0x10,0x07)

//3个HDMI端口的EDID及CEC物理地址已准备好

Set HPD High

//将HPD信号设为高电平

结语

通过PS321的应用设计,可以进一步的了解HDMI开关在软硬件设计方面的设计要点。随着HDMI接口的大量使用以及高清音视频数据流的发展,HDMI开关将开发出集成更多、更新的功能应用,例如,TMDS信号自适应均衡化功能;HDMI-CEC指令接收、解码及发送等功能。

电子发烧友App

电子发烧友App

评论