无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖动、精确的频率转换和去抖动能力。高性能转换器时钟解决方案所体现的许多属性可被有线网络所用的时钟解决方案延用。整个有线网络对互操作性和可靠同步的需求也衍生出某些独特的时钟系统需求。希望这篇文章有助于对这两个应用领域的时钟技术需求进行对比和分析。

转换器时钟

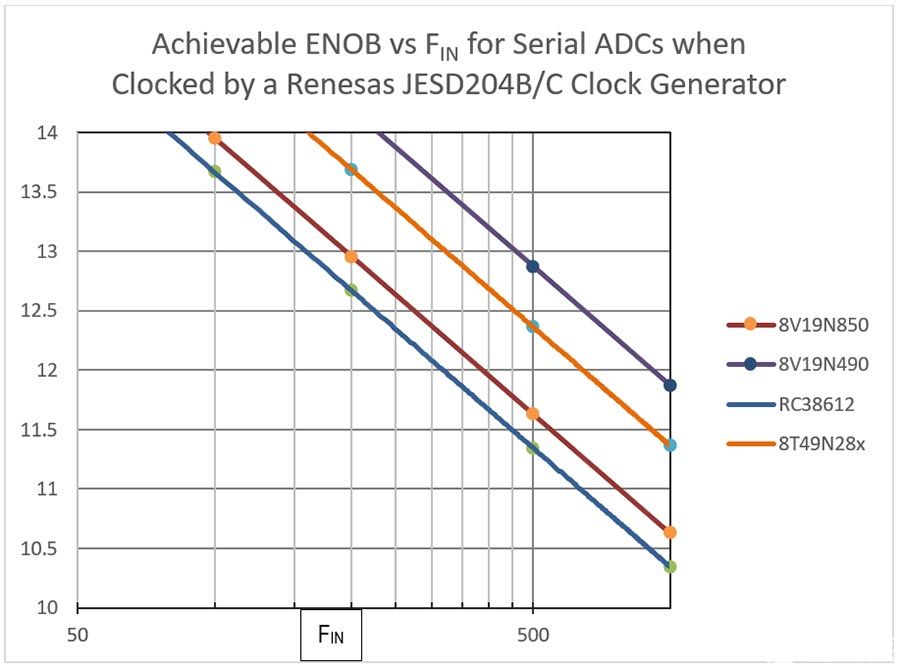

基站收发器、宽带调制解调器和高端仪器仪表通常需要具有高动态范围和高采样率的ADC和/或DAC。高动态范围是为了将信号解析到所需的精度。高采样率则是处理高带宽信号所必需的。无论是无线电系统、调制解调器或者是测量仪器,对转换器的要求将取决于整个系统的规格参数和架构。该转换器的采样时钟的频谱纯度往往会对实际达到的性能产生重大影响。

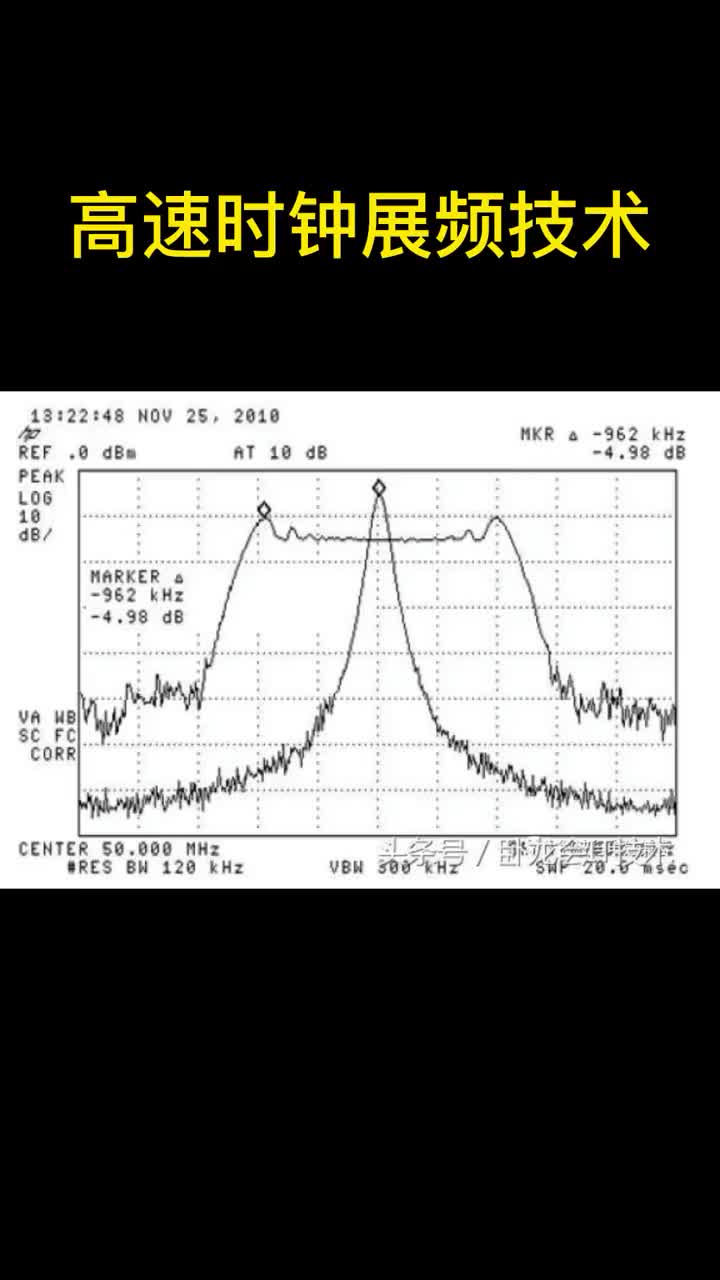

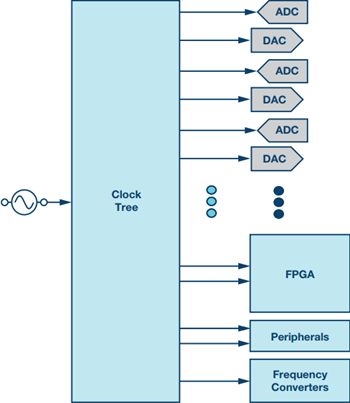

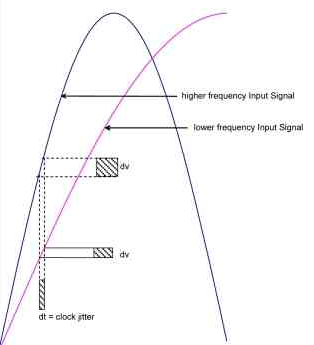

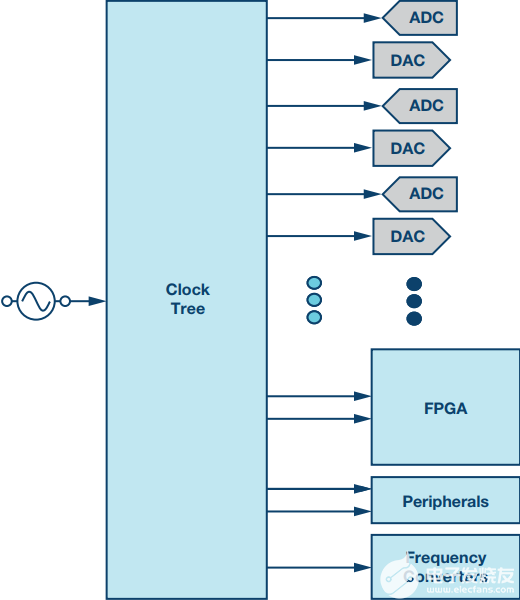

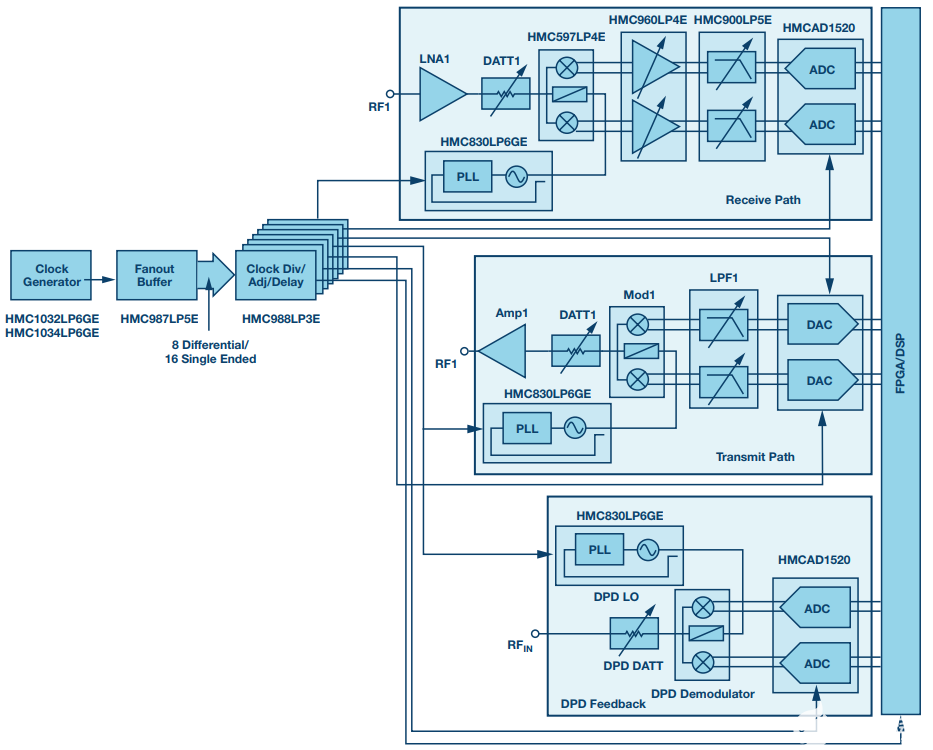

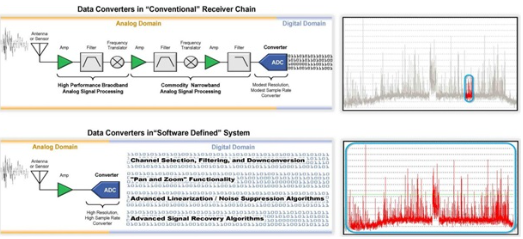

一个无线收发器电路的例子如图1所示。除了为ADC和DAC提供时钟,时钟发生器还负责将时钟信号分配到收发器卡上的其他几个电路模块。接下来我们将集中讨论时钟抖动和相位噪声对ADC性能的影响。

图1:收发器系统框图。

无线电接收器中ADC的一个关键指标是信噪比(SNR),它将影响到ADC在给定幅度范围内能够达到的信号采样精度。理想情况下,ADC应该能够以很高的分辨率将非常小的模拟输入信号转换成精确的数字信号。按照无线电术语,ADC的SNR将决定最小可检测信号(MDS)。

N位转换器基于量化噪声的理论SNR等于:

SNR = 6.02(N) + 1.8 db

因此,对于一个14位转换器,其可以实现的最佳SNR大约为86db。

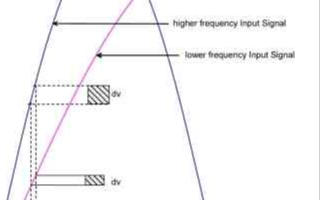

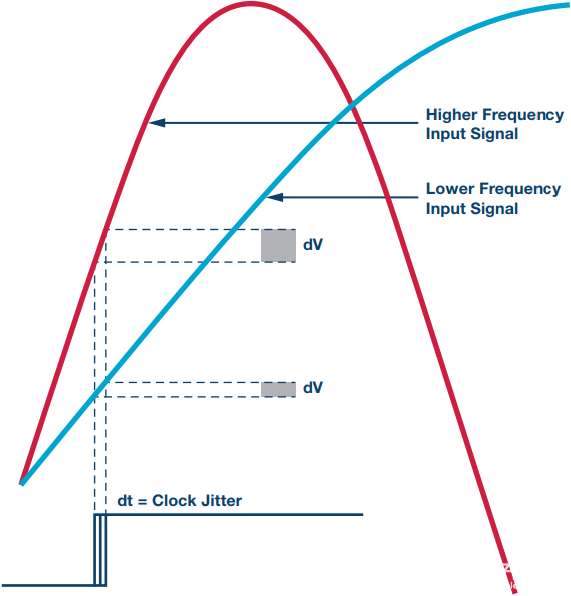

在IF采样架构中,如图1所示框图,对时钟抖动的要求可以说非常严格。事实上,提供给ADC的时钟的质量常常是系统SNR性能的一个限制因素。这可以通过以下公式来理解。

这个公式定义了采样时钟的宽带抖动与ADC在某一给定模拟输入频率抖动情况下可以达到的最大SNR之间的关系。举例来说,如果采样时钟的宽带抖动为275fs ,对170MHz的中频信号采样时,SNR基本上不会高于70.65db。

实际上,ADC内的其他噪声机制通常会将SNR值限制在低于理论水平或量化噪声(公式1) 。这一内部噪声是由于模拟信号路径和采样时钟路径中的器件热噪声而引起的。采样时钟路径中的器件噪声有效地转换为相位调制噪声,又称为孔径抖动。这种行为就像外部时钟上的抖动,遵循公式2 ,孔径抖动(taperture-jitter)代替时钟抖动(tclock-jitter)。由公式2可以看出,随着采样的IF频率(fanalog)增加,SNR下降。

外部时钟的频谱纯度与ADC可实现的SNR之间的关系,可以通过以下一组实验室测量数据进行表述。图2显示了14位ADC采样170MHz中频信号的FFT波形。在这种情况下所用的外部时钟是源自频谱纯净的Wenzel实验室参考振荡器,驱动着带高压摆率输出信号的低抖动矩形波整形电路。测量的意图是尽量减少时钟的影响,并确定由于ADC效应所达到的SNR。由此产生的相对满量程输入信号的SNR测量数据,在图中标示为SNRFS,是76db。这与ADC数据手册1是一致的。Wenzel实验室参考振荡器的确会对SNR有一定影响,但所测的SNR主要是受ADC量化噪声和内部ADC孔径抖动的共同影响。

图2:14位ADC的FFT波形。模拟输入频率= 170MHZ,时钟频率= 122.88MHz。SNRFS =76db。

现在,我们将使用一个适合实际收发卡时钟应用的内置VCO的时钟IC。为了估算这一时钟信号对ADC性能产生的影响,我们可以先测量时钟电路的相位噪声。其相位噪声曲线如图3所示。

图3 :时钟IC在122.88MHz下的相位噪声

在给定的频率范围内,我们可以使用下列公式来将相位噪声转换成时间抖动。

该公式本质上是对相位误差在目标频率范围内进行积分并从一个相对2π的积分弧度误差转换成均方根时间误差。

将图3的相位噪声数据代入公式3,在50kHz至61MHz的频率范围内,会得出230fs的抖动值。50kHz至61MHz频率范围是用来对应有效的FFT测量范围,后者将用于检验抖动对所测SNR的影响的估算是否准确。低至50kHz是源于FFT的有效二进制间距,高至61MHz是奈奎斯特频率。将得出的230fs抖动代入公式1则得出72.2db的SNR值。

然而,实际达到的SNR将受到该抖动和固有ADC噪声的共同影响。图2 FFT波形的SNR(76db)与根据时钟抖动得出的估算值(72.2db)的和平方根将得出70.68db的复合SNR。

为了检验这一估算值,图4显示了采用此时钟IC作为采样时钟的相应ADC FFT波形。所达到的SNR接近基于时钟抖动的估算值,体现了时钟抖动对ADC性能的影响至关重要。

图4:采用时钟IC的14位ADC的FFT波形。模拟输入频率= 170MHZ,时钟频率= 122.88MHz。SNRFS =70.75db。

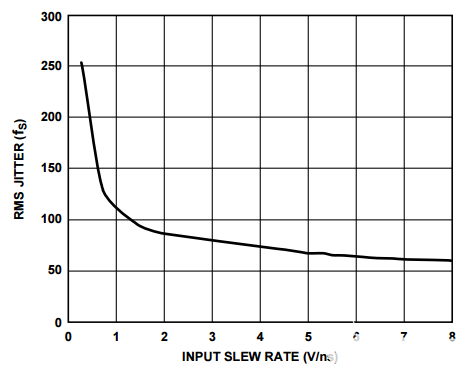

应该强调的是,公式2中的抖动是宽带均方根抖动。抖动带宽有时被认为是ADC编码输入的有效带宽。由于该ADC是个采样系统,编码输入的宽带噪声在奈奎斯特频带内可能被混叠多次。被混叠的抖动带宽的有效数字等于将奈奎斯特带宽除以编码输入的带宽。(见参考文献3提供的详细方案)。但如果时钟边沿的压摆率很快速,在编码输入处噪声电压到时间误差(抖动)的转换将被衰减。通过在编码输入之前改善时钟边沿和保持很高的压摆率可获得最佳的性能。在这些条件下,将抖动进行高达奈奎斯特频率的积分就可提供一个合理的估算,因为上述相关性表明了该时钟抖动对ADC SNR的影响。

尽管上述讨论的重点是ADC,本底噪声和DAC的SNR由于高抖动采样时钟会以类似方式下降。

采样时钟的宽带抖动并不是采样时钟频谱纯度的唯一需要考虑的方面。“近载波”(close-in)相位噪声3也会影响系统性能。

不过近载波相位噪声对SNR的影响甚微,更重要的影响来自相邻信道信号产生的相位噪声,可以使一个“有用”信号失真。这种效应类似于模拟混频过程中的相位噪声相互混频。转换器的编码过程本质上是复制混频过程。编码时钟和模拟输入信号在时域中相乘。这相当于在频域中进行大家熟知的卷积。如图5所示,其结果是造成在编码时钟上的任何相位噪声裙缘将被复制在采样输入信号上。基于编码率和采样信号之间的频率比例,关于每个载波幅度的相对相位噪声将被修改。一个强相邻信道信号的相位噪声裙缘扩展到一个有用弱信道时,并有效地使后者失真,问题就出现了。图6的FFT波形体现了这种效应。在此图中,一个ADC采样一个小的有用信号,但存在很强的相邻干扰,干净时钟条件和高相位噪声条件相重叠。可以看出,时钟的相位噪声裙缘在强干扰上被复制,并扩展到有用信号的频带中。取决于所采用的调制标准,相位噪声频率偏移可从数十kHz扩展至数MHz。

图5 :频谱分析仪波形图:层叠在干净时钟上的带高相位噪声的编码。

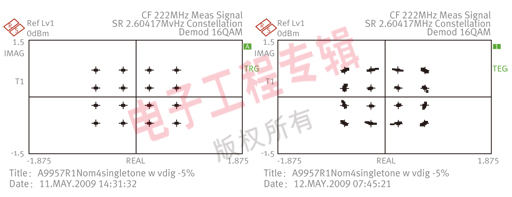

采样时钟相位噪声对DAC的影响通常表现为调制信号的误差向量幅度(EVM)有所降低。对于给定的调制方案,高相位噪声有效地影响星座点使EVM下降并潜在地提高了误码率。图7所示的16 QAM星座图中体现了这一点。图7(a)展示了干净时钟条件下的星座图。图7(b)展示了高相位噪声时钟对星座图的影响。相位噪声事实上旋转了降低相邻点噪声容限的星座点有效相位。应当注意的是,宽带相位噪声和抖动也会降低EVM。在带通滤波用于DAC输出的应用中,主要的考虑事项就是近载波相位噪声。

图7:(a)干净时钟的16QAM星座图。(b) 带高相位噪声的时钟对星座图的影响。

显然,时钟的频谱纯度是收发器时钟解决方案的一个关键方面,但人们还期望时钟系统能提供其他一些功能。

回到图1可看到,该收发器具有多个接收通道,每个都需要单独的ADC。在某些情况下,也会使用多个DAC通道。可能需要额外的时钟通道来为用于数字预失真、FPGA或基带ASIC芯片的ADC提供时钟。

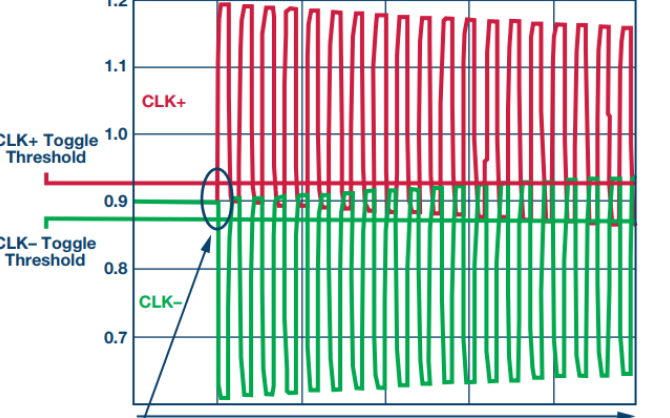

DAC和ADC编码率通常各不相同。FPGA和基带元器件也可能需要不同的频率。频谱干净的主时钟信号需要单独分配给每个通道,为该通道分频为所需的频率,然后转换成适当的输出信号格式。单一收发卡的输出信号通常混合了LVPECL、LVDS和CMOS格式。两个通道之间往往要求偏斜很紧密,以限制PCB布线的延迟变化。在某些情况下,在两个时钟之间设置延迟或相位偏移是必要的。在转换器采样时钟和用于将ADC输出数据锁存到基带芯片的时钟之间可能需要这样做。

在这些系统中,通道与通道之间的耦合是一个需要考虑的因素。如前所述,DAC和ADC时钟通常运行于不同的频率。通道之间的耦合,或时钟从一个通道向另一个馈送可能会在采样时钟上导致不想要的杂散音。有用的时钟信号和无用的噪声可能会导致产生乘积混频,这可能在有问题的地方产生毛刺。如果混频发生在编码输入处,这些问题有时可通过在主时钟和输入时钟边沿及时进行偏置而得到缓解。具备调节每个低抖动时钟延迟的能力可以成为时钟系统的一项优势。

为了尽量减少系统宕机时间,在输入参考出现故障的情况下,时钟系统应提供“备份”功能。这可通过增加第二个参考输入来实现,在主参考出错的情况可以切换到这个备份参考输入。这种备份时钟的指配有时被称为“时钟冗余”。监测主时钟、检测故障然后切换到备份的能力被称为“参考切换”功能。

对于主时钟和辅时钟均出现故障的情况,可实施另一层保护功能,被称为“保持(holdover)”。在保持模式中,时钟系统进入一种模式,即在输入失效之前尽可能长时间地保持时钟频率。对于给定的时钟系统,保持的准确性和持续时间取决于时钟电路架构。本文第二部分在讨论网络时钟时对此会有更详细的阐述,因为那些系统中的保持模式要严格得多。对于收发器系统,保持模式并不试图让收发器工作在它的正常性能水平,而是要保持足够的时钟功能,如可生成适当的系统警报以启动系统修复。

总而言之,多种多样的系统需求广泛存在,以支持各种各样的空间标准、系统通道数要求和架构方案。这些系统的时钟必须足够灵活,以适应广泛的应用、保证系统可靠性并且还能够提供转换器所要求的极低抖动和相位噪声。

(1) AD9445:14位125MSPS , IF采样ADC

(3) 采样系统和时钟相位噪声和抖动的影响。

电子发烧友App

电子发烧友App

评论