均有优势。 因此,CPCI总线已成为当今应用最广泛的工业计算机总线,基于CPCI总线的工业控制计算机已经成为解决大量高速数据处理的一个新方向。

2020-01-26 16:08:00 2701

2701

基于 DSP TMS320C6455的CPCI高速信号处理板卡1、 板卡概述 基于 DSP TMS320C6455的CPCI高速信号处理板卡是新一代高速DSP处理平台,广泛用于DSP性能验证

2014-06-11 11:11:47

`基于TI DSP TMS320C6678、Altera FPGA的CPCI处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP

2015-09-17 14:38:59

基于TI DSP TMS320C6678、Altera FPGA的CPCI处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP

2015-09-11 16:55:46

基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纤信号处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP

2015-05-11 17:14:29

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纤信号处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP

2015-09-14 11:56:15

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纤信号处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP

2015-09-18 15:24:37

`[fly]资料来源网络转载和搜集,请慎重参考哦,只为学习交流为主哈。。[/fly]CPCI总线(CompactPCI,紧凑型PCI),是PICMG(PCIIndustrialComputer

2013-01-12 11:46:35

有一个背板,用的CPCI,然后加了一个PCI,插入PCI的IO板卡时,能搜索到IO板卡,但是软件配置时配置不了IO信号,软件配置进入不了,是为什么呢?网卡板插入时,也能装好驱动,但是也通不了,网络总是被禁用,开启不了。求解答,大神呀!!!

2017-06-21 11:13:29

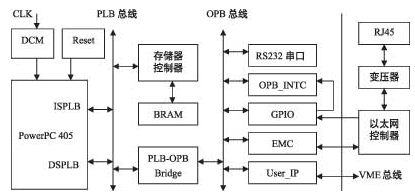

` PowerQUICC III系列处理器具有卓越的高集成度和高性能表现,其重要代表MPC8541E处理器,具有强大的e500 PowerPC内核, 主频533MHz~1.0GHz, 256KB

2017-06-19 09:45:36

ARM处理器的三大特点分别是什么?PowerPC架构相比于ARM有哪些优势?

2021-09-23 07:28:25

本人刚接触cpci总线,自己做的背板(两槽),一块插计算机,一块自己做的电路板,出现如下

2008-12-29 18:35:26

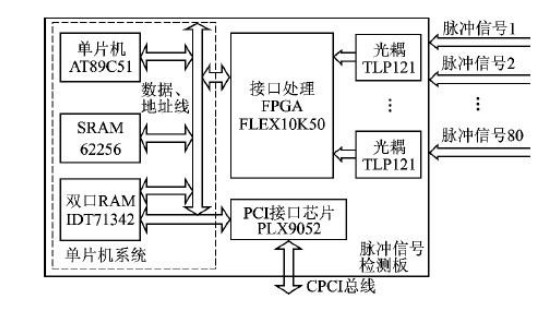

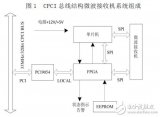

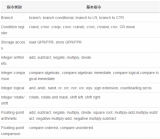

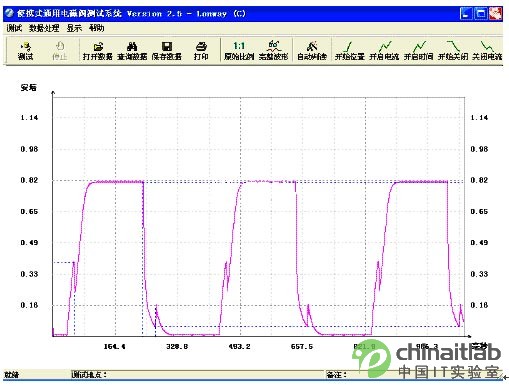

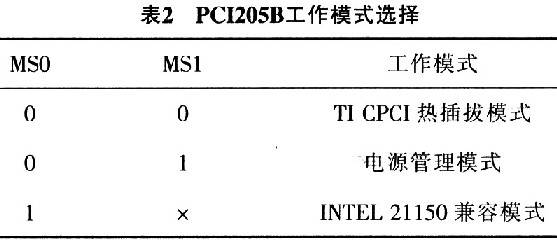

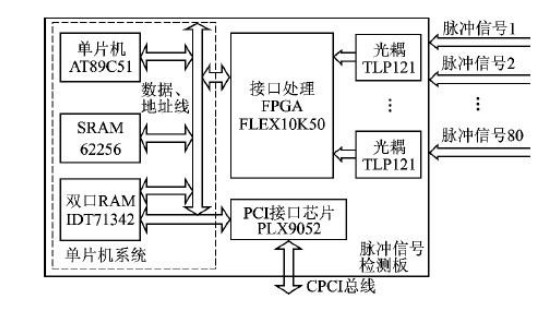

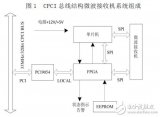

信号的发生时间及脉冲持续宽度,要求测量误差不大于±1ms。 如图2所示,脉冲信号检测板的核心部分包括光耦接口电路、接口处理FPGA、单片机系统和PCI接口电路。板卡采用标准的6U尺寸CPCI板卡

2012-09-01 16:09:40

基于 DSP TMS320C6455的CPCI高速信号处理板卡1、 板卡概述 基于 DSP TMS320C6455的CPCI高速信号处理板卡是新一代高速DSP处理平台,广泛用于DSP性能验证

2014-06-10 10:16:14

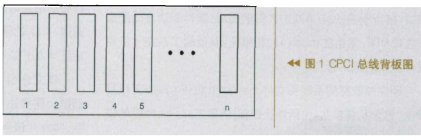

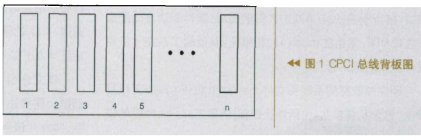

简称CPCI,中文又称紧凑型PCI,是国际PICMG协会于1994提出来的一种总线接口标准。它将VME密集坚固的封装和大型设备的极佳冷却效果以及PC廉价、易采用最新处理能力的芯片结合在一起,既保证了

2019-04-24 07:00:07

%的高可靠度,又极大降低了硬件和软件开发成本。其整体机构紧凑,安装牢固,适应各种运输条件,可靠性高。各功能板采用CPCI总线的模块化结构,插拔十分安全方便,特别适合本系统的多种型号测试对象和多种测试

2008-07-04 09:05:40

,又极大降低了硬件和软件开发成本。其整体机构紧凑,安装牢固,适应各种运输条件,可靠性高。各功能板采用CPCI总线的模块化结构,插拔十分安全方便,特别适合本系统的多种型号测试对象和多种测试工况的要求

2008-07-10 08:08:08

PowerPC440GP是IBM公司推出的高性能32位RISC嵌入式处理器,片上集成了PowerPC440内核及各种丰富的外围设备接口资源、最高速度可达500MHz,适合应用在嵌入式产品诸如交换机

2018-12-06 10:21:41

我想用DSP能够和CPCI总线连接。C6000系列的。不知道有什么方案?不想用PCI2040

2018-06-21 01:00:59

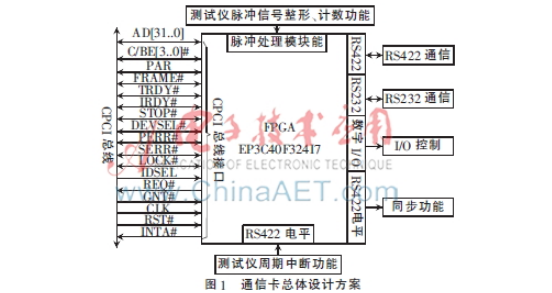

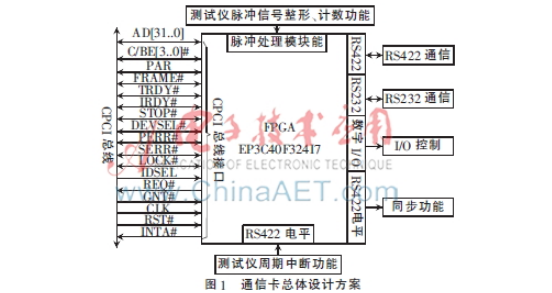

摘 要: 为了提高航空航天领域对信号处理、传输的实时性及可靠性,以CycloneIII系列EP3C40F324I7为核心处理器,设计了一种基于CPCI总线的多功能通信卡。结合高效的FPGA算法

2016-01-14 10:59:18

的cPCI板,当这块电路板插到背板时,热插拔控制器必须完善地执行以下的操作: 1)测试cPCI总线电源处于稳定状态,且用/BRD_SEL信号使电路板就位。这些条件得到满足时,控制器可以连接电路板的电源系统

2011-12-12 16:51:57

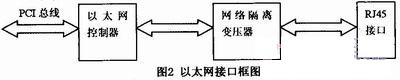

CPCI的特点是什么?CPCI总线与Intel 82551是如何连接的?如何去实现一种基于CPCI总线的以太网卡?

2021-06-03 06:49:06

文中采用Ahera公司最新、具有最佳性能、最大密度和最低功耗的高端FPGA StratixⅢ设计了基于CPCI总线的通用FPGA信号处理板,并在某雷达系统中进行了实际应用。

2021-05-07 06:54:25

本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。

2019-08-27 08:24:41

怎么实现基于CPCI总线的多网口卡设计?

2021-06-02 06:15:08

请求大神分享一款基于CPCI总线的智能A/D,D/A模块设计

2021-04-20 06:05:45

本文首先介绍了PCI Bridge的工作原理;然后以Motorola公司提供的CPX8000系列工控机为例,讨论了两个SBC是如何基于背板(Backplane)上的CPCI总线,并利用PCI Bridge的地址映射机制,通过互访内存的方式最终实现双机通信;最后介绍了实际应用时应注意的性能优化问题。

2021-06-03 06:45:30

1.产品特点* CPCI总线(可定制PXI/PXle/PCI/PCle总线)* 扩展槽:3U8槽CPCI背板 , —个系统槽 , 7个扩展槽;不支持后I/O2.性能参数* 处理器:Intel

2022-04-24 16:55:17

产品主要特点 符合CPCI总线标准规范国产加固机架式CPCI测控平台标准19寸机架式安装CPCI模块信号后出线设计内置厚物科技CPCI-9333或CPCI-9363控制器内置厚物科技3U

2022-04-26 11:11:10

产品描述CHR81002/CHR81014是一款通用型8槽机箱。该机箱提供1个系统槽和7个CPCI外围卡槽,可满足大多数测试测量应用。机箱整体采用铝型材框架式结构,有效的了箱体的结构强度,更能适用

2022-05-26 11:48:06

cpci 3.0规范,cpci3.0标准免费下载

PICMG 2.0 R3.0 CompactPCI â Specification

CompactPCI

2009-06-14 16:12:08 264

264 介绍一种基于cPCI 总线的点到点高速数据光纤传输系统,提出了用现场可编程大规模集成逻辑器件取代分立元件完成接口卡设计及力求达到更高的传输速率的思想,并实际设计实

2009-06-17 11:12:03 20

20 使用WindRiver 公司提供的 Torrnado 集成开发工具,将VxWorks 移植到PowerPc 处理器上,将移植结果应用在跑马灯的实现上,运行正常,表明移植成功。关键字: PowerPC;VxWorks;Tornado;移

2009-06-23 13:08:45 44

44 本文基于PowerPC7410 芯片与常用DSP 芯片性能的比较与分析,指出了PowerPC 在大数据量、高速信号处理中的巨大优势和应用潜力,最后给出了采用PowerPC 实现的SAR实时距离向压缩模块

2009-06-29 08:29:42 41

41 章介绍了PowerPC 60x 处理器的总线接口和操作,详细阐述了60x 总线存储器

控制器在CPLD 上的设计与实现过程。此存储器控制器可提供60x 总线与多种类型的SRAM的接口,及与FLASH

2009-08-26 10:38:37 57

57 CPCI 总线是一种兼容性强、功能全面的计算机总线。文章通过对TI 公司推出的DSP 芯片(TMS320F2812)、FPGA 芯片(EPF10K30A)和CPCI 接口芯片(PCI9054)的功能和特点的深入分析,讨论了

2009-12-19 12:08:10 35

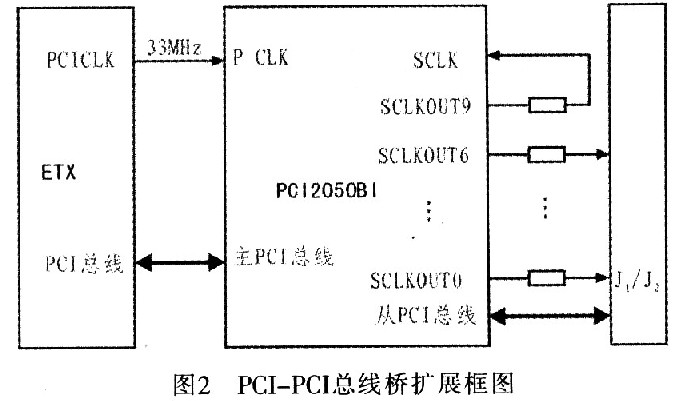

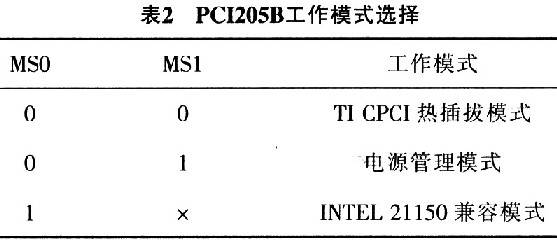

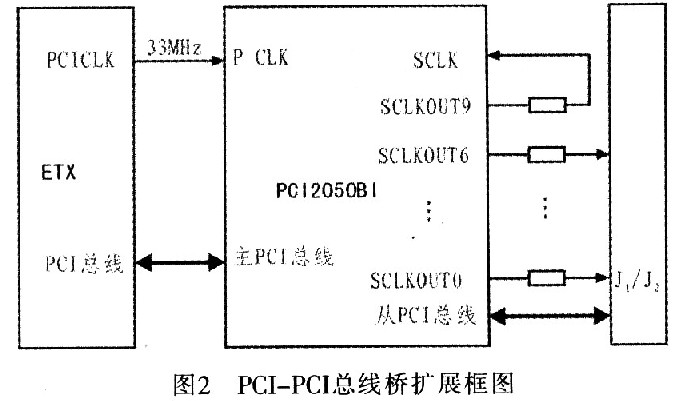

35 提出一种基于CPCI总线插槽的4网口卡的设计方案。运用Intel公司的Intel82551以太网控制器和TI公司PCI2050B PCI-PCI桥器件实现4路10/100 Mb/s自适应网口,重点介绍PCI总线桥的设计要点。该扩展

2010-07-10 15:58:28 28

28 美国半导体供应商AMCC近日与北京寰龙技术有限公司(UD Tech)宣布了一项战略合作,后者将为AMCC的PowerPC嵌入式处理器及相关产品方案提供低成本的评估包

2006-03-13 13:03:43 663

663 PowerPC处理器

二十世纪九十年代,IBM(国际商用机器公司)、

2007-06-09 14:07:54 1233

1233 随着现代军事通信技术的进步,数字化短波电台逐步往嵌入式、模块化的方向发展。CPCI总线作为一种新兴的总线技术,在短波电台的模块化设计上具有重要的应用价值,可以较大

2009-02-17 10:42:16 1358

1358

什么是CPCI

Compact PCI是标准PCI总线的工业版本,采用了抗震的Eurocard封装。插孔连接器被设计成从正面装进机架安装系统。由PICMG指导的

2009-06-13 23:39:28 11783

11783 基于CPCI总线10/100 Mb/s以太网卡的设计与实现

0 引 言 基于PCI总线的以太网控制器是现在以致将来网络应用方面的一个主要发展方向。8位ISA网卡目前已

2009-11-11 16:42:25 1161

1161

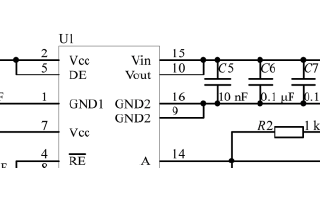

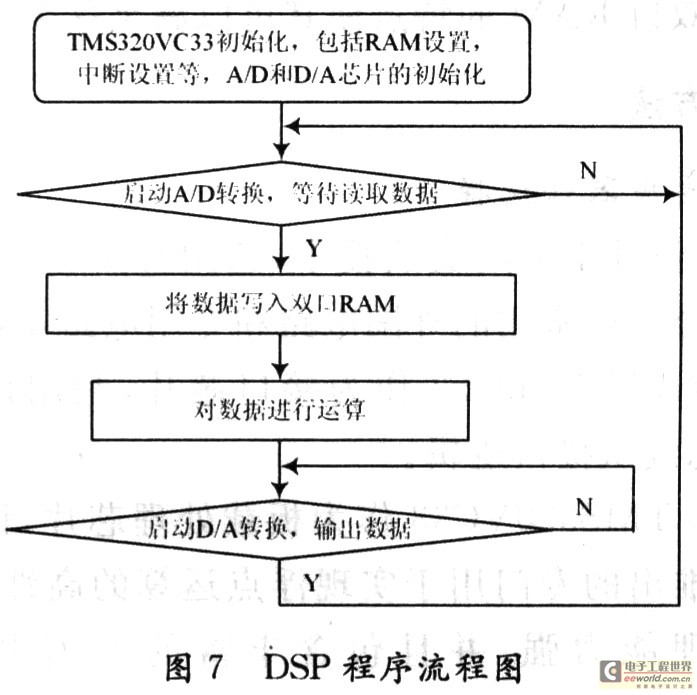

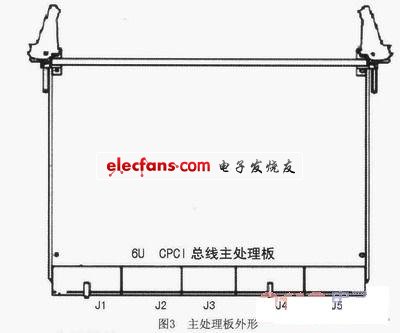

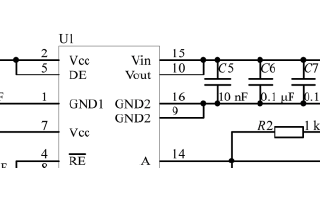

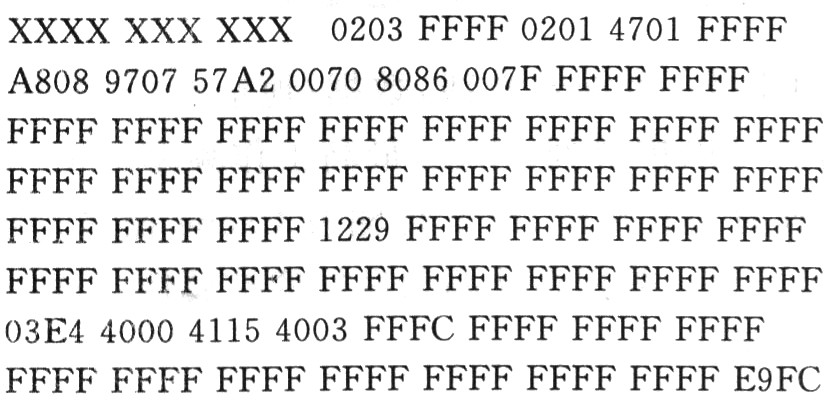

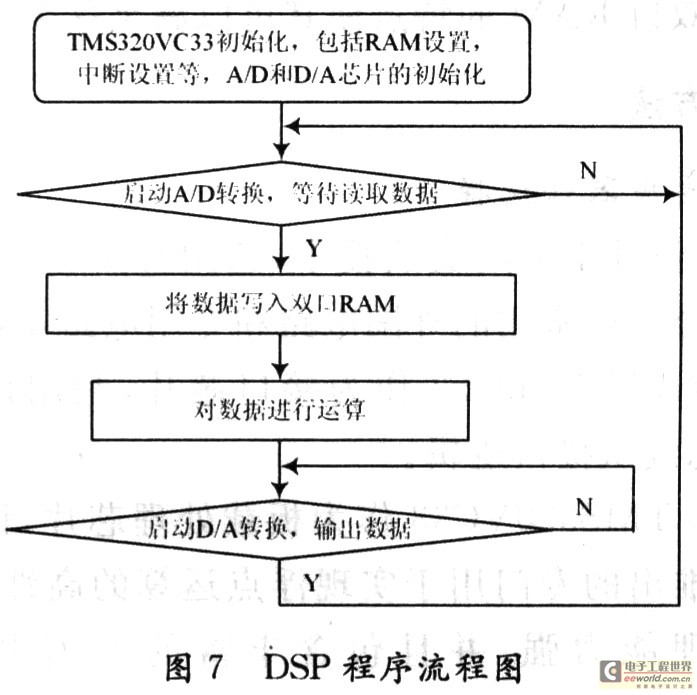

基于CPCI总线的智能A/D,D/A模块设计

0 引 言

在工业控制领域,为了实现采集和控制功能,经常会使用到A/D,D/A模块。在实际使用中A/D,D/A

2009-11-27 09:35:51 845

845

基于CPCI总线的通用FPGA信号处理板的设计

随着雷达信号处理技术的不断发展以及现代国防对雷达技术的需求,系统对雷达信号处理的要求也越来越高,需要实时处

2009-11-28 15:07:38 922

922

PowerPC家族新贵 IBM推高性能嵌入式CPU

导语:PowerPC是一种精简指令集(RISC)架构的CPU,其基本的设计源自IBMPowerPC601微处理器POWER架构。被命名为PowerPC476FP的新款处理器

2009-12-14 09:20:45 916

916 PowerPC处理器

二十世纪九十年代,IBM(国际商用机器公司)

2009-12-17 10:22:43 547

547 什么是PowerPC

PowerPC 体系结构规范(PowerPC Architecture Specification)发布于 1993 年,它是一个 64 位规范 ( 也包含 32 位子集 )。几乎所有常规可用的 PowerPC(除

2010-01-12 15:53:26 2248

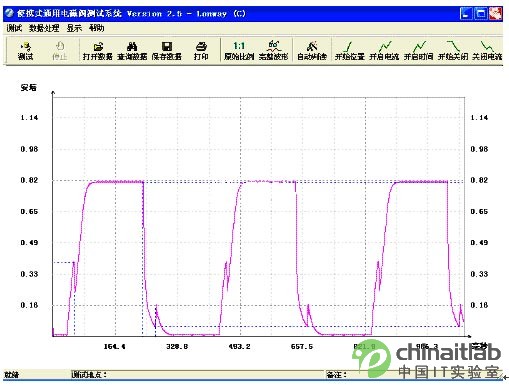

2248 基于CPCI总线的便携式电磁阀测试设备设计

1. 前言

由于某型号电磁阀热真空试验需要出厂完成,在试验过程中需测试阀门响应特性,传统的测试设

2010-01-15 10:40:48 979

979

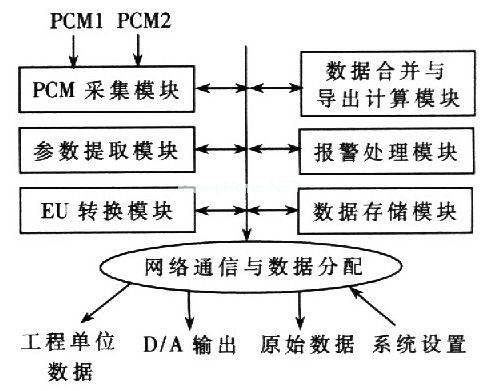

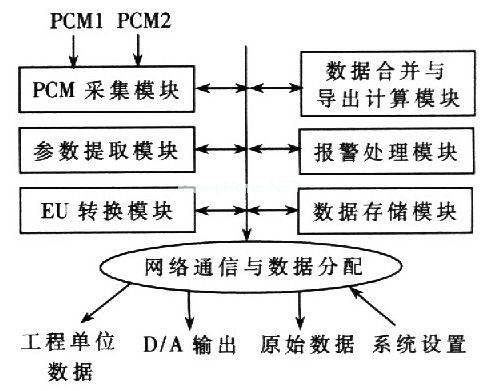

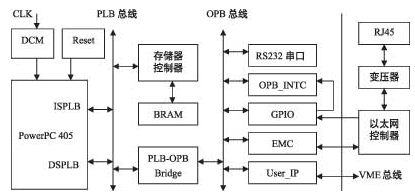

基于cPCI总线的嵌入式遥测前端处理器系统设计

遥测数据处理系统在航空、航天等军工试验领域有着广泛的应用。在航空飞行试验中.遥测数据处理系统为各类试飞测

2010-01-25 09:21:13 751

751

PowerPC,PowerPC是什么意思

Motorola公司将PowerPC内核设计到SOC芯片之中,形成了Power QUICC(Quad Integrated Communications Controller), Power QUICC II和Power

2010-03-26 10:55:27 1921

1921 Compact PCI(简称CPCI)总线是“PCI总线工业计算机制造商组织”推出的一种工业计算机总线标准,近年来应用发展最为迅速。它由PC机上的通用总线PCI发展而来,既有PC

2010-07-21 09:11:40 4981

4981

以太网(Ethernet)作为应用最广泛的局域网技术异军突起,已经迅速走向工业自动化控制领域的前台。CPCI总线系统插槽有限,设计基于CPCI总线的多网口卡可节省空间,又可以满

2010-09-10 09:56:34 1601

1601

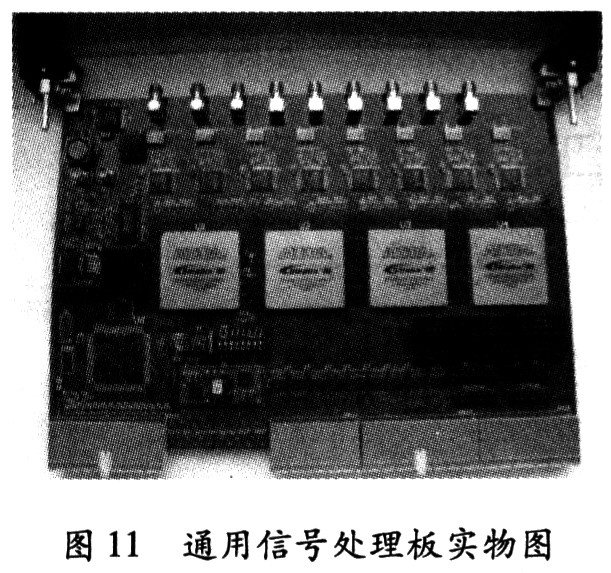

摘要:针对现代雷达信号处理,介绍了CPCI总线信号处理模块与主机间的通信方法,分析了Win2000下WDM驱动程序的开发。借助Win2000操作系统,灵活组建了多板卡通用信号处理平台,可以满足不同信号处理任务需求。 关键词:信号处理 WDMC PCI 并行处理

2011-02-27 22:42:08 70

70 本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。

2011-07-16 09:56:33 2027

2027

本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。

2011-07-17 10:47:57 12055

12055

本文利用TMS320C6416T内部集成的32位、33MHz PCI主/从接口,给出了6U的CPCI信号处理板卡设计方案,并对其软件设计特别是DSP的二次引导程序做了说明。

2011-08-25 14:07:10 2733

2733

本文在详细阐述处理板的整体结构和DSP与PCI9656的接口电路设计原理的基础上,提出一种ADSPTS201基于桥芯片PCI9656实现与CPCI总线通信的雷达信号处理板的设计方案,实现RocketIO到DSP数据的

2011-09-08 13:56:47 1970

1970

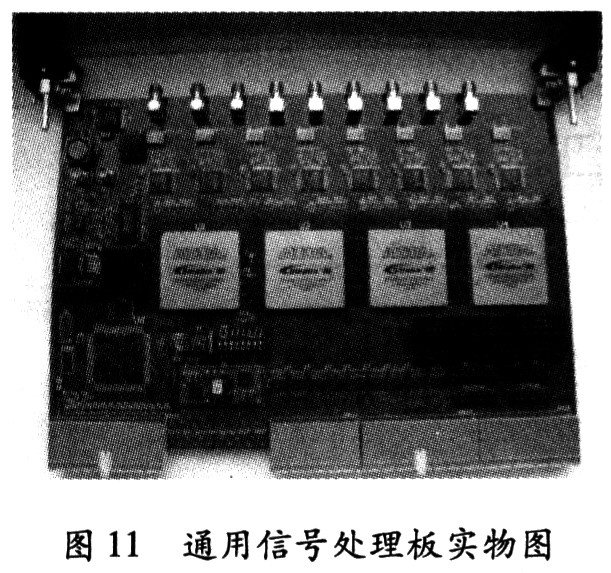

本文首先介绍了多DSP共享总线的通用信号处理板卡的硬件结构,介绍了基于PCI9054的CPCI总线接口设计和FPGA控制的通用信号处理板的板间通信过程。深入讨论了基于Windows2000系统的WDM驱动

2011-09-09 11:51:25 72

72 CPCI总线是一个开放式、国际性技术标准,由PCI总线工业计算机制造商组织PICMG(PCI Industrial Computer Manufacturer Group)负责制定和支持。CPCI总线具有严格的标准和规范,保证其具有良好的兼

2011-09-09 11:53:16 21

21 通过在FPGA中编写Verilog HDL语言控制CPCI协议转换芯片,从而实现与CPCI总线之间的高速通信。实验结果证明,该设计方案工作稳定、传输速度快、数据准确,并可扩展到其他需要通过CPCI总线的

2011-12-07 14:22:06 51

51 文中介绍一种基于CPCI总线的无源雷达终端系统,满足了无源雷达高速、大容量数据处理及传输的要求。

2012-04-20 10:59:52 45

45 本文提出了一种两级测试系统的设计思路,给出了在较宽的范围内兼容不同接口电平的脉冲信号检测系统的设计方案,采用标准CPCI总线接口设计,具有良好的兼容性和扩展性,适用于产

2013-01-04 14:29:44 3337

3337

为了满足工业控制系统多功能和数据处理能力的需求,设计了基于CPCI总线的一体化数据处理中心。系统以FPGA芯片为硬件控制核心,利用硬件描述语言Verilog进行编程,采用自顶向下和模

2013-01-08 18:19:40 28

28 随着cPCI总线技术的发展,cPCI总线逐渐代替了PCI总线、VME总线,成为测控领域中最受人们青睐的总线形式。通过分析PCI总线协议,理解高频数字电路设计方法和高速数据采集原理,本文开发了基于cPCI接口的高速数据采集系统。经过综合测试和现场应用验证表明,采集系统己达到了要求的性能指标。

2016-01-06 11:33:27 21

21 基于PowerPC的H.264编码器中断处理程序解析

2016-01-04 15:26:58 6

6 Industrial Computer Manufacturers Group,简称PICMG)于1994提出来的一种总线接口标准。是以PCI电气规范为标准的高性能工业用总线。 CPCI 规范改进自 PCI 电气规范 2.1,应用于工业和嵌入式领域。它使用工业机械组装标准,具有高性能连接技术, 可以提供一套最优化系统

2017-10-20 11:25:18 26

26 不会有太大的改变。由于先人为主的缘故,VME总线在高性能的实时工业应用领域一直处于主导地位,并且进人一个相对完善的阶段。但CPCI后来居上,由于具有开放性的架构体系和通用的操作系统等优势,CPC)总线自诞生起在PC 机、工控机和军用装备等各个领域受到广泛关注并被普遍采用。遗憾

2017-10-20 17:54:03 73

73 CPCI 总线信号到LOCAL 总线信号的转换是基于PCI9054芯片实现的。PCI9054 是PLX 公司生产的一款基于PCI2.2总线规范的通用接口芯片,是32 位、33MHZ的PCI总线

2018-07-25 11:02:00 2495

2495

二十世纪九十年代,IBM(国际商用机器公司)、Apple(苹果公司)和Motorola(摩托罗拉)公司开发PowerPC芯片成功,并制造出基于PowerPC的多处理器计算机。PowerPC架构

2018-01-26 01:22:02 2960

2960

对 PowerPC 体系结构家族树的所有分支来说,PowerPC 体系结构和应用级编程模型是通用的。 PowerPC 体系结构是一种精减指令集计算机(Reduced Instruction Set

2018-01-26 01:24:01 1783

1783

CPCI6U-2DSP-C6678 信号处理板基于 6U CPCI 规范,并且具有一个基于FMC 规范的 HPC 接口。信号处理板采用双 DSP+FPGA 的处理架构,DSP 采用 TI 公司

2019-03-19 08:00:00 17

17 PowerPC460GTx处理器基于Power Architecture标准,结合了一个性能优化的PowerPC核,带有高带宽存储器和I/O子系统,从而支持苛求的嵌入式处理器应用。

2019-06-28 11:41:26 1953

1953 总线具有严格的标准和规范,保证其具有良好的兼容性,支持多种处理器和操作系统,符合CPCI规范的扩展卡可插入任何CPCI系统并可靠地工作。

2020-04-09 10:05:34 2999

2999

本文简单介绍了CPCI 总线的基本尺寸、射频盲插的实现途径及插件插箱的结构设计要点,希望可以提供参考。

2020-07-08 16:42:40 15

15 Compact PCI(简称CPCI)总线是“PCI总线工业计算机制造商组织”推出的一种工业计算机总线标准,近年来应用发展最为迅速。它由PC机上的通用总线PCI发展而来,既有PCI总线的高带宽高性能

2021-01-20 10:32:52 2407

2407 为了提高航空航天领域对信号处理、传输的实时性及可靠性,以Cyclone III系列EP3C40F324I7为核心处理器,设计了一种基于CPCI总线的多功能通信卡。结合高效的FPGA算法,设计出一款实时性强、可靠性高的多功能通信卡。经测试使用,该多功能通信卡各项性能指标均达到要求,已投入实际应用中。

2021-04-05 08:32:00 3376

3376

设计了一种基于CPCI总线标准的PMC接口载板。载板以FPGA为核心,集成了CPCI接口模块和DPRAM(双口RAM)模块,CPCI接口模

2021-05-05 16:56:00 3055

3055

连续实时信号处理--用连续cFFT比较TigerSHARC和PowerPC

2021-05-11 08:03:42 5

5 、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。SoPC的核心是在FPGA上实现的嵌入式微处理器核,目前主要有Xilinx公司的32位软核MicroBlaze、32位PowerPC系列处理器硬核PowerPC 405,以及Altera公司的Nios系列微处理器软核等。

2021-06-17 11:40:52 2224

2224

基于CPCI总线的四通道总线通讯模块设计

2021-06-22 16:58:19 16

16 基于CPCI总线的航天器通信信号设备故障检测

2021-06-23 11:10:27 12

12 产品性能

总线结构

标准的CPCI通用总线

完全

2022-02-15 10:56:43 2

2 背板

8个槽:1个CPCI系统插槽、7个CPCI外围插槽,全部支持后IO插卡

支持66MHz

2022-02-17 11:09:25 1

1 背板

2个槽:1个CPCI系统插槽、1个CPCI外围插槽

支持66MHz PCI 总线时钟

V(I/O):+3.3V/+5V(出厂默认为3.3V)

2022-02-17 11:10:56 2

2 背板

2个槽:1个CPCI系统插槽、1个CPCI外围插槽

支持66MHz PCI 总线时钟

V(I/O):+3.3V/+5V(出厂默认为3.3V)

2022-02-17 11:11:26 0

0 背板

4个槽:1个CPCI系统插槽、3个CPCI外围插槽

支持66MHz PCI 总线时钟

V(I/O):+3.3V/+5V(出厂默认为3.3V)

2022-02-17 11:11:56 2

2 背板

1个CPCI系统插槽、3个CPCI外围插槽,所有槽均支持后IO插卡

支持66MHz

2022-02-17 11:12:26 2

2 背板

1个CPCI系统插槽、3个CPCI外围插槽,所有槽均支持后IO插卡

支持66MHz

2022-02-17 11:12:57 0

0 背板

6个槽:1个CPCI系统插槽、5个CPCI外围插槽

支持66MHz PCI 总线时钟

V(I/O):+3.3V/+5V(出厂默认为3.3V)

2022-02-17 11:13:28 1

1 背板

6个槽:1个CPCI系统插槽、5个CPCI外围插槽

支持66MHz PCI 总线时钟

V(I/O):+3.3V/+5V(出厂默认为3.3V)

2022-02-17 11:13:58 0

0 背板

1个CPCI系统插槽、3个CPCI外围插槽,所有槽均支持后IO插卡

支持66MHz PCI 总线时钟

2022-02-17 11:15:29 2

2 产品主要特点

符合CPCI总线标准规范

国产加固机架式CPCI测控平台

标准19寸机架式安装

CPCI模块信号后出线设计

内置厚物科技CPCI-9333或CPCI-9363控制器

内置

2022-04-26 15:07:08 468

468

电子发烧友网站提供《基于CPCI总线CPU主控模块的设计与实现.pdf》资料免费下载

2023-10-18 11:09:18 0

0 产品概述 键石 CPCI6320 是一款高品质的视频播放板,该板基于 CPCI 总线,采用 Sigma Designs 公司的 EM8470 流处理器,支持多种音视频格式,兼容即插即用(PNP)。 在安装和使用键石 CPCI6320 型视频播放板前,建议您先阅读本手册,以便了解如何安装和使用该产品。

2023-12-11 14:40:51 0

0

电子发烧友App

电子发烧友App

评论